نام پروژه : طراحی میکروکنترلر نمونه به زبان verilog و شبیه سازی آن در نرم افزار ModelSim

ویژگی های پروژه :

زبان طراحی سخت افزار Verilog HDL

قابل پیاده سازی روی انواع FPGA

محتویات پروژه :

– گزارش انجام مرحله به مرحله پروژه به زبان انگلیسی

– گزارش کلی انجام پروژه به زبان فارسی

– گزارش فارسی شبیه سازی پروژه در ModelSim 10.1 SE

– به همراه سورس انجام پروژه

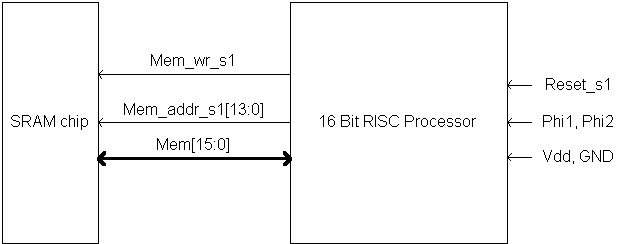

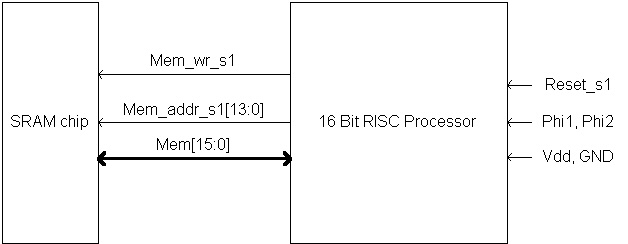

مشخصات میکروکنترلر طراحی شده :

– ۱۶ بیتی و دارای معماری RISC

– ۱۶ دستورالعمل برای CPU

– ۱۶ رجیستر همه منظوره داخل CPU

– دارای حافظه داده و حافظه برنامه از جنس SRAM

بلوک دیاگرام کلی میکروکنترلر طراحی شده :

توضیحات انجام پروژه :

برای طراحی میکروکنترلر فوق ابتدا معماری آن مورد بررسی قرار می گیرد و دستورالعمل های CPU تعریف می شود . این میکروکنترلر قابلیت انجام ۱۶ دستورالعمل مختلف را دارد که هر دستور العمل ۱۶ بیتی تعریف شده است . سپس نحوه انجام کار میکروکنترلر مورد بررسی قرار گرفته و نمودار ماشین حالت (FSM) برای آن رسم می گردد . این میکروکنترلر در ۶ مرحله عملیات Fetch ، Decode ، Execute ، Memory Write Back را انجام میدهد . بعد از مشخص شدن کلیت طراحی میکروکنترلر به برنامه نویسی سخت افزار میکروکنترلر به زبان Verilog HDL پرداخته می شود و طراحی میکروکنترلر به صورت ماژولار صورت می گیرد و در نهایت ماژول های مختلف در یک ماژول به هم متصل می گردند . در هر مرحله برای صحت درستی کدها ، شبیه سازی در ModelSim انجام گرفته است . این میکروکنترلر از ۷ ماژول مختلف به صورت زیر تشکیل شده است :

- ماژول تولید کلاک کاری میکرو ( phi1 و phi2 )

- ماژول واحد محاسبه و منطق میکرو ( ALU )

- ماژول اضافه کردن علامت ( Sign Extend )

- ماژول رجیستر بانک ( Register bank )

- ماژول دیتای میکرو ( Data path )

- ماژول واحد کنترل میکرو ( Control Unit )

- ماژول کلی سیستم میکرو ( System )

قیمت : ۱۰,۰۰۰ تومان

1 دیدگاه

سلام… الگوریتم طراحی pipeline یا multi cycle؟؟؟؟