مقدمه

طراحان سخت افزار های الکترونیکی ، رفتار و ساختار یک مجموعه ی دیجیتال را با استفاده از زبان های HDL ( مخفف Hardware Description Language ) توصیف می کنند . زبان های توصیف سخت افزار در حال حاضر شامل سه نوع زبان متفاوت VHDL ، Verilog و System Verilog هستند . این زبان های توصیف سخت افزار با زبان های برنامه نویسی نرم افزاری تفاوت دارند زیرا در آنها از ارتباطات سیگنالی و زمان انتشار سیگنال ها سخن به میان است . در هر یک از سه زبان HDL گفته شده سبک توصیف سخت افزار منحصر به خود را دارند . در زبان VHDL و Verilog پیاده سازی در سطح رجیستری است ( Register Transfer Level ) که یک سطح بالاتر از سطح گیت ( Gate Level ) است . اما زبان SystemVerilog در ادامه مسیر تکامل پیاده سازی سخت افزاری از سطح بالاتری از طراحی سیستم های دیجیتال پشتیبانی می کند که در آن در کنار استفاده از نسخه بهبود یافته Verilog ، برنامه نویسی شی گرا ( Object Oriented ) نیز اضافه شده است .

ویژگی های VHDL در مقابل Verilog

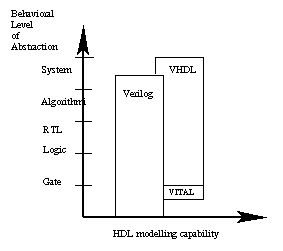

VHDL که مخفف Very High Speed Integrated Circuit Hardware Description Language است از نظر Syntax غنی تر از Verilog است و توانایی مدلسازی سختافزار در بالاترین سطوح انتزاع (تا سطح سیستم) را دارد در حالی که Verilog بیشتر به زبان C شبیه است و از توصیف سخت افزار در سطوح پایین تر طراحی ( سطح گیت ) نیز پشتیبانی می کند . شکل زیر نشاندهنده میزان مقیاس پذیری این دو زبان در سطوح مختلف انتزاع در توصیف رفتاری میباشد .

در زبان VHDL سطح سیستم قابلیتی را ایجاد می کند تا توابع و پروسه ها بتواند در قالب یک پکیج بسته یا Core با Core های دیگر به صورت جداگانه ترکیب شود . یعنی از به هم پیوستن Core های کوچکتر Core های بزرگتر ساخته می شود. اما در Verilog هیچ مفهوم بسته ای وجود ندارد و کلیه توابع و پروسه ها باید در قالب یک ماژول تعریف شود که این ماژول در قالب هدر فایل به برنامه افزوده می شود .

انواع داده در زبان Verilog نسبت به VHDL ساده تر و استفاده از آنها آسانتر میباشد، ضمن اینکه این انواع داده در Verilog به مدلسازی ساختاری نزدیکتر هستند، در این زبان برخلاف VHDL انواع داده مشخصی تعریف شده است و کاربر نمیتواند انواع داده جدید به آن اضافه کند.

برای فردی که پیشزمینهای در مورد زبانهای برنامه نویسی ندارد، یادگیری زبان Verilogسادهتر از VHDL است، چرا که نوشتن کدهای VHDL کمی پیچیده تر از Verilogمیباشد و Verilog تقریبا ۵۰ درصد به زبان C شبیه است .

نمونه یک کد VHDL

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 |

reg1: process (rst, cllk) begin if rst = '1' then q_reg <= (others => '0'); q_i <= (others => '0'); elsif rising_edge(clk) then if s_l = '1' then q_i(0) <= q_i(7); loop1: for i in 6 downto 0 loop q_i(i + 1) <= q_i(i); end loop loop1; q_reg <= y; else q_i <= q_reg; q_reg <= y; end if; end if; end process reg1; |

نمونه یک کد Verilog

|

1 2 3 4 5 6 7 8 9 10 11 12 13 |

always @(posedge CLK or posedge RST) begin if (RST) begin q_reg = 0; Q = 0; end else if (S_L) begin Q[7:0] = {Q[6:0],Q[7]}; q_reg = Y; end else begin Q = q_reg; q_reg = Y; end end |

در صورتی که این مطلب مورد پسندتان واقع شد لایک و اشتراک گذاری فراموش نشود

دیدگاه (6)

ضمن عرض سلام ، ادب و احترام

واقعا خدا قوت مهندس عزیز بخاطر سایت عالی و به روز و مفیدتون

خدمتون عرض کنم اگه اشتباه نکنم VHDL مخفف Very(high speed)HDL باشه

سلام دوست عزیز سپاسگزارم بله حق با شماست اصلاح می کنم تشکر

سلام آیا اسلاید هایی که از دانشگاه شاهد در سایت قرار داده شده اجازش گرفته شده ؟استفاده ازش مشکلی نداره؟

سلام دوست عزیز اسلایدهای درسی هستش و استفاده از اون مشکلی نداره

بُرد های تلفن همراه

با کدوم زبان برنامه نویسی شدن

و هم چنین باکس

سلام متشکر بابت اموزش های بسیار خوبتون مهندس من از سال ۹۴ با سایت و گروه تلگرامتون داشتم پیش میرفتم و اون زمان توضمینه avr خیلی منو کمک کردین مسئله ای ک هست اینه ک من تقریبا الان میخوام fpgaشروع کنم بنظر شما من ک اشنایی با این زبان رو ندارم و تصمیم گرفتم تا سطح بالا این زبان اموزش ببینم بنظر شما بهتره با vhdlشروع کنم ؟یا نه

و اگه شما کتاب خوبی هم مطالعه کردین ممنون میشم به من هم معرفی کنید تا تهیه کنم و استارتو بزنم