لینک های دسترسی به بخش های قبلی دوره آموزش FPGA :

شروع دوره های آموزش مجازی FPGA

بخش اول آموزش FPGA : آشنایی با اصول الکترونیک دیجیتال

مقدمه

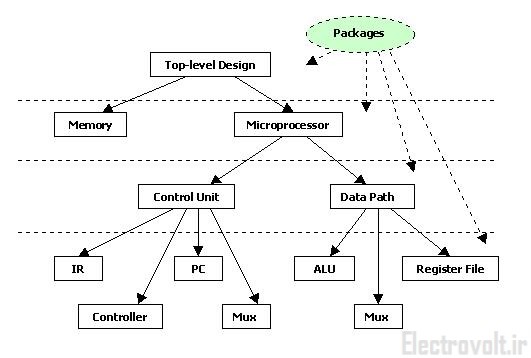

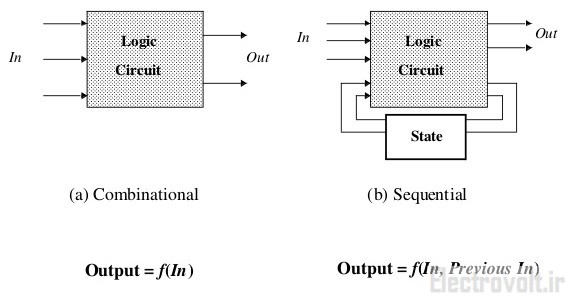

در بخش قبلی با انواع گیت های منطقی آشنا شدیم و گفتیم که با استفاده از این گیت ها میتوان مدارهای ترکیبی ( Combinational ) و ترتیبی ( Sequentional ) ساخت. در این بخش انواع این مدارها را با هم بررسی می کنیم. یادگیری اصولی که در این بخش بیان می شود باعث بوجود آمدن دیدگاه اولیه برای طراحی یک سیستم دیجیتال می گردد. کلیه این مدارها مستقیما روی FPGA ها قابل پیاده سازی هستند. ویژگی دیگری که طراحی مدارهای دیجیتال دارند این است که از گیت های پایه شروع شده و با ترکیب آن ها مدارهای بزرگ و بزرگتری تشکیل می شود. اگر از کوچک ترین جزء سیستم طراحی را آغاز کنیم و به تدریج آن را رو به بالا تا نهایی شدن سیستم ادامه دهیم ، به آن طراحی از پایین به بالا ( Bottom-Up ) گویند. اما اگر طراحی را از بزرگترین جزء سیستم شروع کنیم و سپس رو به پایین دیگر اجزای سیستم را تشریح کنیم ، به آن طراحی از بالا به پایین ( Top-Down ) گفته می شود.

منطق سه حالته مدارهای دیجیتال

همه مدارهای منطقی در مبنای 2 هستند. یعنی دارای دو منطق ولتاژی هستند. منطق 0 ( ولتاژ Low ) و منطق 1 ( ولتاژ High )

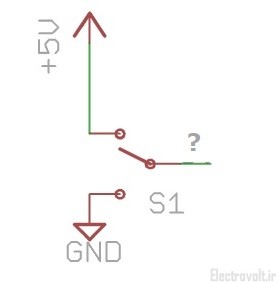

اما در حقیقت یک منطق ولتاژی دیگر نیز در الکترونیک دیجیتال وجود دارد و آن منطق مدار باز ( Open Circuit یا Float یا High Z ) است. با فرض این منطق به صورت یک منطق جداگانه ، مدارهای الکترونیکی دیجیتال سه حالته ( three state ) می شود. برای درک بیشتر این منطق ، کلید زیر را در نظر بگیرید.

زمانی که کلید به بالا وصل شود، منطق High به خروجی منتقل می شود. زمانی که کلید به پایین وصل شود، منطق Low به خروجی منتقل می شود. اما اگر کلید وسط باشد ( به هیچ جا وصل نباشد ) خروجی چه منطقی دارد ؟ در این حالت میگوییم خروجی مدارباز است. نام های دیگر این منطق Float ( شناور ) یا high impedance ( مقاومت بالا ) است. علت نامگذاری Float به خاطر خاصیت شناور بودن این منطق است یعنی زمانی که یک سیم مدار باز است منطق دقیقی ندارد با کوچکترین تحریکی تغییر حالت می دهد و هر لحظه ممکن است منطق 0 یا 1 شود. علت نامگذاری high impedance نیز به خاطر این است که اگر یک مقاومت با مقدار زیاد را در مدار قرار دهیم ، به علت افت ولتاژ زیاد بین دو سر مقاومت هیچ جریانی از آن عبور نکرده و دقیقا عین حالت مدارباز عمل می کند.

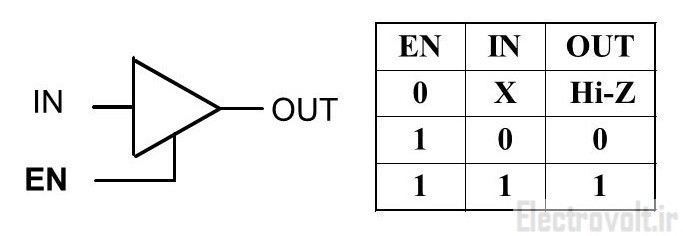

یکی از گیت های پرکاربردی که دارای منطق سه حالته می باشد ، گیت بافر سه حالته است. در این نوع بافر دو ورودی داریم. یک ورودی اصلی و یک ورودی فعالساز ( Enable ). شکل زیر نماد مداری این بافر و جدول درستی آن را نشان می دهد.

همانطور که در شکل فوق مشاهده می کنید زمانی که پایه فعالساز دارای منطق 0 باشد ، خروجی مدار باز یا همان High Z می شود و زمانی که پایه فعالساز دارای منطق 1 باشد ، خروجی همان ورودی X است ( X خود منطق 0 یا 1 دارد ).

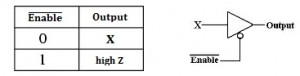

مدل دیگری از گیت بافر سه حالته وجود دارد که در شکل زیر آن را مشاهده می کنید.

همانطور که در شکل فوق مشاهده می کنید زمانی که پایه فعالساز دارای منطق 0 باشد ، خروجی همان ورودی X است ( X خود منطق 0 یا 1 دارد ) و زمانی که پایه فعالساز دارای منطق 1 باشد ، خروجی مدار باز یا همان High Z می شود.

تنها تفاوتی که در این دو مدل از گیت بافر سه حالته مشاهده می شود ، مربوط به پایه فعالساز ( Enable ) است. در شکل اول با 1 شدن این پایه ، بافر فعال ( Active ) می شود و در شکل دوم با 0 شدن این پایه ، بافر فعال می شود. در اصطلاح طراحی منطقی به پایه هایی نظیر شکل اول Active High ( فعال شدن با منطق High ) و به پایه هایی نظیر شکل دوم Active Low ( فعال شدن با منطق Low ) گفته می شود.

کاربرد بافرها در مدار به خاطر :

- منطقی کردن سطح ولتاژ : در مدارهای دیجیتال ممکن است با افت ولتاژ یا افزایش ولتاژ مواجه شویم که این مسئله باعث تغییر منطق ولتاژ از ۱ به ۰ یا بالعکس می شود. برای جلوگیری از تغییرات ناخواسته ولتاژی که باعث افت عملکرد مدار می شود از گیت بافر استفاده می شود.

- تقویت جریان در خروجی : استفاده از گیت بافر باعث تقویت جریان در خروجی این گیت می شود بدین معنی که می توان به خروجی بار بزرگتری متصل کرد بدون اینکه افت ولتاژ داشته باشیم .

- ایزوله سازی مدار : یکی از استفاده های دیگر گیت بافر در حالت مدار باز ( High Z ) می باشد بدین معنی که مدار سمت راست گیت بافر از مدار سمت چپ آن به کلی جدا می گردد .

آشنایی با انواع مدارهای ترکیبی (آسنکرون)

ویژگی مهم مدارهای ترکیبی دیجیتال که با استفاده از گیت های منطقی استاندارد ساخته می شوند ، آنی بودن آن ها است. یعنی به محض اینکه به این مدارها ورودی بدهیم ، خروجی آماده می گردد. در مدارهای ترکیبی تاخیری که بین تغییر در ورودی و تغییر در خروجی وجود دارد بسیار کم و در حد نانو ثانیه می باشد.

A ) جمع کننده ( Adder )

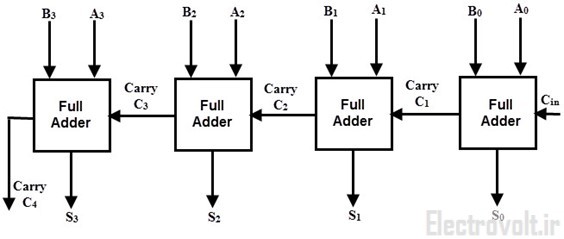

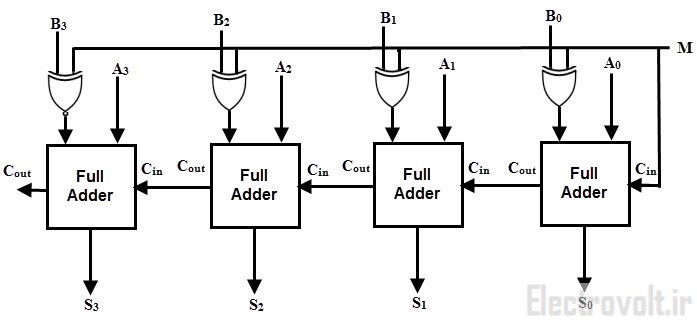

جمع کننده مداری دیجیتالی است که می تواند دو عدد را با هم جمع کند. عملیات جمع ( ADD ) یکی از پرکاربردترین عملیات ها می باشد ( S=A+B ). هر گاه دو عدد n بیتی را با یکدیگر جمع کنیم جواب حداکثر n+1 بیت خواهد شد. شکل زیر یک جمع کننده 4 بیتی را نشان می دهد.

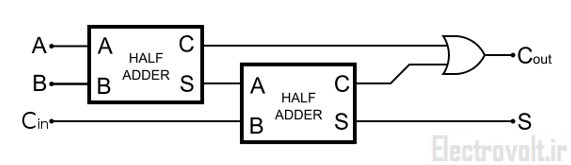

همانطور که در شکل فوق مشاهده می کنید ، جمع کننده 4 بیتی از 4 تمام جمع کننده ( Full Adder ) تشکیل شده است. C4 همان بیت آخر حاصل جمع یعنی S5 است که نشان دهنده این موضوع است که حاصل جمع دو عدد 4 بیتی ، 5 بیت می شود. مداری که سه رقم دودویی ( سه بیت ) را جمع کند (جمع دو رقم دودویی و یک رقم نقلی حاصل از ستون قبلی)، تمام جمع کننده نامیده می شود. هر Full Adder از دو نیم جمع کننده ( Half Adder ) تشکیل می شود. مدار ترکیبی که دو رقم دودویی ( دو بیت ) را با هم جمع می کند ، نیم جمع کننده می نامند. شکل زیر این موضوع را نشان می دهد :

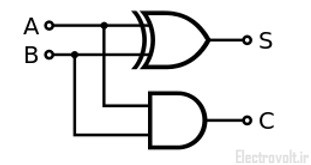

هر Half Adder مداری به صورت شکل زیر دارد :

B ) تفریق کننده ( Subtractor )

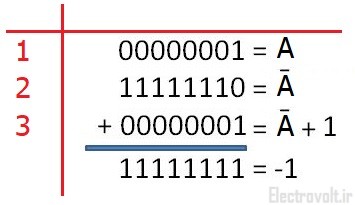

تفریق کننده نیز عملکردی مشابه با جمع کننده دارد با این تفاوت که عدد اول با علامت مثبت و عدد دوم با علامت منفی وارد جمع کننده می شود ( C=A-B ). حاصل تفریق دو عدد n بیتی نیز حداکثر n+1 بیت می شود. برای منفی کردن یک عدد کافی است مکمل دو عدد را محاسبه نماییم. مکمل دو ( two’s complement ) هر عدد برابر است با معکوس تک تک بیت های آن عدد و جمع شدن عدد نهایی با 1 که در شکل زیر یک مثال را مشاهده می کنید.

نکته : اگر تک تک بیت های یک عدد را به عنوان ورودی اول با منطق 1 به عنوان ورودی دوم Xor کنیم ، نتیجه آن مکمل دو آن عدد بدست می آید.

با استفاده از نکته فوق میتوان مداری ساخت که عملیات جمع و تفریق را به صورت همزمان انجام دهد. این مدار را در شکل زیر مشاهده می کنید.

در مدار فوق اگر ورودی M برابر 1 باشد ، عملیات A-B و در صورتی که M برابر 0 باشد ، عملیات A+B انجام می شود.

C ) ضرب کننده ( multiplier )

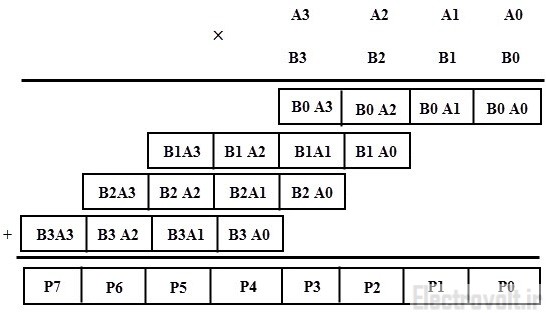

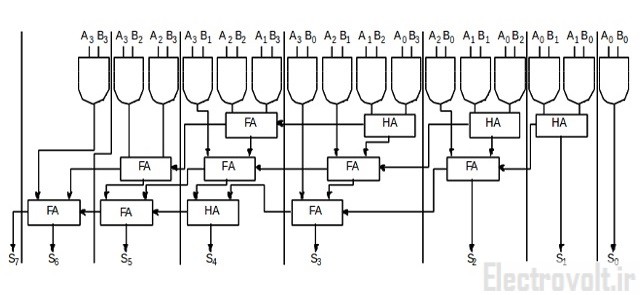

ضرب یکی دیگر از عملیات هایی است که با مدارهای منطقی ساخته می شود. اگر دو عدد n بیتی را با هم ضرب کنیم حاصل 2n بیت خواهد بود و در حالت کلی تر اگر یک عدد n بیتی را در یک عدد m بیتی ضرب نماییم حاصل n+m بیت خواهد بود. در طراحی یک ضرب کننده دیجیتال از جمع کننده و گیت And استفاده می شود. برای مثال ضرب دو عدد چهار بیتی A و B را در نظر بگیرید. شکل زیر ضرب این دو عدد و نتیجه آن را در مبنای دو نشان می دهد.

همانطور که مشاهده می کنید بعد از And شدن دو به دوی بیت ها ، در برخی از خروجی ها Half-Adder و در برخی Full-Adder استفاده می گردد. مدار کامل این ضرب کننده در شکل زیر نشان داده شده است.

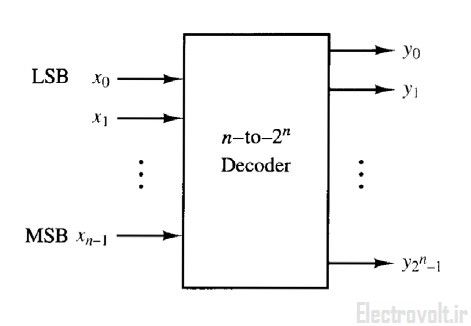

D ) دیکودر یا کدگشا ( decoder )

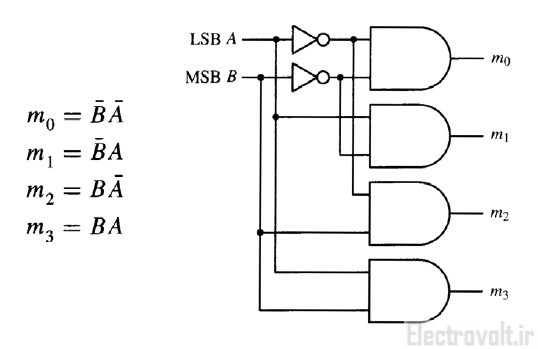

دیکودر یک مدار ترکیبی است که دارای n بیت ورودی ( از 0 تا n-1 ) و 2 به توان n بیت خروجی ( از 0 تا 2n-1 ) دیجیتال می باشد. بر اساس کد باینری که در ورودی دیکودر قرار می گیرد ، تنها یکی از 2 به توان n خروجی آن فعال می شود. شکل زیر یک دیکودر را نشان می دهد.

درون دیکودر از گیت های Not و And استفاده می شود. برای مثال در شکل زیر یک دیکودر 2 به 4 را مشاهده می کنید.

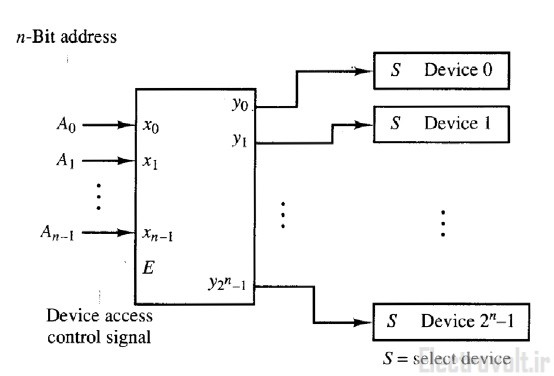

از کاربردهای دیکودر میتوان به آدرس دهی حافظه به منظور فعال/غیرفعال سازی مکانی از حافظه اشاره کرد. برای مثال در یک حافظه 4 کیلوبایتی میتوان با 12 بیت تمام خانه های آن را آدرس دهی کرد به طوری که فقط یکی از آن ها انتخاب می گردد. شکل زیر این موضوع را نشان می دهد.

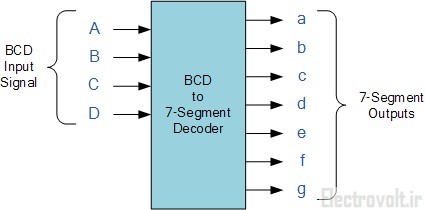

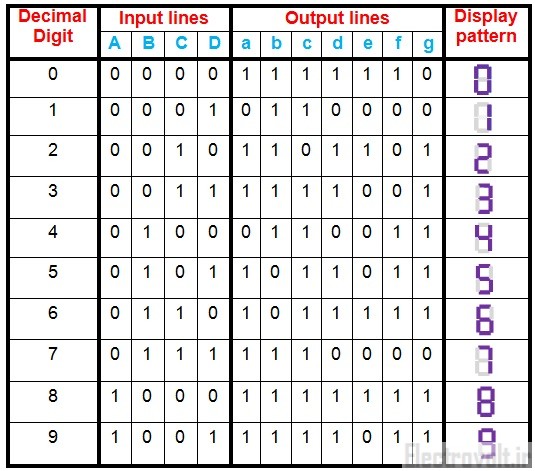

از آی سی ها دیکودرهای معروف میتوان آی سی های 7447 و 7448 را نام برد. این آی سی ها دیکودر باینری به کدهای سون سگمنت هستند که دارای 4 ورودی باینری و 7 خروجی مخصوص سون سگمنت می باشند. آی سی 7447 برای سون سگمنت های آند مشترک و آی سی 7448 برای سون سگمنت های کاتد مشترک می باشند.

از آی سی ها دیکودرهای معروف میتوان آی سی های 7447 و 7448 را نام برد. این آی سی ها دیکودر باینری به کدهای سون سگمنت هستند که دارای 4 ورودی باینری و 7 خروجی مخصوص سون سگمنت می باشند. آی سی 7447 برای سون سگمنت های آند مشترک و آی سی 7448 برای سون سگمنت های کاتد مشترک می باشند.

شکل زیر جدول درستی آی سی 7448 را نشان می دهد.

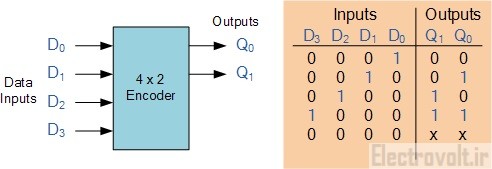

E ) انکودر یا کدگذار ( encoder )

یک مدار ترکیبی با ۲n ورودی و n خروجی می باشد. در کدگذار در صورتی که یکی از پایه های ورودی را فعال کنیم در خروجی کد باینری معادل آن تولید می شود. یعنی انکدر دقیقا عکس دیکدر عمل می کند.

مثال : انکدر ۴ به ۲

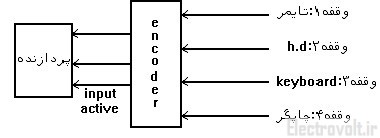

دسته ای از انکودر ها دارای اولویت هستند که به آن Priority Encoder گفته می شود. در این انکودرها ورودی های LSB اولویت بیشتری دارند. از کاربردهای این انکودرهای دارای اولویت می توان دریافتن آدرس وقفه های مختلفی که به پردازنده ای فرستاده می شود اشاره کرد. در این کاربرد دیگر نیاز نیست که برای هر وسیله که وقفه نیاز دارد ، خطوط جداگانه ای برای آدرس ایجاد کرد یعنی ۲n وسیله را با n خط و با یک کد گذار می توان آدرس دهی کرد.

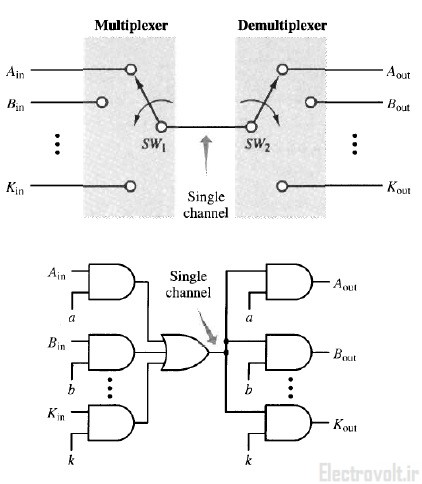

F ) مالتی پلکسر ( Multiplexer ) و دی مالتی پلکسر ( Demultiplexer )

مالتی پلکسر یک مدار ترکیبی است که دارای 2 به توان n ورودی دیتا ، n بیت انتخاب دیتا و ۱ بیت خروجی می باشد. یک مالتی پلکسر توسط n بیت انتخاب دیتا 2 به توان n بیت ورودی را کنترل می کند که کدام یک از آنها به خروجی وصل باشد. پس در واقع مالتی پلکسر همانند سوئیچی عمل می کند که از بین تعدادی ورودی یکی از آنها انتخاب و به خروجی متصل می کند.

دی مالتی پلکسر دارای ۱ ورودی و 2 به توان n خروجی و n بیت انتخاب است. دی مالتی پلکسر دقیقا عکس مالتی پلکسر عمل می کند یعنی انتخاب می کند که یک خط دیتای وارد شده به کدام خروجی وصل شود. دیگر خروجی ها صفر هستند.

نکته : اگر به تنها ورودی دی مالتی پلکسر ، منطق 1 بدهیم ، تبدیل به یک دیکودر می گردد که n بیت ورودی و 2 به توان n بیت خروجی دارد.

آشنایی با مدارات ترتیبی (سنکرون)

علت استفاده از مدارهای ترتیبی ، وجود نقص در مدارهای ترکیبی بزرگ بود. گفتیم که تاخیر برای یک مدار ترکیبی ناچیز و در حد نانو ثانیه است اما در مدارهایی که از قرار گرفتن هزاران مدار ترکیبی مختلف پشت سر هم تشکیل می گردد ، این تاخیر به میکرو و میلی ثانیه می رسد و دیگر ناچیز نمی باشد. ضمن اینکه مقدار دقیق این تاخیر برای مدارهای مختلف متفاوت بوده و نمیتوان کنترلی روی زمان دقیق اجرای عملیات ها داشت.در مدارهای ترتیبی این مشکل با حافظه دار شدن و وجود سیگنال کنترل کننده ای به نام کلاک حل شده است.

در مدارهای ترکیبی به محض تغییر ورودی ، خروجی نیز تغییر می کند و همچنین خروجی فعلی تنها به ورودی فعلی بستگی دارد. اما دسته ای دیگر از مدارها هستند که برای آنها پیش بینی مقادیر خروجی ها با دانستن ورودی های فعلی همیشه امکان پذیر نیست. به عبارت دیگر خروجی اینگونه مدارها می توانند علاوه بر ورودی های فعلی به ورودی های قبلی مدار نیز وابسته باشند. مدارهایی را که اینگونه عمل می کنند مدارهای ترتیبی می نامند. مدارات ترتیبی را مدارات باحافظه هم می گویند . بنابراین در مدارهای ترتیبی، خروجی نه تنها به ورودی فعلی بلکه به ورودیهای قبلی هم بستگی دارد و قادرند اطلاعات را در خود ذخیره کنند.شکل زیر این موضوع را نشان می دهد.

مفهوم ترتیبی تنها به سیستم های دیجیتال اختصاص ندارد. مثلا عملکرد یک آسانسور را در نظر بگیرید. آسانسور مانند یک وسیله ترتیبی عمل می کند زیرا کار آن توسط سیگنال های ورودی از پنل آسانسور ( پنل داخل آسانسور و پنل موجود در هر طبقه ) و مکان فعلی اش در طبقات معین می گردد. شکل زیر دسته بندی انواع مدارهای منطقی ترتیبی را نشان می دهد.

Bistable : به معنای دو حالته می باشد. مدارهایی که در این دسته قرار می گیرند دارای دو حالت پایدار هستند.

Monostable : به معنای تک حالته می باشد. مدارهایی که در این دسته قرار می گیرند ، تنها یک حالت پایدار می تواند داشته باشد.

Astable : به معنای ناپایدار می باشد. مدارهایی که در این دسته قرار دارند بین دو حالت پایدار در حال نوسان هستند.

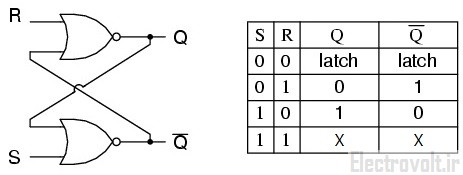

بیشترین کاربرد را دسته Bistable دارند نظیر انواع حافظه ها که دو حالت پایدار 0 یا 1 دارند. دو نمونه از حافظه ها که در مدارهای دیجیتال به کار می روند ، لچ ( Latch ) ها و فلیپ فلاپ ( Flip-Flop ) ها هستند. لچ یک عنصر حافظه می باشد که در آن سیگنال های ورودی حالت مدار را کنترل می کنند. شکل زیر یک Set/Reset Latch را نشان می دهد.

همانطور که مشاهده می کنید اگر لچ دارای ورودی باشد که خروجی مدار ( یعنی Q ) را به منطق 1 ببرد ، به آن نشاندن ( Set ) و اگر خروجی مدار را به منطق 0 ببرد ، به آن بازنشاندن ( Reset ) می گوییم. حالتی که هر دو ورودی 0 باشد ، هر حالت قبلی که مدار داشته باشد حفظ می شود. حالتی که هر دو ورودی 1 شود به خاطر ناپایدار شدن مدار تعریف نشده می باشد.

لچ ها که با گیت NOR ساخته شده اند جزو اولین مدارهایی هستند که دارای فیدبک ( Feedback ) می باشند. فیدبک اتصالی است که خروجی را به نحوی به ورودی مرتبط می سازد. کاربرد لچ در مدارهایی است که سیگنال کلاک ( Clock ) ندارند. بنابراین در لچ به محض تحریک در ورودی به آن پاسخ می دهد. عدم وجود سیگنال کلاک باعث بوجود آمدن پدیده ای به نام Glitch در مدارهای لچ و در نتیجه رفتاری نوسانی و بی ثبات می گردد. بنابراین بهتر است برای جلوگیری از این مشکل از فلیپ فلاپ ها که دارای سیگنال کلاک هستند استفاده شود.

سیگنال کلاک فرمانی به فلیپ فلاپ صادر کرده و اجازه می دهد تا حالت فلیپ فلاپ بر حسب سیگنال های ورودی تغییر کند. یعنی فلیپ فلاپ تا زمان رسیدن پالس کلاک هیچ تغییری نمی کند. این ویژگی باعث می شود که در یک مدار ترتیبی گسترده توسط یک پالس ساعت مشترک برای همه ماژول های ترتیبی بتوان مدار را بدون مشکل همگام سازی کرد.

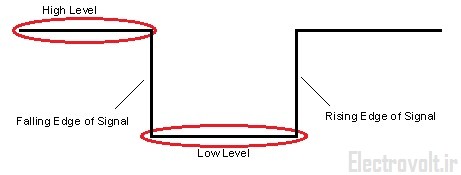

فلیپ فلاپ ها دارای انواع مختلفی نظیر SR-FF ، D-FF ، JK-FF و T-FF می باشند. همه فلیپ فلاپ ها حساس به لبه یا حساس به پالس هستند بدین معنی که تنها در زمان تغییر در لبه یا سطح منطقی پالس کلاک کار می کنند. شکل زیر نواحی مختلف حساسیت برای یک سیگنال کلاک را نشان می دهد که شامل سطح منطقی بالا ، لبه پایین رونده سیگنال ، سطح منطقی پایین و لبه بالارونده سیگنال می باشد.

آشنایی با انواع فلیپ فلاپ

در این بخش با انواع فلیپ فلاپ ها آشنا می شویم. توجه کنید که منظور از Q(t) در اینجا حالت قبلی ( Previous State ) و منظور از Q(t+1) حالت بعدی ( Next State ) می باشد.

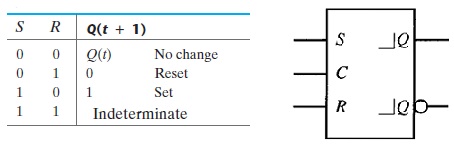

1- فلیپ فلاپ SR :

در ساختار این فلیپ فلاپ از دو لچ SR با فعالساز استفاده شده است که همواره یکی از آن ها غیرفعال می باشد و باعث عدم بوجود آمدن حالت های گذرا و بی ثباتی می گردد. شکل زیر این فلیپ فلاپ را نشان می دهد. زمانی که S=R=0 باشد و لبه بالارونده کلاک بیاید هیچ تغییری در خروجی رخ نمی دهد و حالت قبلی حفظ می گردد. همچنین زمانی که S=0 و R=1 باشد و لبه بالارونده کلاک بیاید خروجی ریست شده و 0 می گردد. در نهایت زمانی که R=0 و S=1 باشد و لبه بالارونده کلاک بیاید خروجی ست شده و 1 می گردد. وضعیت خروجی در حالت R=1 و S=1 نامشخص می باشد و از این حالت استفاده نباید کرد.

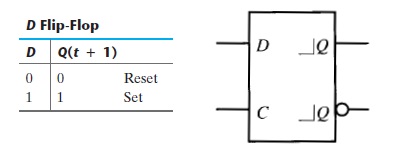

2- فلیپ فلاپ D :

این فلیپ فلاپ که با حذف دو حالت از حالت های فلیپ فلاپ SR بدست می آید ، در شکل زیر نشان داده شده است. زمانی که D=0 شود و لبه بالارونده سیگنال کلاک بیاید ، خروجی نیز برابر 0 می گردد و زمانی که D=1 شود و لبه بالارونده سیگنال کلاک بیاید ، خروجی نیز برابر 1 می گردد.

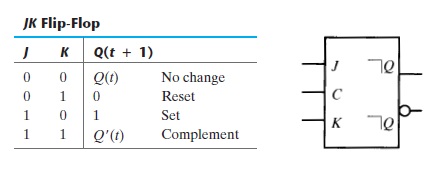

3- فلیپ فلاپ JK :

این فلیپ فلاپ با تغییر حالت تمام یک ( یعنی S=1 و R=1 ) از فلیپ فلاپ SR بدست می آید به طوری که زمانی که ورودی های این فلیپ فلاپ هر دو یک باشند ( یعنی J=1 و K=1 ) خروجی به جای حالت نامشخص ، متمم ( Not ) حالت قبلی می گردد. شکل زیر این فلیپ فلاپ و جدول حالت آن را نشان می دهد. همانطور که مشاهده می کنید این فلیپ فلاپ با لبه پایین رونده کلاک کار می کند.

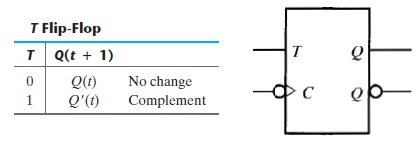

4- فلیپ فلاپ T :

این فلیپ فلاپ که با حذف دو حالت J=0 ، K=1 و J=1 ، K=0 از فلیپ فلاپ JK بدست می آید ، در شکل زیر نشان داده شده است. در صورتی که T=0 باشد حالت قبلی تغییری نمی کند اما در صورتی که T=1 باشد ، با هر بار آمدن لبه پایین رونده پالس کلاک حالت بعدی ، متمم ( Not ) حالت قبلی می گردد.

شیفت رجیستر ( Shift Register )

شیفت رجیستر ها یکی از ماژول های منطقی ترتیبی می باشند که از تعدادی فلیپ فلاپ های ( معمولا نوع D-FF ) ساخته می شوند. شیفت رجیستر ها میتوانند با هر پالس کلاک مکان بیت ها را به چپ یا راست جا به جا کنند. شیفت رجیسترها بر حسب نوع ورودی و خروجی های آن به چهار دسته زیر تقسیم می شوند :

1- ورودی سریال – خروجی سریال ( یا SiSo مخفف Serial in – Serial Out )

دارای یک ورودی ، یک خروجی و یک پالس کلاک می باشد. با هر بار آمدن پالس کلاک ، یک واحد انتقال دیتا داریم. در این شیفت رجیستر در صورتی که به تعداد فلیپ فلاپهای موجود ، کلاک دهیم اولین دیتای وارد شده از خروجی خارج می شود.

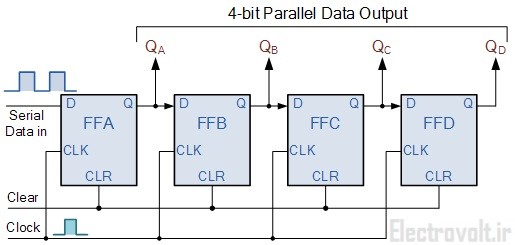

2- ورودی سریال – خروجی موازی ( یا SiPo مخفف Serial in – Parallel Out )

دارای یک ورودی ، به تعداد فلیپ فلاپ ها خروجی و یک پالس کلاک می باشد. با هر بار آمدن پالس کلاک ، یک واحد انتقال دیتا داریم. در این شیفت دیتایی که میخواهیم شیفت داده شود بیت به بیت به صورت سریال وارد می شود و تک تک بیت های خروجی در حین عملیات شیفت قابل مشاهده هستند.

3- ورودی موازی – خروجی سریال ( یا PiSo مخفف Parallel in – Serial Out )

دارای چند ورودی به تعداد فلیپ فلاپ ها ، یک خروجی و یک پالس کلاک می باشد. با هر بار آمدن پالس کلاک ، یک واحد انتقال دیتا داریم.در این شیفت رجیستر دیتایی که میخواهیم شیفت داده شود در ابتدا به صورت موازی وارد می شود و سپس با هر بار کلاک شیفت داده می شود. در اولین کلاک خروجی همان بیت کم ارزش ورودی موازی است و زمانی که به تعداد شیفت رجیسترها کلاک دهیم همه بیت های وارد شده به صورت سریال خارج می شوند.

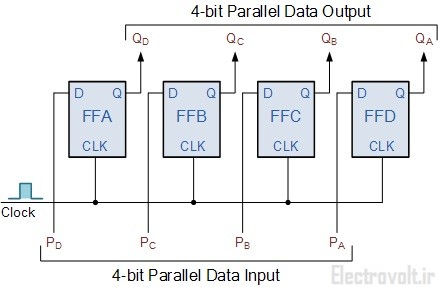

4- ورودی موازی – خروجی موازی ( یا PiPo مخفف Parallel in – Parallel Out )

دارای چند ورودی به تعداد فلیپ فلاپ ها ، به تعداد فلیپ فلاپ ها خروجی و یک پالس کلاک می باشد. با هر بار آمدن پالس کلاک ، یک واحد انتقال دیتا داریم. در این شیفت رجیستر هم دیتایی که میخواهیم شیفت داده شود و هم دیتای شیفت داده شده هر دو به صورت موازی هستند. در ابتدا دیتا به صورت موازی وارد می شود و تک تک بیت های خروجی در حین عملیات شیفت قابل مشاهده هستند.

شمارنده ( Counters )

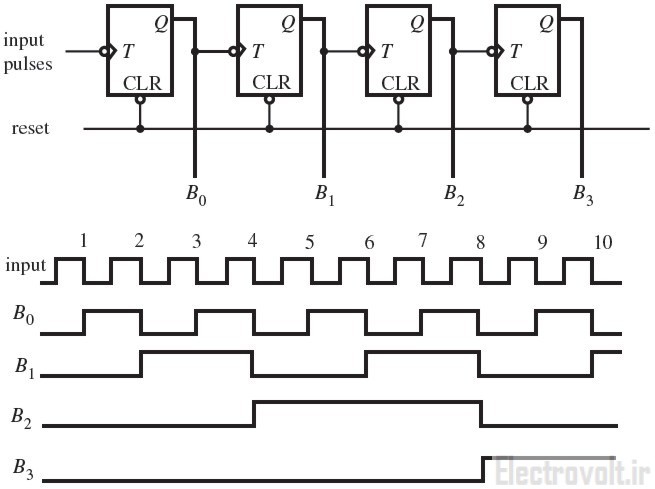

شمارنده ها گروهی از مدارهای منطقی ترتیبی هستند که یک سری از پالس های ورودی را می شمارند ؛ این پالس ها ممکن است ذاتا منظم یا غیر منظم باشند. شمارنده ها بخشی اساسی از مدارهای منطقی دیجیتال هستند که معمولا از فلیپ فلاپ های JK یا T ساخته می شوند. شکل زیر یک شمارنده را نشان می دهد که با T-FF ساخته شده است. اگر ورودی این شمارنده پالس منظمی نظیر پالس کلاک باشد ، با عبور از هر فلیپ فلاپ T ، فرکانس سیگنال تقسیم بر 2 می گردد.

همانطور که مشاهده می کنید ، پهنای پالس سیگنال منظم کلاک بعد از عبور از هر فلیپ فلاپ دو برابر شده است ( با دو برابر شدن عرض پالس فرکانس نصف می گردد ).

مقایسه کننده ( Comparator )

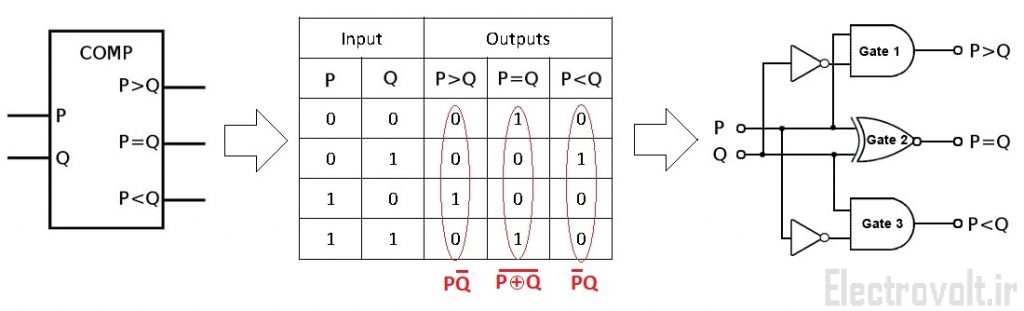

مقایسه کننده ها یکی از مدارهای منطقی ترکیبی مهم به شمار می روند. یک مقایسه کننده دارای دو ورودی n بیتی و سه خروجی 1 بیتی می باشد که در شکل زیر آن را مشاهده می کنید. عملکرد یک مقایسه کننده به این صورت است که ابتدا مقدار ورودی ها را با یکدیگر مقایسه می کند. در صورتی که P>Q ( ورودی P بزرگتر از ورودی Q باشد ) خروجی اول 1 و بقیه خروجی ها 0 می شود. در صورتی که P=Q ( ورودی P و Q برابر هم باشند ) خروجی دوم 1 و بقیه خروجی ها 0 می شود. در صورتی که P<Q ( ورودی P کوچکتر از ورودی Q باشد ) خروجی سوم 1 و بقیه خروجی ها 0 می شود.

شکل زیر یک مقایسه کننده 1 بیتی را به همراه جدول درستی و مدار منطقی معادل آن نشان می دهد.

انواع ریست در مدارهای دیجیتال

ریست ( Reset ) سیگنالی است که در مدارهای دیجیتال باعث راه اندازی اولیه مدار می گردد. زمانی که تغذیه مدار وصل می گردد ، حالت اولیه مدار مشخص نیست. تمامی مدارهای ترتیبی دیجیتال باید ریست داشته باشند چرا که با ریست شدن ، مدار به یک حالت اولیه مشخص می رود و فلیپ فلاپها حالت اولیه مشخصی پیدا می کنند. سیگنال ریست را معمولا Active Low در نظر می گیرند که با صفر شدن فعال می گردد.

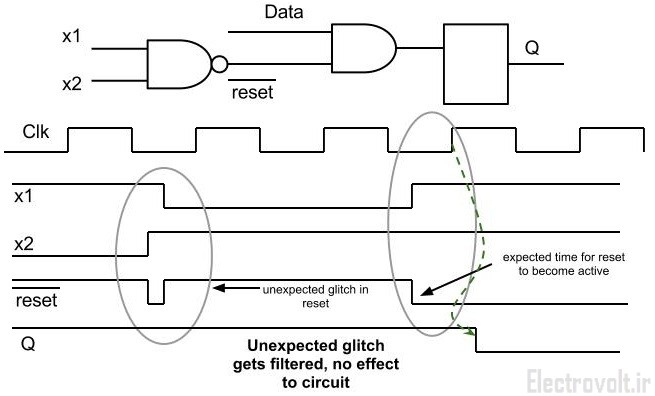

در مدارهای دیجیتال دو نوع ریست وجود دارد. ریست سنکرون ( Synchronous reset ) که به محض آمدن سیگنال ریست اعمال می شود و ریست آسنکرون ( Asynchronous reset ) که بعد از آمدن سیگنال ریست و لبه کلاک اعمال می شود.

نکته : هر چند که ریست آسنکرون سریعتر از ریست سنکرون می باشد اما در صورت استفاده نادرست ممکن است موجب ناپایداری مدار شود. بنابراین معمولا از ریست سنکرون به علت اطمینان بیشتر استفاده می شود. شکل زیر نمودار مربوط به یک مدار دارای ریست سنکرون را مشاهده می کنید. در سمت چپ سیگنال ریست دچار Glitch شده است اما به علت وابسته بودن سیگنال ریست به لبه بالارونده سیگنال کلاک تاثیری در مدار نگذاشته است و مدار ریست نشده است. در سمت راست سیگنال ریست به مدت طولانی واقعا اعمال شده است و بر روی مدار هم تاثیر گذاشته و خروجی ریست شده است.

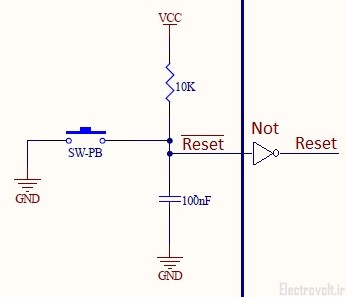

نکته : پایه ریست از بیرون آی سی به یک سوئیچ به همراه مقاومت و خازن متصل می گردد که در شکل زیر آن را مشاهده می کنید.

برای رفتن به بخش بعدی روی تصویر زیر کلیک نمایید

در صورتی که این مطلب مورد پسندتان واقع شد لایک و اشتراک گذاری فراموش نشود

دیدگاه (15)

این سایت عالیه موفق باشید اگه مطالب سایت به صورت pdf در دسترس بود خیلی عالیه می شد آخه همه جا به اینترنت دسترسی ندارد

خیلی ممنون و متشکر از حسن نظرتون . به محض تکمیل شدن آموزش ها حتما به صورت pdf قرار خواهم داد .

با درود

کاش امکان دانلود یا ذخیره اطلاعات رو میذاشتین..

تصاویر و متنها جالب نگارش شدهاند.

درود بر شما دوست عزیز … در پایان آموزش FPGA ( اواخر امسال ) حتما امکان دانلود یکجا به صورت pdf میزارم

با سلام

ممنون بابته مطالبتون لطفا امکان دانلود را قرار بدهید

سلام دوست عزیز این امکان برای آموزش های AVR و ARM وجود دارد و برای FPGA نیز در آینده وجود خواهد داشت.

واقعا عالی بود

ممنون

ممنون از زحماتتون واقعا خسته نباشید همونطور که یکی از دوستان فرمودند اگه مطالب رو Pdf کنید تا وقتی که اینترنت در دسترس نیست بتونیم استفاده کنیم خیلی خوب میشد

خواهش میکنم دوست عزیز حتما به محض پایان آموزش ها همه آن ها را در قالب یک pdf ارائه خواهیم کرد با ما همراه باشید

سلام و خسته نباشید بایت سایت خوبتون

مهندس جسارتا قسمت تفریق کننده فکر میکنم مشکل داره چون شما در سیستم مکمل 2 دارید صحبت میکنید پس منفی یک عدد نمیتونه با XOR تک تک بیت ها با 1 به دست بیاد بلکه اون مکمل 1 یک عدده که میتونه با XOR تک تک بیت ها با 1 به دست بیاد.لذا در سیستم مکمل 2 این مدار که هم جمع کنندست و هم تفریق کننده به نظرمن اشکال داره.

ممنون میشم اگر رفع ابهام کنید

سلام دوست عزیز

بله حرف شما درسته و این مشکل وجود داره

ویرایش خواهد شد

ممنونم

با سلام

تشکر میکنم بخاطر سایت خوبتون

سلام

توضیحات کامل مدار ضرب کننده رو از کجا میتونم پیدا کنم؟

سلام

پک آموزشی برای میکروکنترلرها و fpga دارین؟؟

سلام دوست عزیز برای میکروکنترلرهای AVR و ARM داریم برای FPGA خیر. به فروشگاه محصولات دانلودی مراجعه نمایید.