# **Embedded in Embedded**

ARM Cortex-M Embedded Design from 0 to 1

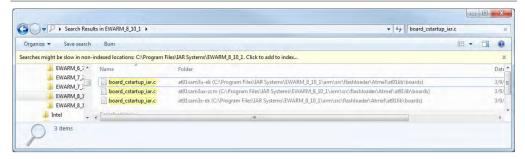

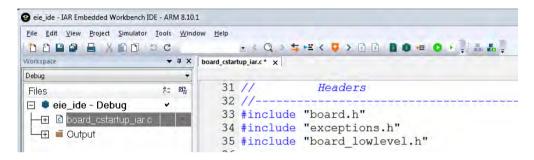

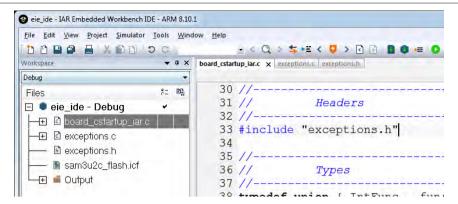

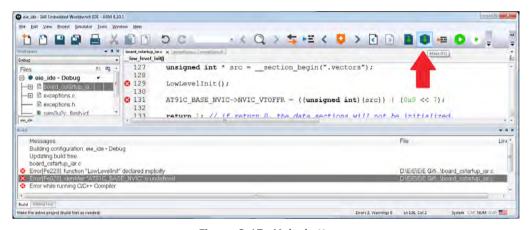

LEARN • DESIGN • SHARE • LEARN • LEARN • DESIGN • SHARE • LEARN • DESIGN • SHARE • LEARN • DESIG

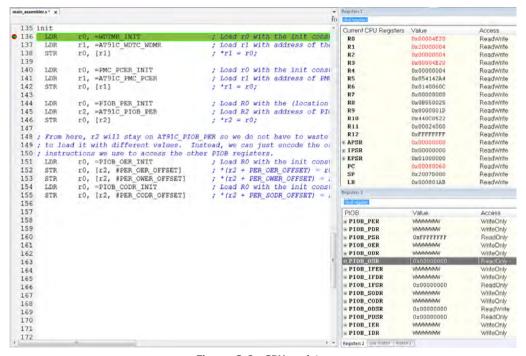

## **Embedded in Embedded**

ARM Cortex-M embedded design from 0 to 1

Jason Long

an Elektor Publication

LEARN DESIGN SHARE

This is an Elektor Publication. Elektor is the media brand of Elektor International Media B.V.

78 York Street London W1H 1DP, UK

Phone: (+44) (0)20 7692 8344

© Elektor International Media BV 2018 First published in the United Kingdom 2018

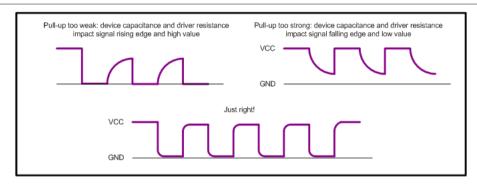

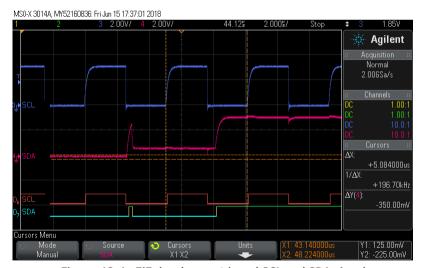

#### 179014-1/EN

- All rights reserved. No part of this book may be reproduced in any material form, including photocopying, or storing in any medium by electronic means and whether or not transiently or incidentally to some other use of this publication, without the written permission of the copyright holder except in accordance with the provisions of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London, England W1P 9HE. Applications for the copyright holder's written permission to reproduce any part of this publication should be addressed to the publishers. The publishers have used their best efforts in ensuring the correctness of the information contained in this book. They do not assume, and hereby disclaim, any liability to any party for any loss or damage caused by errors or omissions in this book, whether such errors or omissions result from negligence, accident or any other cause.

- British Library Cataloguing in Publication Data Catalogue record for this book is available from the British Library

- ISBN 978-1-907920-73-8

Prepress production: DMC | daverid.com Printed in the Netherlands by Wilco

Elektor is part of EIM, the world's leading source of essential technical information and electronics products for pro engineers, electronics designers, and the companies seeking to engage them. Each day, our international team develops and delivers high-quality content - via a variety of media channels (e.g., magazines, video, digital media, and social media) in several languages - relating to electronics design and DIY electronics. www.elektor.com

#### **Dedication**

To Adym, Ben, and Eryn: those who matter most.

To Amy Strutt, Barry Moore, and Hanson Zheng who have shown unconditional confidence and belief in me. Also to Dr. Mike Smith at the Schulich School of Engineering for all the fundamental knowledge you provided, and the two decades of continued support.

My reviewers and friends, Jon, Vipin and Pouyan. You are amazing people.

To the disproportionally high number of influential people in my life named Steve that the Universe seems to produce at just the right time and in just the right way.

Finally, a big thank you to Ferdinand and Don at Elektor for their patience with my "off by an order of magnitude" estimates, and my editor Dave for his tireless efforts in somehow deciphering my napkin sketches and putting this all together.

#### **Acknowledgements**

The following material is reproduced in this book with the kind permission of the respective copyright holders and may not be reprinted, or reproduced in any way without their prior consent.

Figure 1-1: Weekly World News

Figure 1-2: Stockphoto

Figure 1-5: www.microchip.com

Figure 1-6: http://learnprotocol.blogspot.ca/2014/07/learn-ic-packages-01.html

Figure 1-7: ARM Cortex Microcontrollers

Figure 1-9, Figure 3-1, Figures 4-12 to 4-14, Figures 5-5 to 5-6 and 5-9, Figures 6-7 to 6-9, Figures 7-1, 7-9, 7-10, Figures 8-3, 8-5, Figure 9-5, Figures 10-8, 10-9, 10-11 and 10-13, Figures 11-2, 11-6, 11-7, Figure 12-5 and Figures 13-5, 13-6, 13-9, and 13-12:

Atmel-6430G-ATARM-SAM3U-Series-Datasheet 31-Mar-15

Figure 1-10: https://www.wayneandlayne.com/projects/blinky/design/

Figure 1-14: https://www.digikey.com/product-detail/en/tag-connect-llc/TC2050-

IDC-430/TC2050-IDC-430-ND/2605368

**Engenuics Technologies** Figure 1-15:

Figure 1-19: https://pitchengine.com/dd/2017/11/20/crystal-oscillators-market-

report-2016-2023/002518911240077147806

Figure 3-2: SAM3U User Guide 6430F-ATARM-21-FEB-12, p, 59

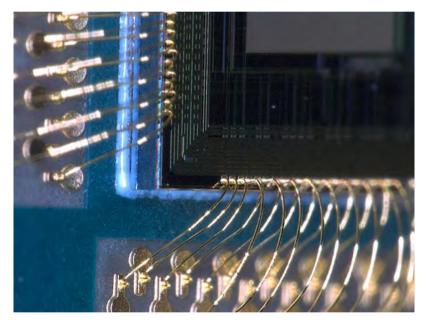

Figure 5-1: http://www.teledynemicro.com/space/fine-pitch-wire-bonding

Figure 5-8: Register table for the PIO controller SAM3U Series [DATASHEET]

Figure 6-3: 6430F-ATARM-21-Feb-12, p. 5

Figures 12-14, 12-17, 12-18 and 12-20:

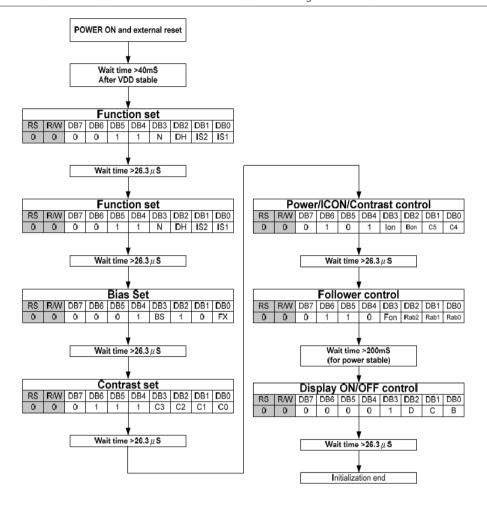

Sitronix ST7036 Dot Matrix LCD Controller/Driver data sheet, p. 16

Figure 14-1: Interfacing with ANT General Purpose Chipsets and Modules v2.0, p.4,

**Dvnastream Innovations**

Figures 14-5 and 14-6:

ANT message protocol and usage 5.1.pdf page 34, Dynastream

Innovations Inc.

### **Table of Contents**

| Preface                                                  |

|----------------------------------------------------------|

| Chapter 1 • Getting started                              |

| 1.1 • A Micro what?19                                    |

| 1.2 • The 32-bit Processor                               |

| 1.3 • Microcontroller Programs                           |

| 1.4 • The Clock                                          |

| 1.5 • The Fundamentals                                   |

| 1.5.1 • Number Systems                                   |

| 1.5.2 • Ohm's Law                                        |

| 1.6 • Switches                                           |

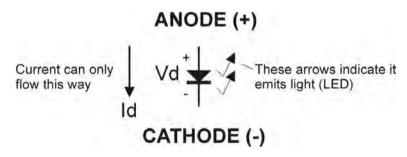

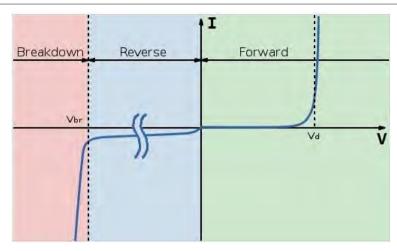

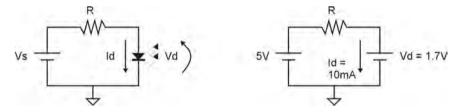

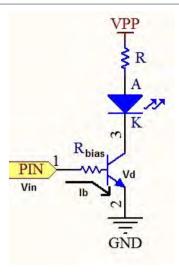

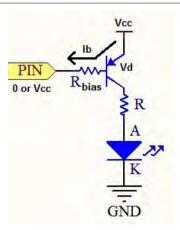

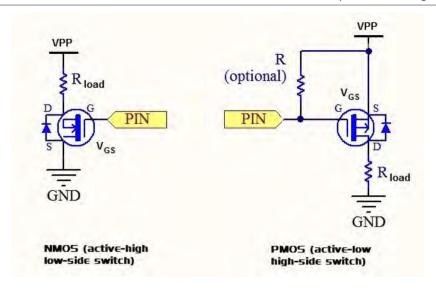

| 1.7 • Light Emitting Diodes (LEDs)                       |

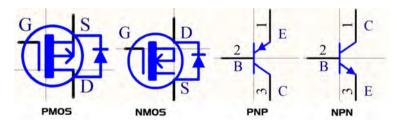

| 1.8 • Transistors                                        |

| 1.9 • Power Supplies                                     |

| 1.9.1 • Linear Regulators                                |

| 1.9.2 • Switching Power Supplies                         |

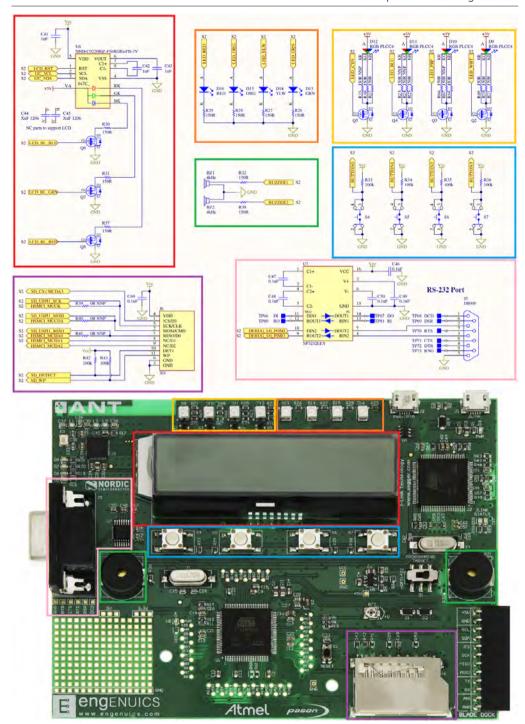

| 1.10 • Development Board Hardware50                      |

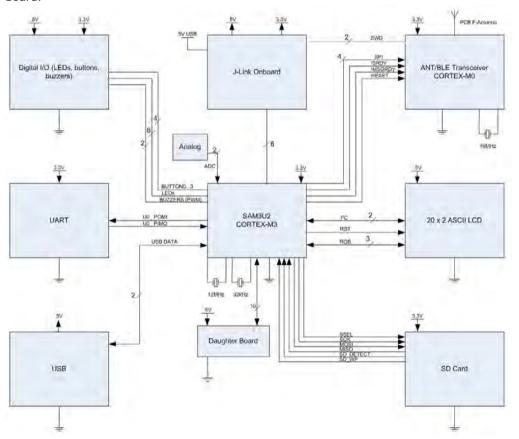

| 1.11 • Block Diagram                                     |

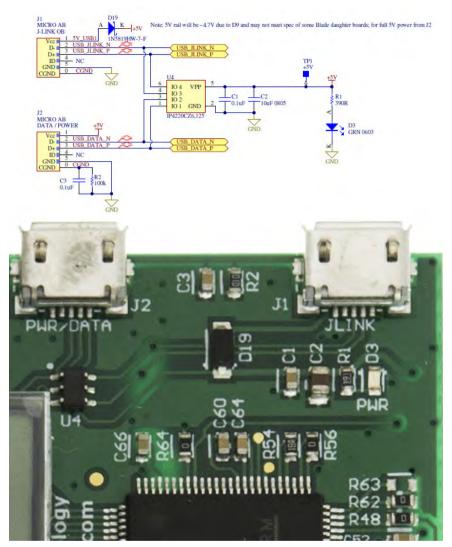

| 1.12 • Power Input                                       |

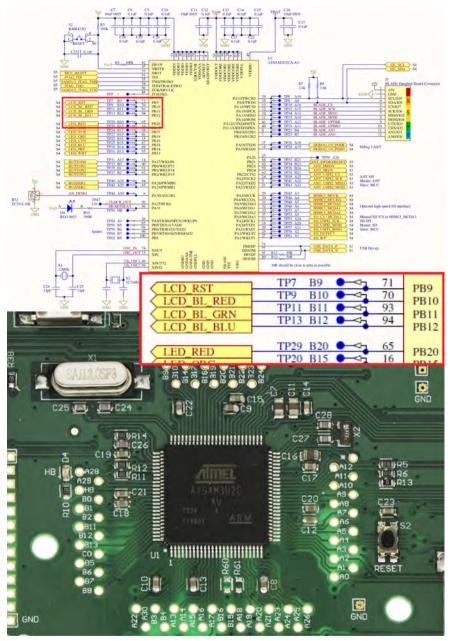

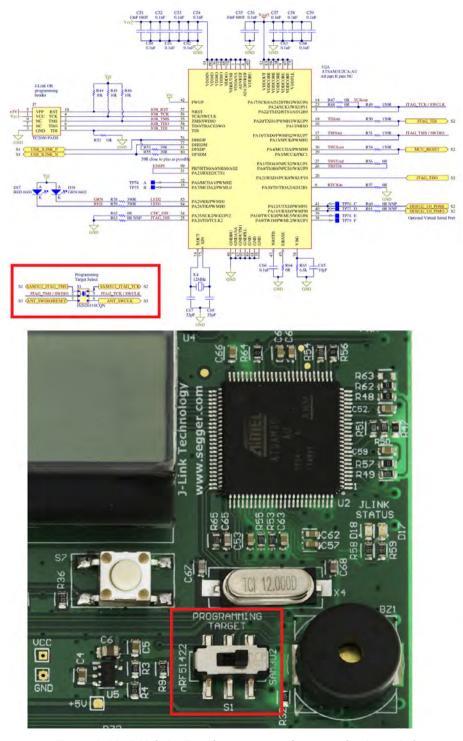

| 1.13 • Main processor, JTAG, clocks, and connections     |

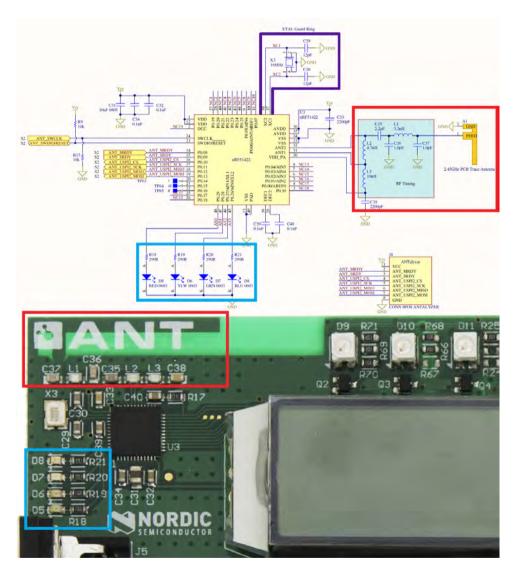

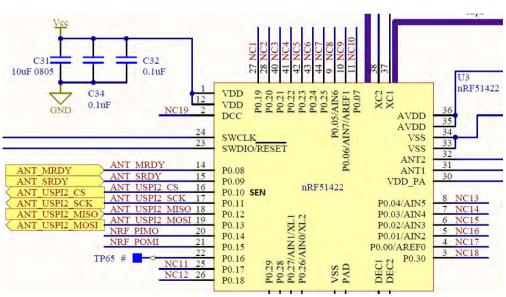

| 1.14 • ANT 2.4GHz Transceiver                            |

| 1.15 • User IO: LCD, LEDs, Buttons, Beeper56             |

| 1.16 • J-Link On-Board                                   |

| 1.17 • Summary                                           |

| Chapter 2 • Development Environment & Version Control 61 |

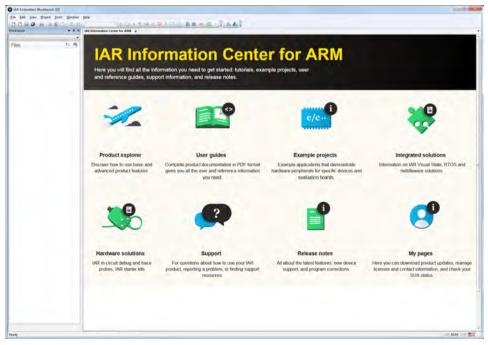

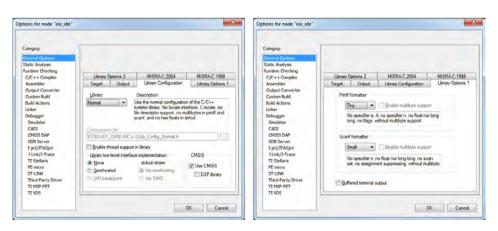

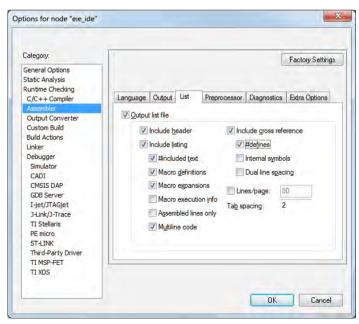

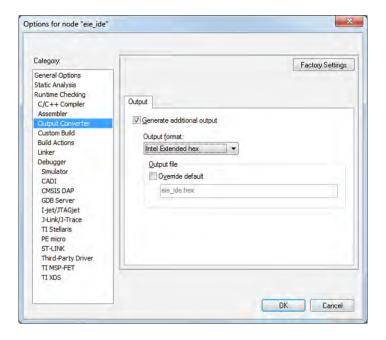

| 2.1 • IAR Integrated Development Environment             |

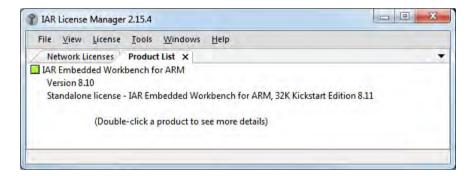

| 2.2 • IAR Installation                                   |

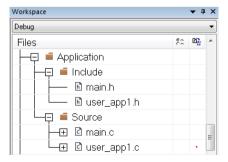

| 2.3 • Setting Up a New Project                           |

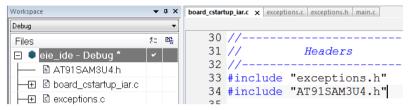

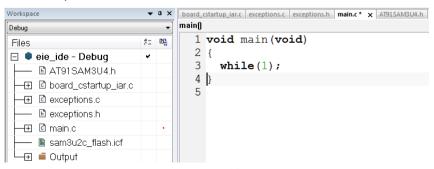

| 2.4 • Files in a New Project                             |

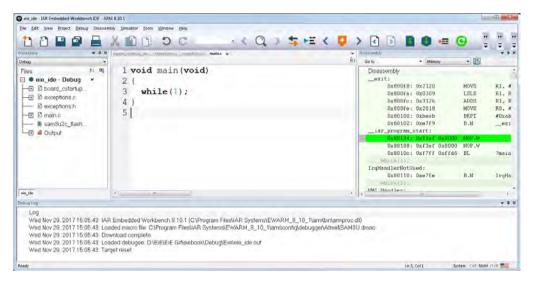

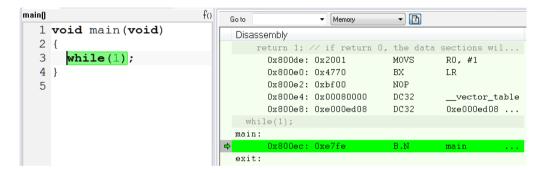

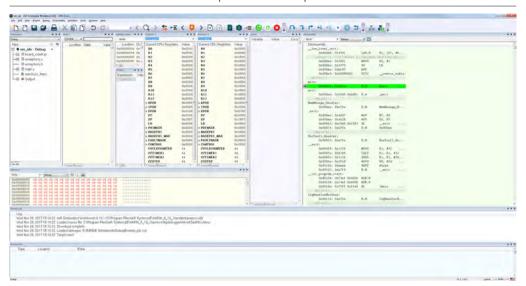

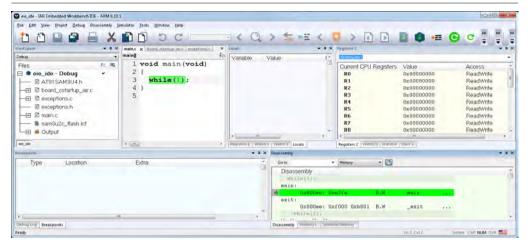

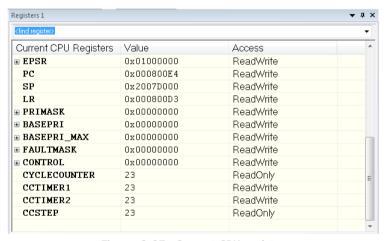

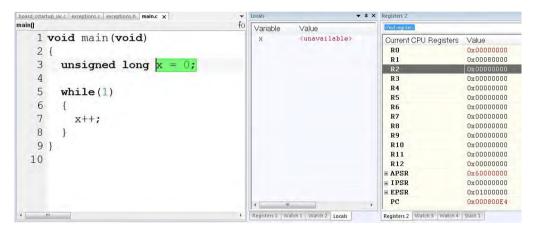

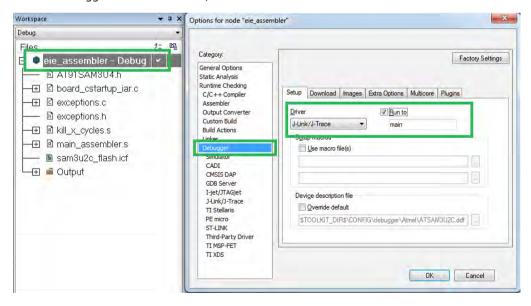

| 2.5 • IAR Simulator and Debugger                         |

| 2.6 • Other Development Tools                            |

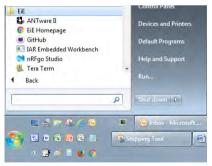

| 2.6.1 • Tera Term                           | 81  |

|---------------------------------------------|-----|

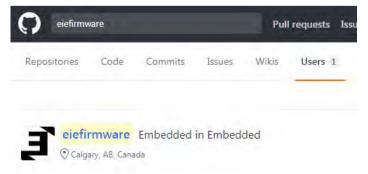

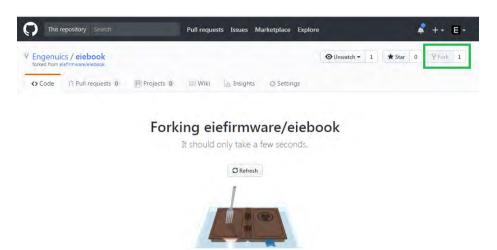

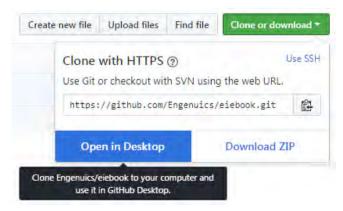

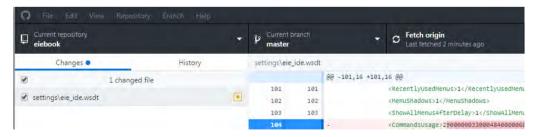

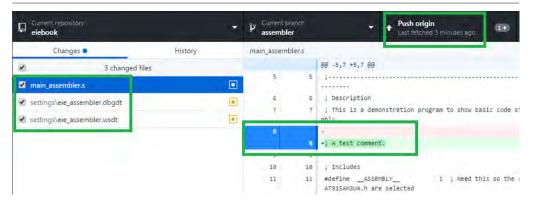

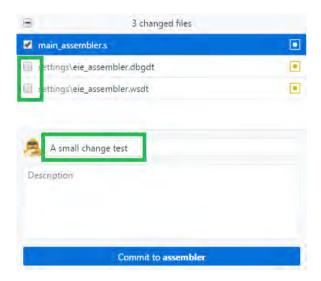

| 2.6.2 • GitHub Desktop                      | 82  |

| 2.6.3 • ANTware II                          | 82  |

| 2.6.4 • nRFgo Studio                        | 82  |

| 2.6.5 • Windows Settings                    | 83  |

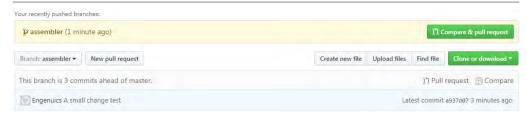

| 2.7 • Version control with Git              | 83  |

| Chapter 3 • ARM Cortex-M3 Assembly Language | 91  |

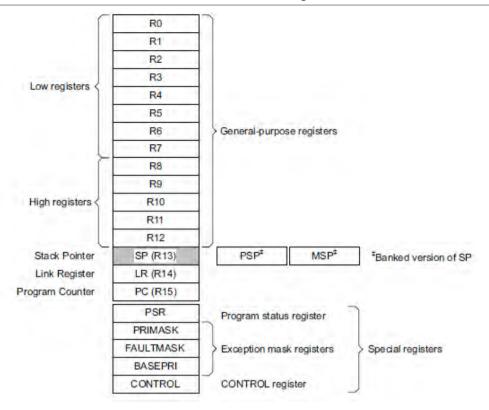

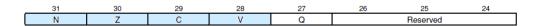

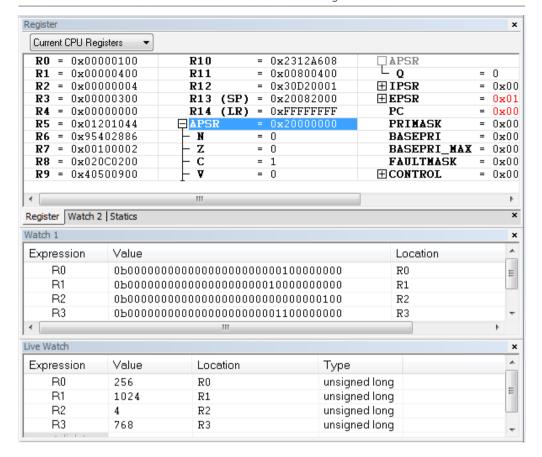

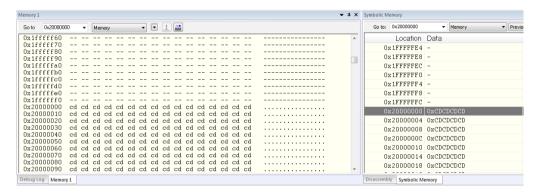

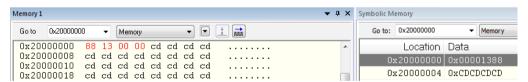

| 3.1 • Core Registers                        | 91  |

| 3.2 • Instructions                          | 93  |

| 3.3 • Assembly Language Syntax              | 94  |

| 3.4 • Load and Store Instructions           | 101 |

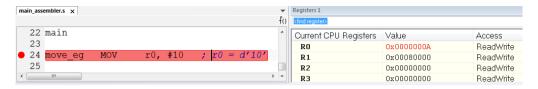

| 3.5 • Hello World in Assembly               | 103 |

| Chapter 4 • Embedded C                      | 115 |

| 4.1 • Documentation                         | 115 |

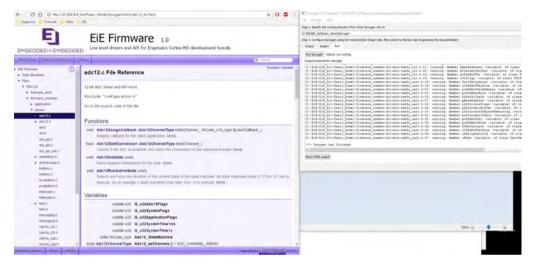

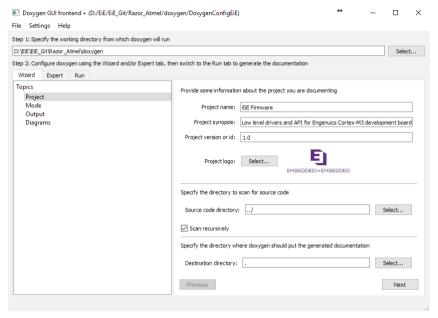

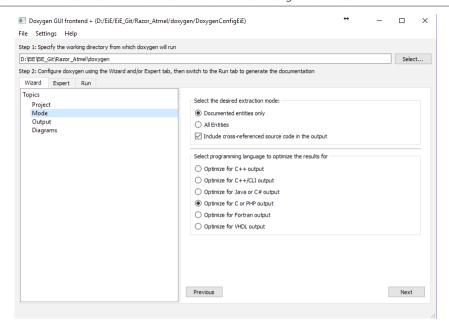

| 4.2 • Doxygen                               | 117 |

| 4.2.1 • Documenting the "right information" | 117 |

| 4.2.2 • Create a Configuration File         | 118 |

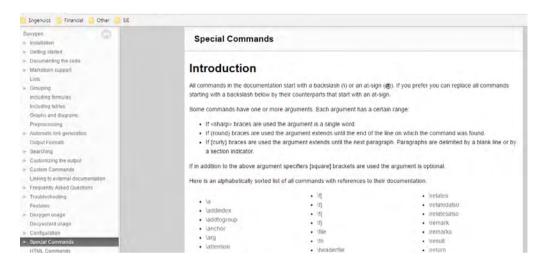

| 4.2.3 • Special Comment Blocks              | 120 |

| 4.2.4 • Doxygen tags in code                | 122 |

| 4.2.5 • Doxygen Example                     | 123 |

| 4.3 • Coding Conventions                    | 125 |

| 4.3.1 • Type Definitions                    | 125 |

| 4.3.2 • Hungarian Notation                  | 126 |

| 4.3.3 • Preprocessor Symbol Definitions     | 127 |

| 4.3.4 • Braces { }                          | 127 |

| 4.3.5 • Switch statements                   | 127 |

| 4.3.6 • White Space                         | 128 |

| 4.3.7 • Global Variables                    | 128 |

| 4.3.8 • Doxygen Tags                        | 129 |

| 4.3.9 • Function Declarations               | 129 |

| 4.3.10 • State Declarations                 | 130 |

| 4.3.11 • Tabs and Indenting                 | 130 |

|    | 4.3.12 • Operator Precedence              |

|----|-------------------------------------------|

|    | 4.4 • C project file overview             |

|    | 4.4.1 • Accessing Registers               |

|    | 4.5 • How A Processor Starts Up           |

|    | 4.5.1 • Watchdog Timer                    |

|    | 4.5.2 • Clock and Power Initialization    |

|    | 4.5.3 • Implementing the clock setup141   |

|    | 4.6 • GPIO Initialization                 |

|    | 4.7 • Program Structures                  |

|    | 4.7.1 • The Infinite Loop                 |

|    | 4.7.2 • Operating Systems                 |

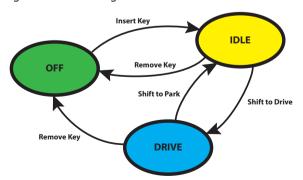

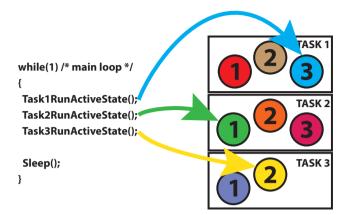

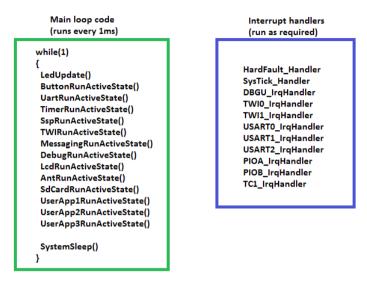

|    | 4.7.3 • State Machine Super Loop          |

|    | 4.8 • Implementing the SM Super Loop      |

|    | 4.8.1 • Initialization                    |

|    | 4.8.2 • State Machine Super loop          |

|    | 4.9 • helloworld.c                        |

|    | 4.10 • Next Steps                         |

| Cŀ | napter 5 • GPIO & LED Driver              |

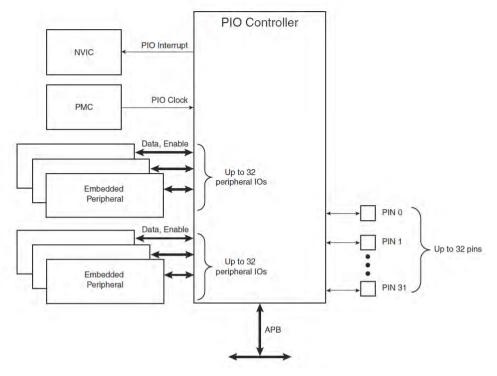

|    | 5.1 • SAM3U2 General Purpose Input Output |

|    | 5.2 • External Hardware                   |

|    | 5.2.1 • Pin Allocation                    |

|    | 5.3 • The PIO Peripheral                  |

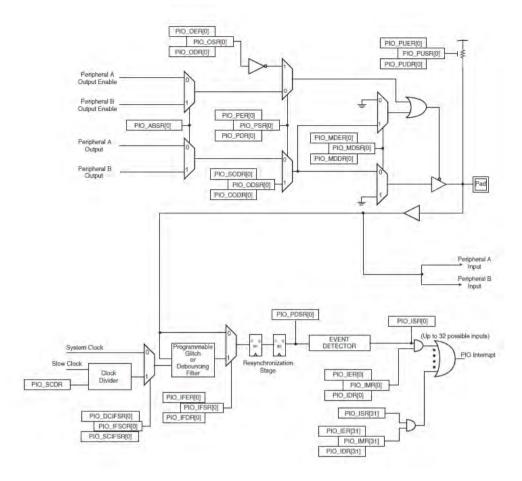

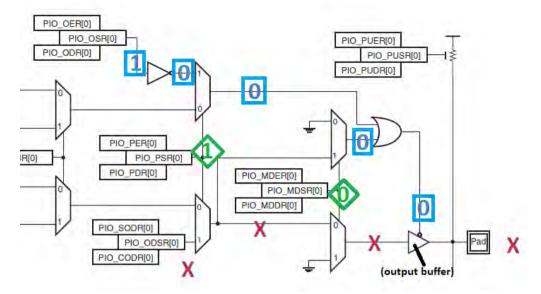

|    | 5.4 • PIO Internal Hardware               |

|    | 5.4.1 • Logic Block Diagram               |

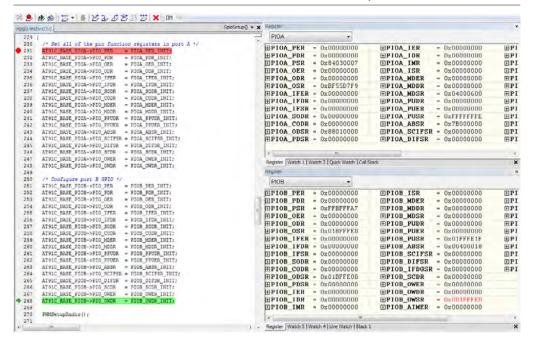

|    | 5.5 • PIO Registers                       |

|    | 5.6 • Adding a New Task                   |

|    | 5.7 • The LED Driver                      |

|    | 5.8 • Driver Implementation               |

|    | 5.9 • Blinking                            |

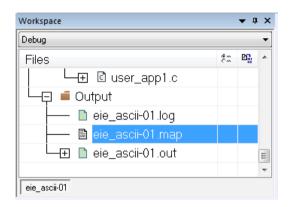

|    | 5.9.1 • Map File                          |

|    | 5.10 • Chapter Exercise                   |

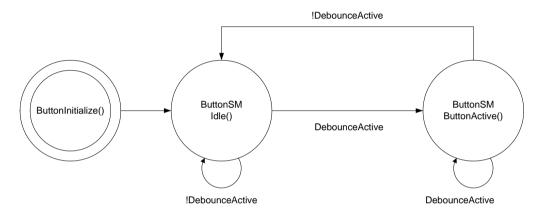

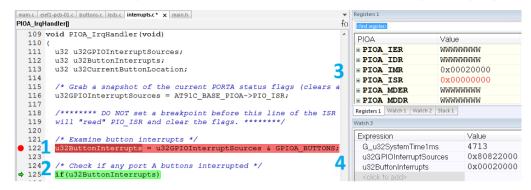

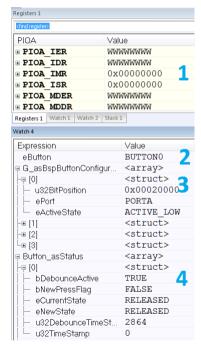

| Chapter | 6 • Interrupts & Button Drivers                                                                                                                                                |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

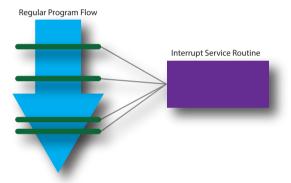

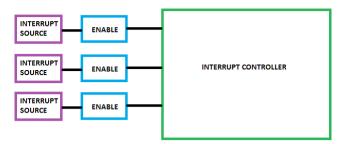

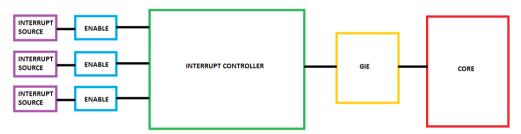

| 6.1 •   | Interrupts                                                                                                                                                                     |

| 6.2 •   | Interrupts on the SAM3U2                                                                                                                                                       |

| 6.3     | 2.1 $ullet$ Interrupts depend on hardware                                                                                                                                      |

| 6.3     | 2.2 $ullet$ Interrupts need to be configured by firmware                                                                                                                       |

| 6.3     | 2.3 $ullet$ Interrupts can be enabled and disabled globally $\dots \dots \dots \dots \dots 196$                                                                                |

| 6.3     | $2.4 ullet$ An interrupt forces the processor to run an Interrupt Service Routine $\dots 196$                                                                                  |

| 6.3     | 2.5 • Interrupts have priorities                                                                                                                                               |

| 6.3     | 2.6 $ullet$ Interrupts can (and will) occur anytime, anywhere $\dots \dots 198$                                                                                                |

| 6.3     | 2.7 • Interrupts require context preservation                                                                                                                                  |

| 6.3     | $2.8$ $ullet$ Interrupts set flags that need to be cleared $\dots \dots \dots$ |

| 6.3     | 2.9 • ISRs should be short and fast199                                                                                                                                         |

| 6.3 •   | Interrupt User Guide Resources                                                                                                                                                 |

| 6.4 •   | Interrupts and C                                                                                                                                                               |

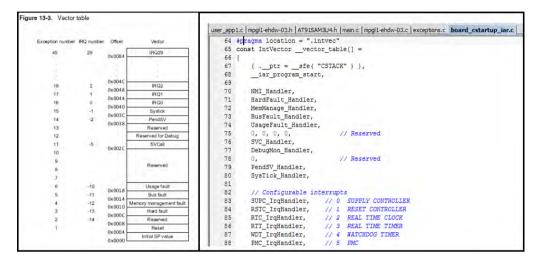

| 6.4     | 4.1 • Vector Table                                                                                                                                                             |

| 6.4     | 4.2 • Priorities                                                                                                                                                               |

| 6.4     | $4.3 ullet$ Enabling and Disabling Peripheral Interrupt Sources $\dots \dots \dots 204$                                                                                        |

| 6.5 •   | Peripheral Interrupts                                                                                                                                                          |

| 6.      | 5.1 • GPIO Interrupts                                                                                                                                                          |

| 6.      | 5.2 • Timer / Counter Interrupts                                                                                                                                               |

| 6.      | 5.3 • Communication Peripheral Interrupts                                                                                                                                      |

| 6.      | 5.4 • Other Peripheral Interrupts                                                                                                                                              |

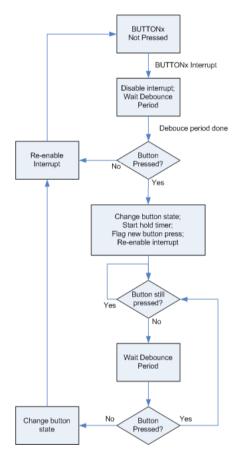

| 6.6 •   | Button Driver Overview and Setup                                                                                                                                               |

| 6.0     | 6.1 • Debouncing                                                                                                                                                               |

| 6.0     | 6.2 • Button history or edge detection                                                                                                                                         |

| 6.0     | 6.3 • Button held                                                                                                                                                              |

| 6.7 •   | Button Operation                                                                                                                                                               |

| 6.      | 7.1 • Button Typedefs                                                                                                                                                          |

| 6.8 •   | PIO Interrupts                                                                                                                                                                 |

| 6.9 •   | Button API                                                                                                                                                                     |

| 6.10    | Chapter Exercise                                                                                                                                                               |

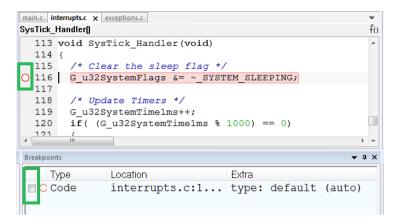

| Chapter 7 • Sleep, System Tick and Timer Peripheral | 25 |

|-----------------------------------------------------|----|

| 7.1 • Sleep                                         | 25 |

| 7.2 • System Tick Configuration                     | 26 |

| 7.2.1 • Tick Time and CTRL INIT value               | 27 |

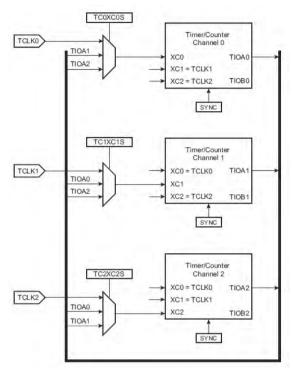

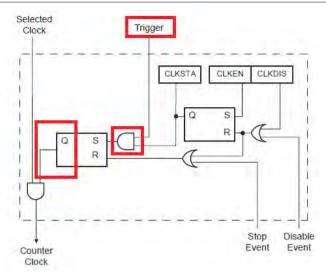

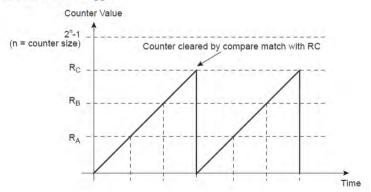

| 7.3 • Timer Peripheral                              | 33 |

| 7.4 • Timer Counter Highlights                      | 35 |

| 7.5 • Timer Counter Registers                       | 37 |

| 7.6 • Timer Driver                                  | 39 |

| 7.7 • Timer API                                     | 40 |

| 7.8 • Chapter Exercise                              | 45 |

| Chapter 8 • Pulse Width Modulation                  | 17 |

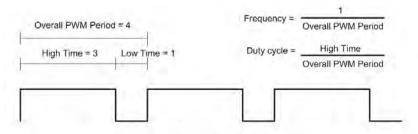

| 8.1 • PWM Concepts                                  | 17 |

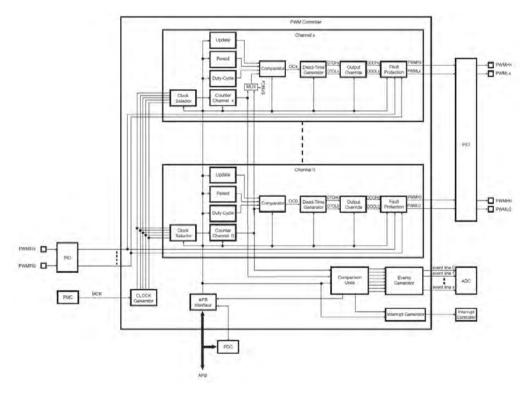

| 8.2 • PWM the Easy Way: SAM3U2 PWM Peripheral24     | 19 |

| 8.3 • Peripheral Highlights                         | 50 |

| 8.4 • PWM and Audio                                 | 51 |

| 8.5 • EiE Audio Hardware25                          | 52 |

| 8.6 • PWM Registers                                 | 53 |

| 8.7 • Development Board Audio Driver                | 56 |

| 8.7.1 • Audio function initialization25             | 56 |

| 8.7.2 • Audio API Functions25                       | 58 |

| 8.7.3 • PWMAudioOn() and PWMAudioOff()26            | 51 |

| 8.8 • PWM the Hard Way: Bit Bashing                 | 52 |

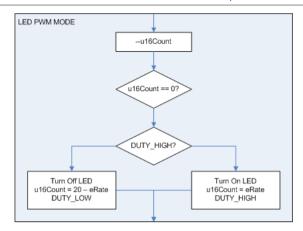

| 8.9 • LED PWM Design                                | 53 |

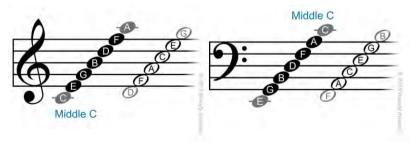

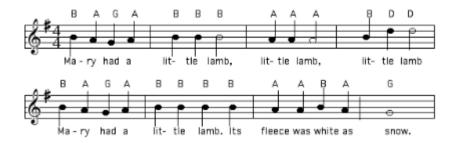

| 8.10 • Audio Bits                                   | 58 |

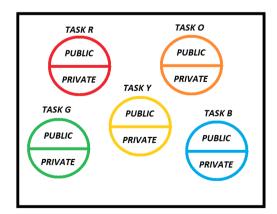

| 8.11 • Multiple User Tasks                          | 70 |

| 8.12 • Chapter Exercise                             | 72 |

| Chapter 9 • DMA and Messaging                       | 73 |

| 9.1 • Data Transmission                             | 73 |

| 9.2 • Resource Conflicts                            | 75 |

| 9.3 • Direct Memory Access – DMA                    | 76 |

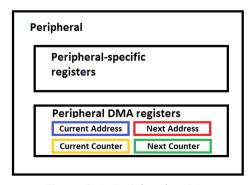

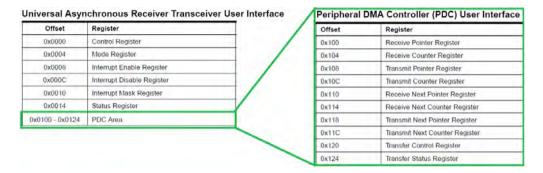

| 9.3.1 • PDC Registers                               | 79 |

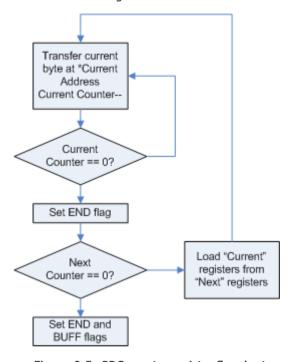

| 9.3.2 • PDC Interrupts                              | 31 |

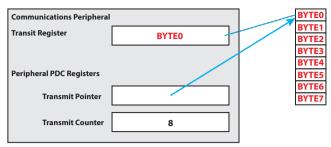

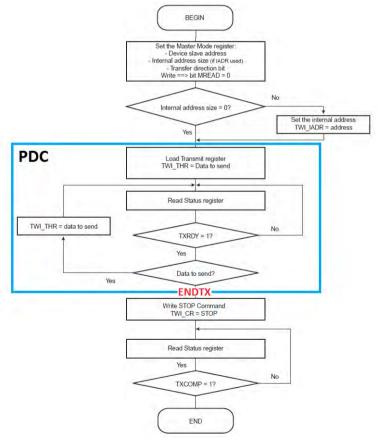

|     | 9.3.3 • Transmitting with DMA28            |

|-----|--------------------------------------------|

|     | 9.3.4 • Receiving with DMA28               |

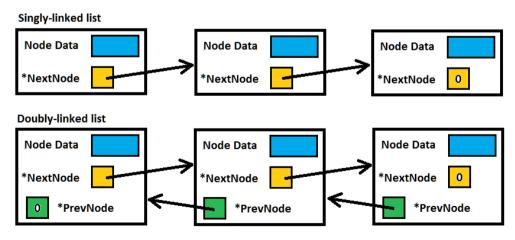

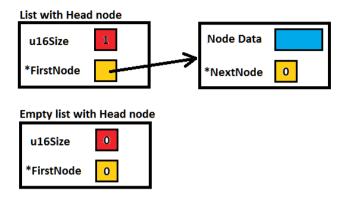

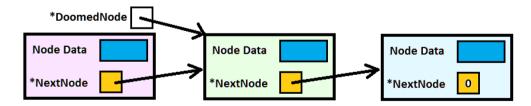

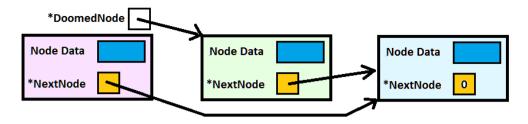

| Ġ   | 9.4 • Linked Lists                         |

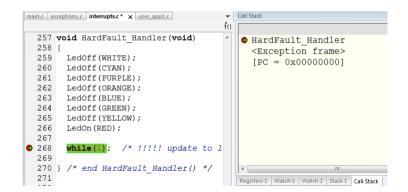

| 9   | 9.5 • Hard Faults                          |

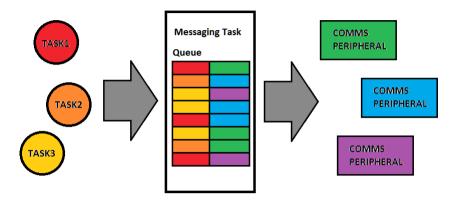

| 9   | 9.6 • EiE Messaging Task                   |

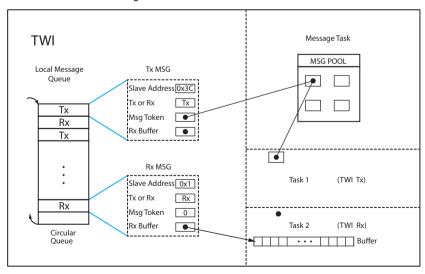

|     | 9.6.1 • Message Task Data Structures       |

|     | 9.6.2 • Message Task Protected Functions29 |

| 9   | 9.7 • Messaging Public Functions           |

|     | 9.7.1 • QueryMessageStatus()               |

| 9   | 9.8 • Messaging State Machine30            |

| Ġ   | 9.9 • Chapter Exercise                     |

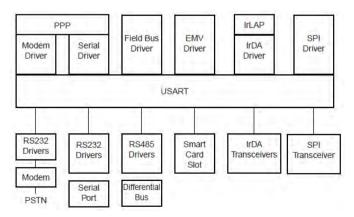

| Cha | pter 10 • Serial and Bugs for Breakfast    |

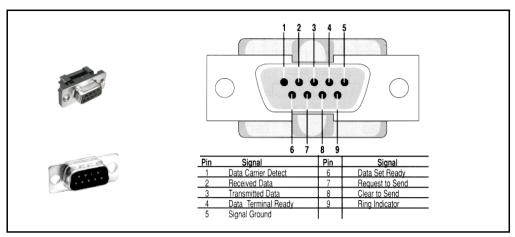

| 1   | 10.1 • RS-232 Overview                     |

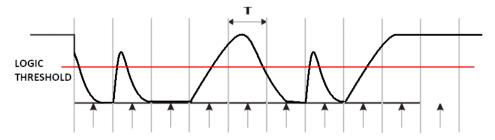

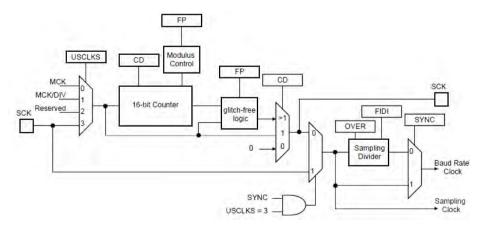

|     | 10.1.1 • Clocking                          |

|     | 10.1.2 • Signaling                         |

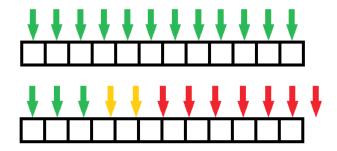

| 1   | 10.2 • Data Errors                         |

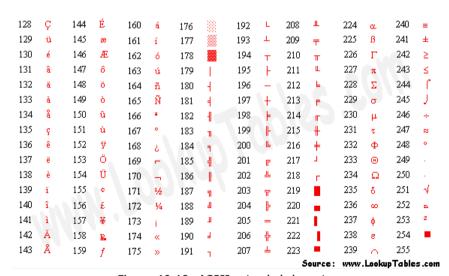

| 1   | 10.3 • ASCII                               |

| 1   | 10.4 • Storing and Displaying Characters31 |

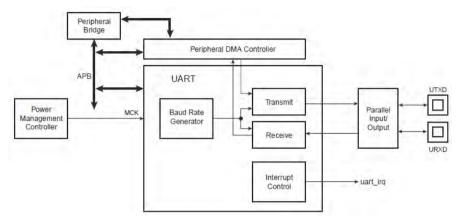

| 1   | 10.5 • SAM3U2 UART Peripheral              |

|     | 10.5.1 • Peripheral Highlights             |

|     | 10.5.2 • Baud Rate Generator               |

| 1   | 10.6 • UART Registers                      |

|     | 10.6.1 • EiE UART Driver                   |

|     | 10.6.2 • UART Task Data Structures32       |

|     | 10.6.3 • UART Driver Functions             |

| 1   | 10.7 • UART Interrupts                     |

| 1   | 10.8 • UART Driver Design                  |

|     | 10.8.1 • Data Transmit                     |

|     | 10.8.2 • Data Receive                      |

| 1   | 10.9 • Dynamic Memory Allocation           |

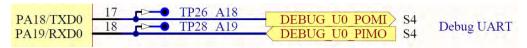

| 1   | 10.10 • Debug Task                         |

| 1   |                                            |

| 10.11.1 • DebugPrintf()                          |

|--------------------------------------------------|

| 10.11.2 • DebugPrintNumber()                     |

| 10.12 • Reading Character Input                  |

| 10.12.1 • DebugInitialize()                      |

| 10.12.2 • DebugRxCallback()                      |

| 10.13 • Debug Programmer Access                  |

| 10.14 • Terminal Control Codes                   |

| 10.15 • Chapter Exercise                         |

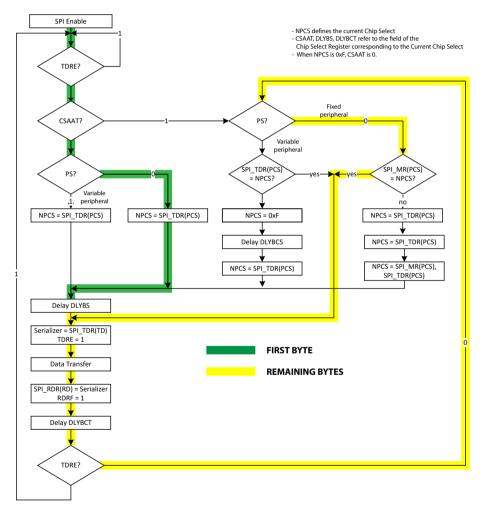

| Chapter 11 • I SPI with my I2C                   |

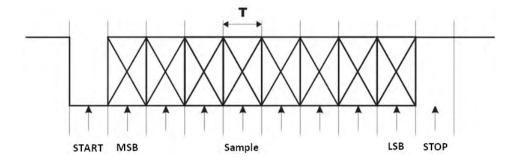

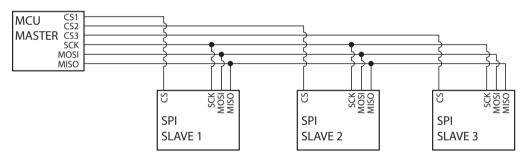

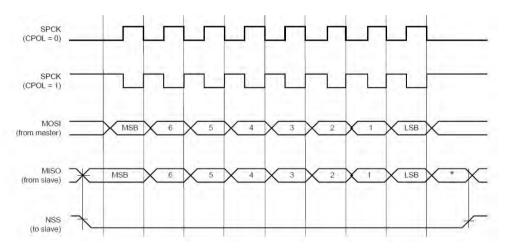

| 11.1 • SPI Signaling                             |

| 11.2 • SPI Hardware                              |

| 11.3 • SPI Registers                             |

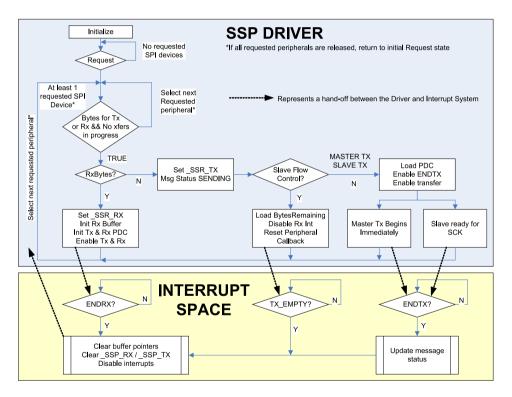

| 11.4 • EiE SPI Driver                            |

| 11.5 • Master Transmit                           |

| 11.6 • Master Receive                            |

| 11.7 • Slave Transmit                            |

| 11.8 • Slave Receive                             |

| 11.9 • Slave Transmit with Flow Control          |

| 11.10 • Slave Receive with Flow Control          |

| 11.11 • Chip Select                              |

| 11.12 • SPI Data Structures                      |

| 11.13 • SPI Driver Functions in Common with UART |

| 11.14 • New SPI Driver Functions                 |

| 11.14.1 • SspRequest()                           |

| 11.14.2 • SspRelease()                           |

| 11.14.3 • SspAssertCS() / SspDeassertCS()        |

| 11.14.4 • SspReadByte() / SspReadData()          |

| 11.14.5 • SspQueryReceiveStatus()                |

| 11.14.6 • SspGenericHandler()                    |

| 11.15 • Ssp State Machine                        |

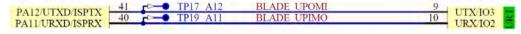

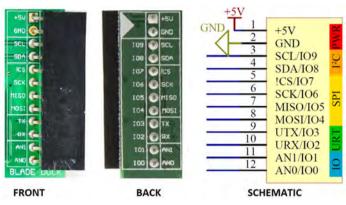

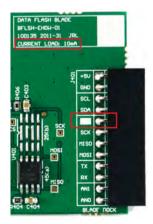

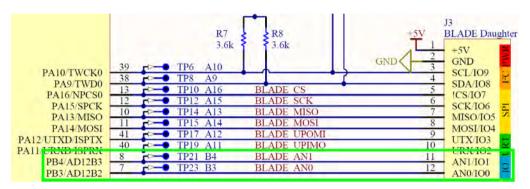

| 11.16 • Blade Daughter Board Interface           |

| 11.17 • Blade Example Project                    |

| 11.17.1 • Blade Firmware Configuration Defaults and Interface    | 398 |

|------------------------------------------------------------------|-----|

| 11.17.2 • UserApp1Initialize()                                   | 401 |

| 11.17.3 • UserApp1SM                                             | 402 |

| 11.18 • Chapter Exercise                                         | 403 |

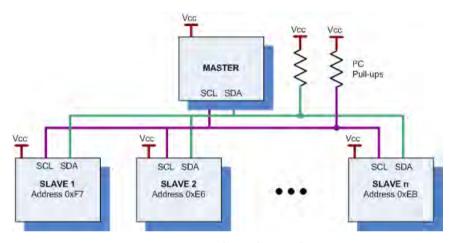

| Chapter 12 • I <sup>2</sup> C & ASCII LCD                        | 405 |

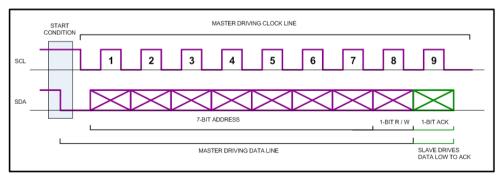

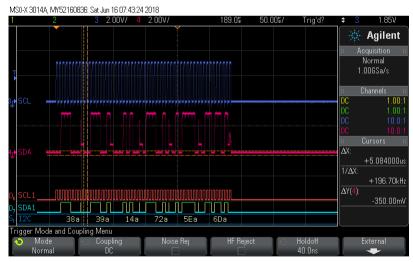

| 12.1 • Inter-Integrated Circuit (I <sup>2</sup> C) Communication | 405 |

| 12.2 • I <sup>2</sup> C Hardware                                 | 406 |

| 12.3 • I <sup>2</sup> C Signaling                                | 408 |

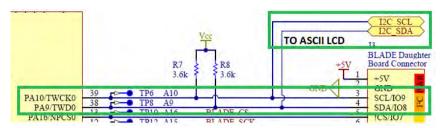

| 12.4 • EiE TWI Hardware                                          | 411 |

| 12.5 • I <sup>2</sup> C (TWI) on SAM3U2                          | 411 |

| 12.6 • TWI and PDC                                               | 412 |

| 12.7 • TWI Registers                                             | 414 |

| 12.8 • TWI Driver                                                | 416 |

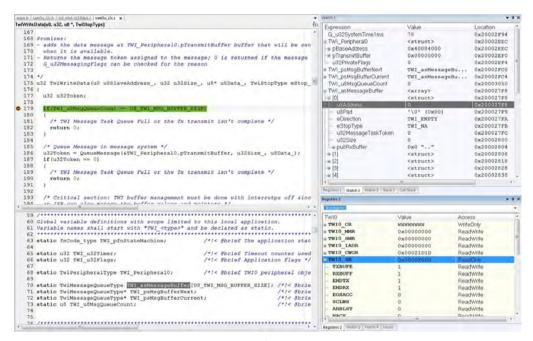

| 12.8.1 • TWI Data Structures                                     | 417 |

| 12.8.2 • TWI Driver Functions                                    | 418 |

| 12.9 • TWI State Machine and ISR                                 | 423 |

| 12.9.1 • TWI Transmit                                            | 423 |

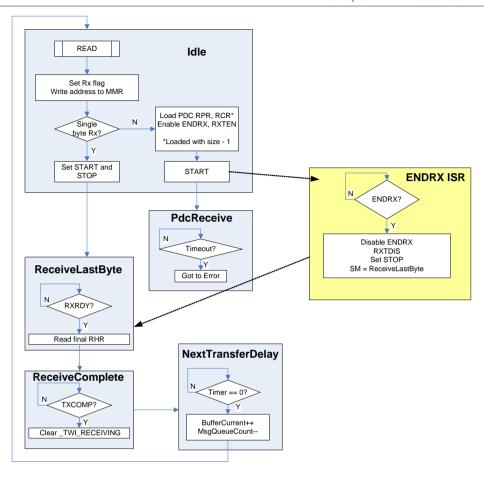

| 12.10 • TWI Receive                                              | 428 |

| 12.10.1 • NACK and Errors                                        | 431 |

| 12.11 • ASCII LCD                                                | 433 |

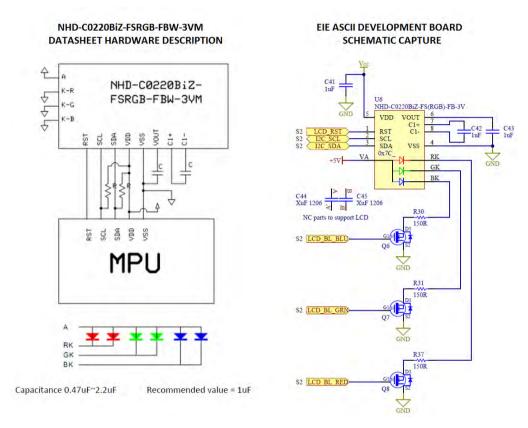

| 12.11.1 • LCD Hardware                                           | 433 |

| 12.11.2 • LCD Controllers                                        | 435 |

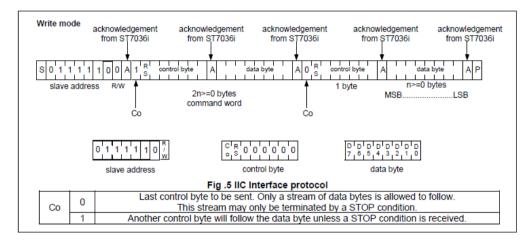

| 12.11.3 • LCD Interface                                          | 436 |

| 12.12 • Character and Control Data                               | 437 |

| 12.13 • Using the LCD Controller                                 | 438 |

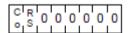

| 12.14 • Control byte with Co and Rs                              | 440 |

| 12.14.1 • Character RAM Addresses                                | 441 |

| 12.14.2 • LCD Command Set                                        | 442 |

| 12.14.3 • LCD Initialization                                     | 443 |

| 12.15 • LCD Application                                          | 446 |

| 12.15.1 • LcdCommand()                                           | 447 |

| 12.15.2 • LcdMessage()                                           | 447 |

| 12.15.3 • LcdClearChars()                    | 448 |

|----------------------------------------------|-----|

| 12.16 • Chapter Exercise                     | 449 |

| Chapter 13 • Analog to Digital Conversion    | 451 |

| 13.1 • ADC background                        | 451 |

| 13.1.1 • Quantization                        | 451 |

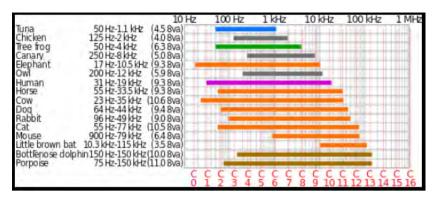

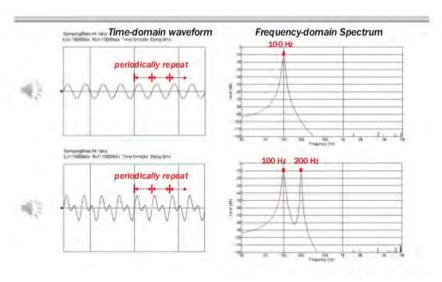

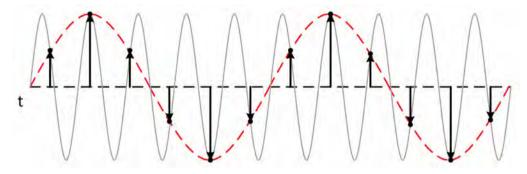

| 13.1.2 • Sampling                            | 451 |

| 13.1.3 • Bandwidth and Aliasing              | 452 |

| 13.1.4 • Nyquist Frequency                   | 453 |

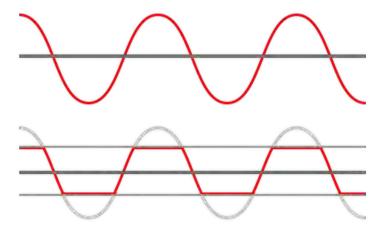

| 13.1.5 • Resolution                          | 454 |

| 13.1.6 • Clipping                            | 455 |

| 13.2 • Characteristics of ADCs               | 455 |

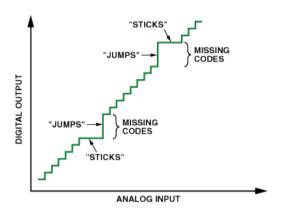

| 13.2.1 • Precision, Error, and ENOB          | 456 |

| 13.2.2 • Missing codes                       | 457 |

| 13.2.3 • Reference Voltages                  | 457 |

| 13.2.4 • Noise                               | 457 |

| 13.2.5 • Single vs. Differential Measurement | 458 |

| 13.2.6 • Signal Conditioning                 | 458 |

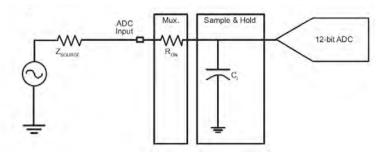

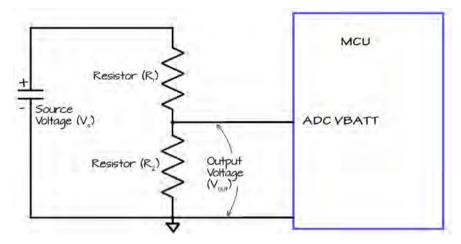

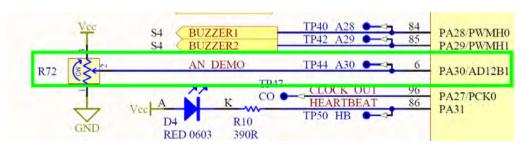

| 13.3 • EiE ADC Hardware                      | 460 |

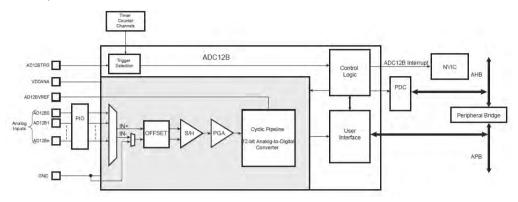

| 13.4 • SAM3U2 12-bit ADC Peripheral          | 460 |

| 13.4.1 • ADC Registers                       | 462 |

| 13.5 • EiE ADC Driver                        | 464 |

| 13.5.1 • ADC Initialization                  | 466 |

| 13.5.2 • ADC Interrupt                       | 467 |

| 13.5.3 • ADC State Machine                   | 468 |

| 13.6 • EIE ADC API                           | 468 |

| 13.6.1 • void Adc12AssignCallback( )         | 468 |

| 13.6.2 • bool Adc12StartConversion()         | 469 |

| 13.7 • Chapter Exercise                      | 470 |

| Chapter 14 • ANT Radio System                | 473 |

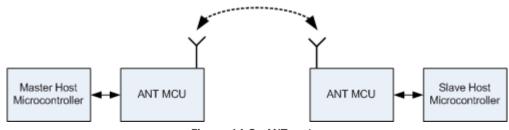

| 14.1 • ANT Wireless Radio                    | 474 |

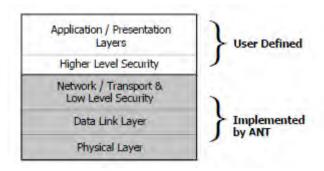

| 14.2 • Building the ANT Stack                | 475 |

| 14.2.1 • ANT Physical Layer                  | 476 |

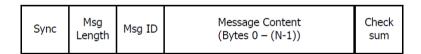

| 14.3 • ANT Message Protocol and Usage                            |

|------------------------------------------------------------------|

| 14.3.1 • ANT Protocol: Sections 1 thru 4477                      |

| 14.3.2 • ANT Protocol Section 5: Channel Parameters              |

| 14.3.3 • ANT Channel ID                                          |

| 14.3.4 • Transmit Data Types                                     |

| 14.3.5 • ANT Protocol Section 6: Pairing                         |

| 14.3.6 • ANT Protocol Section 7: ANT Interface                   |

| 14.3.7 • ANT Protocol Sections 8 and 9: Examples and Appendix483 |

| 14.4 • Message Handling                                          |

| 14.4.1 • Messaging with Channel Closed                           |

| 14.4.2 • Messages When Channel is Open                           |

| 14.5 • Debugging an ANT System                                   |

| 14.6 • Programming the ANT Sub-System                            |

| 14.6.1 • Firmware Design ant.c and ant_api.c                     |

| 14.6.2 • Data Structures                                         |

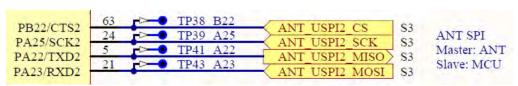

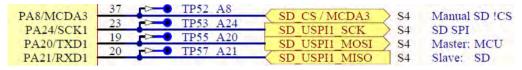

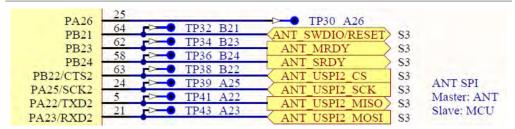

| 14.6.3 • Serial Drivers and ANT hardware interface               |

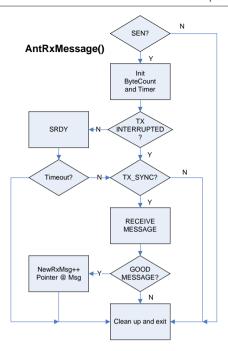

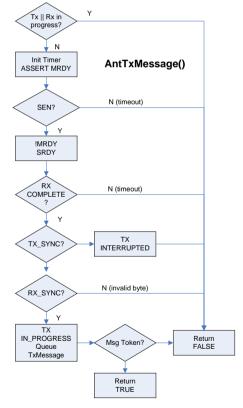

| 14.6.4 • Task access to send and receive                         |

| 14.6.5 • ANT_TICK and ANT_DATA518                                |

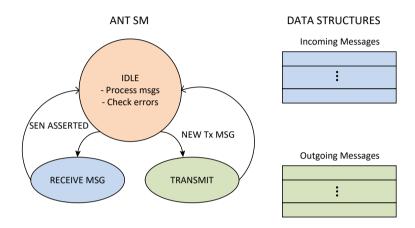

| 14.7 • ANT State Machine                                         |

| 14.7.1 • Initializing the ANT SM526                              |

| 14.8 • Implementing the ANT State Machine                        |

| 14.9 • API Summary                                               |

| 14.9.1 • ANT Configuration and Status Message533                 |

| 14.9.2 • ANT Data Messages                                       |

| 14.10 • Chapter Exercise                                         |

| 14.11 • Conclusion                                               |

| Glossary                                                         |

| Index 547                                                        |

#### **Preface**

Microcontrollers are everywhere in the world today providing intelligence to billions of electrical systems that people interact with – or don't interact with — every day.

Microcontrollers are programmed with firmware and combined into circuits to get their job done. These devices are what we call "Embedded Systems." Chances are any electronic device in use today contains at least one microcontroller, and complicated systems may have dozens of micros embedded in them to handle different tasks.

There are thousands of different microcontrollers to choose from. These choices can be sorted out rather quickly based on what you are looking to design. As you design more products, you will no doubt end up with some favorite microcontrollers that you become an expert at using. You will also likely design products for similar applications or with similar capabilities and therefore develop expertise in a particular field or application of microcontrollers.

What you should gather from that is that your own experience is unique, and what you know and how you have learned will always be different than the people you work with. The first four years of my own embedded experience started with programming PIC microcontrollers in assembly language where literally every byte of flash and RAM had to be used as effectively as possible. This shaped me into being very pragmatic and "low level" in my designs and thinking.

Even as I evolved to writing in C for 32-bit processors, my established fundamentals remained. I still think a lot about assembly language even when coding in C and strongly believe that a programmer should have a solid understanding of the instruction set of the processor being used. Though I can code in both C++ and Java, I have not done any commercial designs using those languages. However as you will see, I incorporate many of the concepts of high-level object-oriented programming in my C code albeit sometimes only by a written rule or process that I follow. I see more and more developers doing this.

The diversity in people's experiences is extremely important to recognize because it means that there are always opportunities to learn from and share what you know with other people. Collaboration is one of the greatest benefits of being alive, so open your mind and bring ideas together. Also, remember that in hindsight it is very easy to pick out elements of a design that can be improved – you should always do this with your own designs. If you do not find anything that you would do differently if you did it all over again, you probably are not looking hard enough.

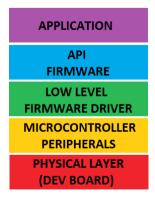

Embedded in Embedded tries to teach the fundamental, foundational concepts of embedded systems development as generically as possible. Indeed many of the concepts and processes that you will learn here can be applied to a variety of processors for a variety of applications. To provide a resource that is useful and with discussion of intricate details of design decisions, a specific processor on a specific development board with a specific development environment is used. I cannot stress enough that I totally understand that EiE is just ONE way, not THE way, of writing the drivers and programs that I will show you.

As with all engineering decisions, there are a vast number of tradeoffs when it comes to making decisions about how to complete a design, many of which will be discussed in this book as we come across them. In the firmware world, a general rule of thumb is that the easier and more robust or feature-rich a piece of code or application interface is to use, the more complicated the source code behind it will be.

A great example I like to use is comparing RS-232 to USB as standard serial interfaces. Simple RS-232 functionality can be written in just a few lines of code, but if you have ever had the pleasure of trying to get RS-232 serial devices to work properly on a

computer you will know how frustrating that can be. On the other end of the spectrum, there is USB, where a typical bare-bones driver on the embedded system will be at least 2kB of code. But USB is perhaps the epitome of plug-and-play, and computer users today expect nothing less than to plug in any USB device to any USB socket and immediately have a perfect operation.

With that in mind, we dive in to explore one way of writing a reasonably robust, reasonably small footprint, reasonably expandable, and reasonably multi-tasking embedded system. All based on the needs, resources, and knowledge at the time of writing. The ARM Cortex family of processors happens to be my current favorite, and for a variety of reasons, I designed the EiE development boards using Atmel's SAM3U2 Cortex-M3 microcontroller. I use IAR Systems IDE as I have used this for a long time across many different processors. For the record, I have never worked for ARM, Atmel/Microchip, IAR or any of the other vendors whose names you will see on the EiE hardware – every design decision I have made is based on my own experience with our research into the part or package that best meets the need of the design. Over time I have invited these companies into the EiE network for mutual benefit. For those that know me, you know that I am genuinely all about win-win.

You can use this book in one of four ways:

- Read it from start to finish developing all the code by yourself and comparing

it to the solutions provided. This is by far the most comprehensive approach.

Since the goal of the EiE program is to jump-start young engineers through the

first two years of working as an embedded developer, that is truly the way to

gain this experience.

- 2. Skim through and highlight what is important for you to know, or what might be important for upcoming projects. Reference the solutions provided and use the book's explanations to complement the code documentation.

- 3. Work backward from the application level and reference this book when you need or want to know the theory or decisions behind the code.

- 4. Choose specific chapters or topics of interest a la carte and use the book as a reference.

In every chapter you will see three icons that flag certain text:

Information. Use this icon to indicate some extra information relevant to the topic being discussed.

Do some work. Use this icon to indicate the reader should perform a task at this point.

This is massively important. Do not move past this point in the notes if you do not understand this yet.

It is my sincere hope that you get a lot out of this book and that it helps you gain skill as an embedded designer. If you love this system and adopt it (or parts of it) in your designs, that is great. If you hate this system and decide it is the best example of what never to do, that is great, too. There is as much value – or possibly more – in seeing what NOT to do as there is to seeing what to do.

In a world full of pre-developed solutions that people stitch together and call it "designed" I hope the story of this code shows how much thought and effort goes into making a system. Yes, we can patch together code and make use of work others have done, but when we design products for industry, how will these systems behave?

Will you understand your code next week, next month, or next year? Will your colleagues ever understand your code? How many bugs will your customers find? Do you understand the system you built and the tools you have to find and fix those bugs?

One thing I can say for sure is that after 18 years working with and teaching embedded systems, I know it is our processes that are most critical in being great developers, and if nothing else, this book will demonstrate the processes I rely on. To my knowledge, there are no other authors and/or engineers that have taken the time to go through and describe an entire development of a system as I will do here. Sharing this is a little like getting undressed in the middle of a crowded room... I hope you like what you see and find great value here!

Jason Long

#### **Chapter 1 • Getting started**

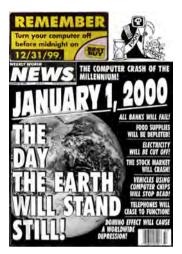

In 1999, the world was poised for what was thought was going to be the most significant disaster to hit the modern world: the "Y2K" computer bug. People everywhere were desperately trying to upgrade systems and test their computers to see if they would suffer from the bug. Yet even if every personal computer was safely protected, there was a great concern for all the embedded processors that were virtually everywhere and could not be reached in time.

Figure 1-1 "Y2K" magazine cover

Fortunately, the new millennium started with barely a flicker of the lights. Though some may argue that the problem was completely blown out of proportion, no one can contest that many of us were clued into the incredible impact that computers and embedded systems have on our lives. There are literally billions of microprocessors at work in our electronic devices. Everything from coffee makers, garage door openers, sprinkler systems and pop machines etc. have microprocessors these days – a high-end automobile has dozens of them and with the advent of self-driving cars, the computing power in a vehicle will increase massively. Estimates on the global value of embedded systems and the supporting industry are in excess of a trillion dollars.

Engineers working in this space know that technologies have grown linearly, but there has been exponential growth in awareness and application of embedded systems. The mainstream adoption of the term "Internet of Things" has brought embedded computing to a whole new level, just as the term "Cyberspace" ushered in the internet to the average person. The world is truly embedded in embedded systems!

This chapter takes you through some of the fundamental knowledge in embedded systems.

#### 1.1 • A Micro what?

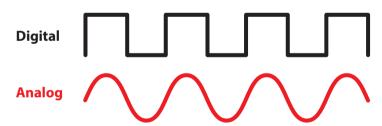

So, what are microprocessors and microcontrollers? Both are digital devices packed full of transistors that make up logic gates and data paths. By turning on or off combinations of those transistors, data can be accessed, processed and distributed throughout a device and to other devices that are connected in a circuit. This data can come from places such as memory, input/output lines, and from the processor core itself. All this is managed by the program (firmware) that is written and executed by the processor.

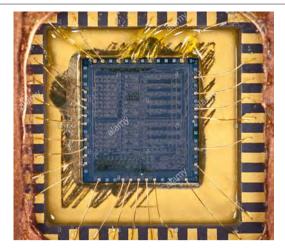

Figure 1-2 Example of a microprocessor

A microprocessor is the "core" where the instruction set of the processor lives and performs calculations. A core needs to be attached to external memory and other peripherals if it is going to be useful. It talks to RAM where programs and data are stored, communicates to the display to show you what is going on, processes the bytes that play music and sounds, and exchanges information with data storage devices. It is the main brain of an electronic device, just like the processor in a desktop PC or smartphone.

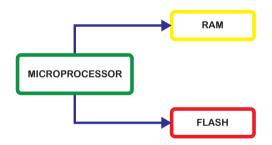

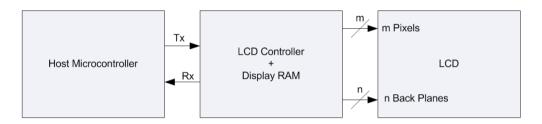

Figure 1-3 Microprocessor communicates with external memory

A microcontroller is an integrated circuit that contains a microprocessor, but also may have onboard memory, timers, communications peripherals, analog to digital converters, and many others. The microcontroller can usually run on its own with barely any external devices connected to it, though it still needs to be in a circuit to control. Literally billions of electronics in the world are microcontroller-based embedded systems.

Figure 1-4 Microcontroller-based embedded system

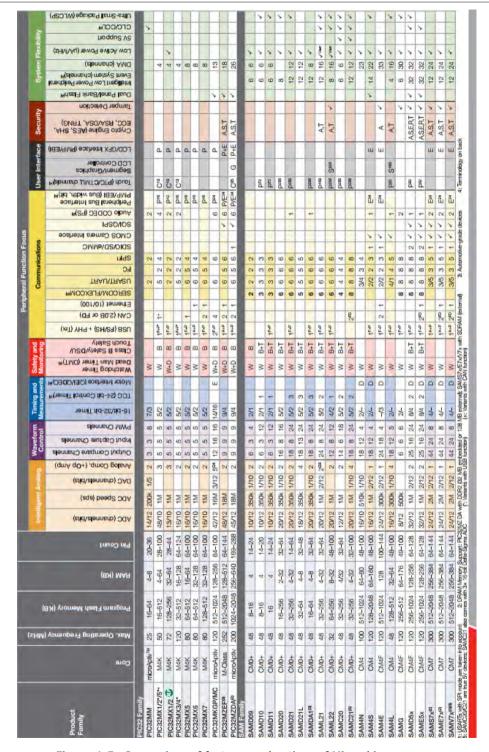

Figure 1-5 Comparison of features and options of Microchip processors

Since everything is integrated on a single chip, a microcontroller-based system is more resource-limited than a microprocessor-based system that could have practically unlimited volatile and non-volatile memory attached. Even high-end microcontrollers max out around 2MB of non-volatile flash and 1MB of RAM and have clock speeds topping out at 200MHz. That might not sound like a lot compared to microprocessor systems with capabilities and resources order of magnitudes higher, and it's also a great way to date this book since advances are always being made. However, what you can do with even an 8-bit microcontroller with 1kB of flash and 100 bytes of RAM is still amazing. Microcontrollers tend to be simpler to work with, easier for hardware design, and are inherently less expensive.

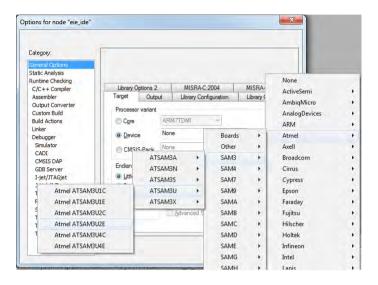

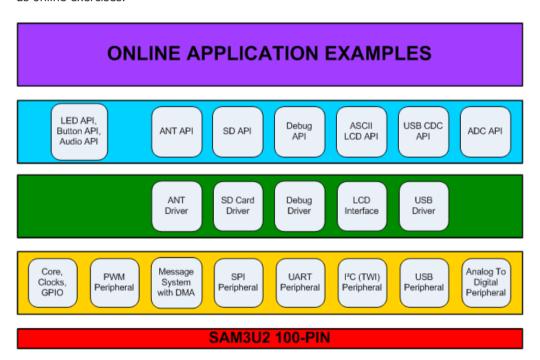

Embedded in Embedded uses the SAM3U2 Cortex-M3 microcontroller from Atmel (which is now Microchip after being acquired in 2016). Like any vendor who provides an ARM-based microcontroller, Microchip licensed the ARM core and added peripherals to build its device. The SAM3U2 is just one of several devices in the SAM3U family, which in turn is one of the many Cortex-M3 processors available from Microchip. A Cortex-M3 core provides plenty of power to run our development board and for most of the time, it will be busy sleeping doing nothing at all. The specific device does not really matter for EiE since our goal is to teach the process of design.

So how do you navigate all the processor options to decide on the right one to use in a design? There are many factors and there is no simple formula to put in some parameters and crank out the answer. Likely the biggest deciding factor will be your own experience. The investment you make in learning how to use a particular family of microcontroller might be the most valuable part of the equation, though being open to change is good if it makes sense. If you are new to embedded design or faced with a design where your "toolbox" of available knowledge does not provide any solutions, then you are limited to searching on your own or consulting a colleague or reputable distributor to get advice. As you gain experience, you can more quickly identify what you may or may not need for features and capabilities.

Learning a new microcontroller is exciting, but even industry experts will experience a learning curve if they change platforms to something entirely new. "Time to market" is one of the timeless mantras in engineering, so it is inherently a good idea to minimize new learning in a product and maximize reusability. Easier said than done and you will find an almost infinite number of variables to consider. Cost, power consumption, and available peripherals are very important. A strategy that we have found successful for specifying a micro for a new product is to aim for around 50% total resource usage for the part you choose and ensure there is at least one part in the family that you could scale to further double the resources. For example, if you think you need 32kB of flash and 8kB of RAM for your product, we would suggest starting with a processor that has 64kB of flash and 16kB of RAM available. Within the family, there should be drop-in parts with 128kB of flash and 32kB of RAM.

The physical size of the chip is another factor. If you prepare a block diagram and decide you need 30 input/output pins, you probably want to have at least 10 spares. If you are upgrading an existing design, the margins can be much tighter. No doubt it is difficult to predict what you might need 2-3 years down the road, but a good brainstorming session of "what features will Marketing think of" is a good way to think outside of the box to anticipate reasonable growth of the product.

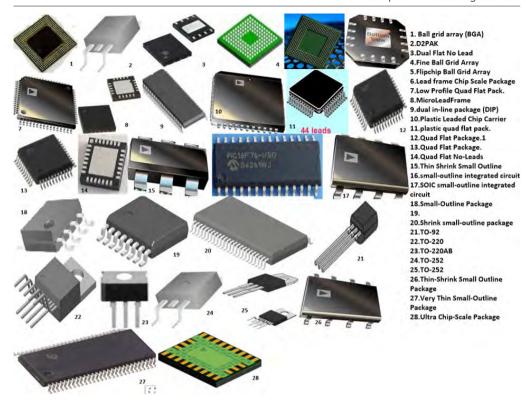

Figure 1-6 Examples of various component packages

One of the nice things about using an ARM-based microcontroller is that if you run out of power, you can migrate to a more powerful core like the Cortex-M4 or all the way up to an applications processor. If you need less power, then you can downgrade within the portfolio to the Cortex-M0. Since all the processors are built with very similar architecture, you can change quite freely and the underlying concepts plus all your development tools and knowledge remain applicable. While we do love ARM processors, that does not mean we use them exclusively. There are plenty of applications where we will look at an 8-bit or 16-bit solution if the requirements make sense to do so.

The Cortex family also attempts to make porting between different vendors as easy as possible. ARM developed a standard for Cortex devices called CMSIS – Cortex Microcontroller Software Interface Standard. It is growing in complexity but the portion relevant to us is the CMSIS-CORE. This part of the standard provides an interface to the ARM core and the core peripherals. Vendors also use the CMSIS pointer-to-struct style for accessing the microcontroller peripherals that they add. The exact register names and organization is different between vendors, but at least the main organization is the same.

Figure 1-7 Cortex microcontroller software interface standard

For example, ST has a nice family of Cortex-M3 and Cortex-M4 processors not to mention some very low-cost development boards, so you might be interested in taking some of the code from EiE to an ST micro. Porting high-level code is very simple since it has

been designed with a high degree of hardware abstraction, but porting peripheral drivers will require a lot of peripheral-specific re-write. In fact, the EiE firmware system started as a product-specific version of that code on an ST Cortex-M3 way back in 2008. This was ported to an LPC2148 ARM7 and then an LPC1752 Cortex-M3 where the code was further developed. The SAM3U2 was chosen in 2013 for final development because it had the perfect hardware peripherals and pin count that we needed for EiE and was also compatible with Segger programmer firmware.

The ST to NXP move inspired us to better layer the code and abstract each task, and when we later ported to the SAM3U2 it was a lot easier, though still took many weeks. We re-used a lot of the code structure and in some cases just had to determine the names of registers that were different. That being said, writing a firmware system with portability to other vendors is probably not an appropriate level of effort to expend, though it all depends on what you want to accomplish.

Figure 1-8 Cortex-M3 processors

#### 1.2 • The 32-bit Processor

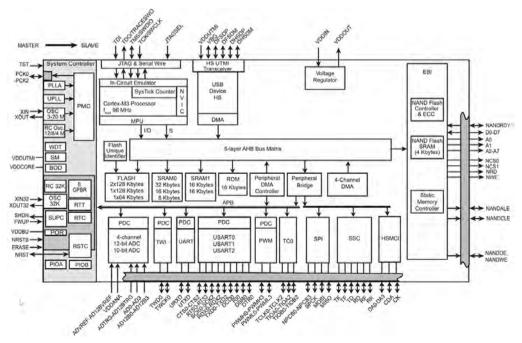

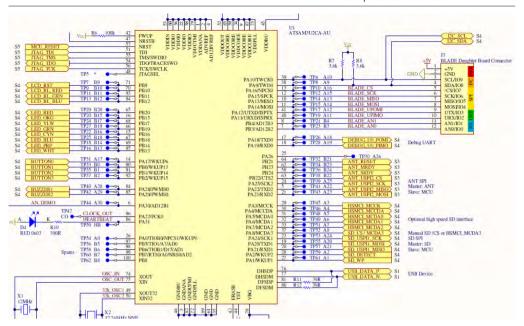

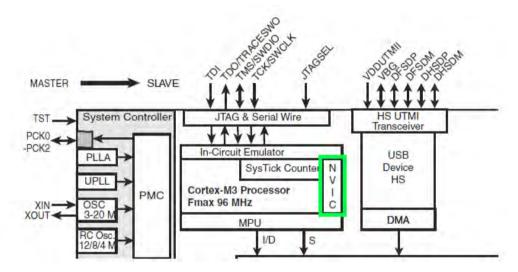

We have already mentioned that a microcontroller has many onboard peripherals that it uses to operate. The microcontroller attaches to the physical world through its IO pins, many of which are connected to the internal peripheral blocks that provide other capabilities to the processor. The figure below is the block diagram of the SAM3U2. Note all the different peripherals, memory, buses, and connections.

Figure 1-9 100-pin SAM3U4/2/1C block diagram

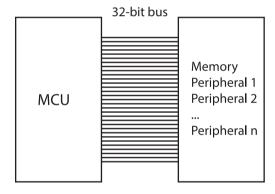

Even though these peripherals are built-in, they still require a physical connection over which they exchange data. This communication is done over a set of connections called a "bus." In the diagram above, you can see two buses: AHB (Advanced High-speed Bus) and APB (Advanced Peripheral Bus). Depending on the processor architecture, there may be multiple buses for different purposes such as for instructions, data, and peripheral access. There are historically two different architectures: Harvard (single bus for instructions and data) and Von Neumann (separate data and instruction buses). The Cortex-M3 family happens to be Harvard architecture. A designer practically never worries about the type of architecture of a processor – the implementation ends up being transparent unless the requirements of the device are very specific for some reason. The Wikipedia page on ARM Cortex-M provides a wealth of information if you are interested (https://en.wikipedia.org/wiki/ARM\_Cortex-M).

The main bus on a SAM3U2 is 32 bits wide. In other words, there are 32 wires that connect the area where the program runs with the other parts of the system. This also means that the main registers and memory locations can be 32-bits wide. The native data size is typically called "word" size. Microcontrollers also come in 8 and 16-bit versions. Desktop PCs use 64-bit processors these days. The transition from 32-bit PCs started around the Pentium-4 processor. At the time of writing, there are not any well-known 64-bit microcontrollers, though there are a growing number of dual-core embedded micros entering the market that feature a higher end core like a Cortex-M4 paired with a lower power Cortex-M0.

Figure 1-10 32-bit bus and addressing

An 8-bit processor can do many of the same things as a 32-bit processor, but any time an operation requires numbers larger than 255, an 8-bit processor must complete tasks in pieces. Data transfer is also limited by the smaller bus size. If you want to add two 16-bit numbers on an 8-bit processor, you must take several steps to add the low bytes, watch for a carry bit, then add the high bytes and the carry bit (and watch for a carry bit there, as well). Another important consideration is that there is a limitation on the amount of memory that can be accessed directly. If the data bus is only 8-bits, then only 255 bytes of memory can be addressed directly, although there are lots of ways to add additional addressing bits. A 32-bit processor can inherently access over 4GB of memory.

#### 1.3 • Microcontroller Programs

No matter what programming language is used to write a program (for example C or C++), the source code is compiled into the assembly language for the specific processor that will run the code. Programs may also be written directly in Assembler. Assembly language works with the collection of instructions that a processor knows how to process which is called the "instruction set." All Cortex-M3 processors use the same instruction set

regardless of the vendor's microcontroller they are in.

The instructions and arguments in an assembly language program are converted into "opcodes" and saved to a hex (hexadecimal) file by the Assembler. Assembling is a much simpler process than Compiling and every developer's software Assembler should come up with the same hex file for a given program. The hex file is a bunch of addresses, data, and some error checking/checksum information. The 1's and 0's of the opcodes will be loaded into a processor's memory at the specified addresses and eventually be executed one-by-one when the core starts running.

There are various formats that this file can have, with one of the most common being "Intel Hex."

```

Intel Hex file: : num bytes address record type data checksum

:10080000042CFF3FFF3FFF3F8801762F8B1378308A

:100810002100990087318E2784318731AA278431BE

:1008200087319D2784318731B42784318B1700307D

:1008300087315D2784312000A0002008D1005108B5

```

Figure 1-11 Intel Hex file

The example below is a hex file for a program that turns on a light if a button is pressed on a certain microcontroller.

#### Listing 1-1

```

:02000004000FA

:10000000831601308600831206188610061C86149B

:020010000428C2

:00000001FF

```

The hex file needs to be programmed in a microcontroller's non-volatile memory. Most micros these days use "flash" memory that is both electrically writeable and readable hundreds of thousands of times. This makes learning and testing easy because the chip can be continually reprogrammed until the code works properly. Flash memory replaced EEPROM (Electrically Erasable Programmable Read Only Memory) in most microcontrollers in the late 1990s due to cost. EEPROM is nice because individual bytes can be erased, whereas flash memory is typically organized in large pages that must be erased. Both can write individual bytes so in most cases it's not a big deal. Some microcontrollers have a small EEPROM peripheral that is very handy for saving user information.

At the other end of the spectrum are processors that are one-time programmable (OTP) so you better do some serious debugging before you download your program as you get one chance only. Somewhere in the middle are EPROM's (Electrically Programmable Read Only Memory) that can be easily programmed but can only be erased by shining UV light through a small window on the chips for 15 – 20 minutes which tends not to be very convenient.

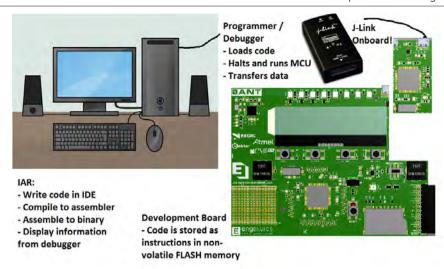

To write a program you code to a processor's non-volatile memory, you need some sort of programming tool. Many microcontrollers use a standardized interface commonly referred to as "JTAG" to move a program from the computer on which it is developed to the embedded system. MCUs can be both programmed and debugged through JTAG. JTAG devices are separate pieces of hardware that are usually called "programmers" or "debuggers." A common tool is called a "J-Link" from Segger.

Figure 1-12 Programming tool chain

JTAG programmers/debuggers can be expensive. Serial programming devices are low-cost and can also be used to program but not debug a microcontroller. Serial programming requires the processor to support on-chip programming and have some type of "bootloader" program that runs outside of the programmed memory space. A processor vendor might provide this, or it can be designed into the system.

Regardless of how the connection is made, the act of programming is what physically drives the high and low voltage levels into the target microcontroller. Once the code is programmed in non-volatile memory, it can stay there for over 100 years!

Development boards typically have a JTAG device built-in since programming and debugging is the whole purpose of the board. The second SAM3U2 processor on the EiE main development board is the programmer called a J-Link Onboard (OB). The J-Link OB firmware license is purchased and loaded in the factory. The programmer is connected to a PC and the signal chain is complete.

It would be much too costly to add a programmer to every production device, so most products are designed with a connector to attach the programmer. This allows the developer to write and test code and gives the factory access to program the device during manufacturing. A programming header can consume a lot of space and add cost to each board. The standard JTAG header is a huge 2x10 box-connector. A much smaller standard connector was defined for Cortex parts, but it is quite expensive and from our own experience has not been widely adopted.

Figure 1-13 J-Link programmer and board connectors

Companies will often develop a proprietary connection that works well for their product line. One of our favorites is the "Tag-Connect" system that requires only a footprint on the PCB that a special cable securely attaches to.

Figure 1-14 Tag-Connect system

Cortex microcontrollers support a two-wire programming and debugging interface. With a bit of hacking, you can use a standard USB physical connection. This has nothing to do with USB data - it is just the physical connector. Be aware if you are designing consumer products, re-purposing a USB connector can lead to some confused customers. If the connector is used only for power by the consumer, then it might be ok.

Figure 1-15 USB pinouts

All custom solutions will still require an adapter to plug into a JTAG device. We designed a special J-Link adapter that can be used to connect to any of these options and our own open source solution that is a nice balance of size, cost, and can provide additional UART debugging access.

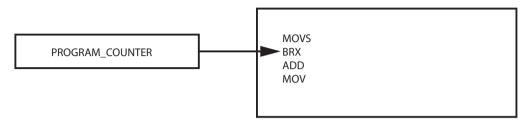

Figure 1-16 Engenuics programming interface adapter

Once the microcontroller is programmed, the code is ready to execute as soon as the power is turned on or the processor is reset to kick it out of programming mode and into execution mode. A program runs by executing each instruction sequentially via a special pointer called the Program Counter (PC) that indexes and reads out each instruction from memory to the bus. The PC always starts at 0 when the device powers on and increments after each instruction with every full clock cycle. Unless an instruction tells the PC to branch or jump, it will keep incrementing to the next address in memory.

Figure 1-17 Special pointer "Progam\_Counter"

On a 32-bit processor, the program counter increments by 32 bits (0x04). Many instructions on 32-bit Cortex parts are only 16-bits (called the "Thumb-2" instruction set), so program memory storage can be up to 2x more efficient in some cases. In practice, many instructions end up taking two 16-bit locations, so the net result is less than 2x efficient.

Sometimes an instruction will cause the program counter to change by some number other than the next sequential amount, so it will jump to run instructions from a different part of the program memory. This is how function calls and branches are performed. When the program reaches the end of the programmed memory, you want to ensure that it returns to the beginning with a branch instruction. Otherwise, because of the way the address space in the ARM is set up, it will keep addressing memory and could start doing crazy things like putting the contents of your RAM memory onto the local bus to execute as opcodes. There is nothing stopping you from doing that on purpose and running code from RAM.

The basic operation of a processor and the corresponding flow of data can be understood if you remember a few key points:

- There are 4 steps required to carry out an instruction: Fetch, Decode, Execute, and Writeback. Simple processors can often run one instruction step per clock cycle, and each instruction is pipelined so the fetch of instruction 2 happens on the same clock tick as the decode of instruction 1. In a processor like the Cortex-M3, most instructions require multiple clock cycles, but they still follow the general fetch, decode, execute, writeback flow.

- 2. Microcontrollers are digital systems: signals on the bus are merely logic level highs and lows that are momentarily present at discrete locations and are advanced through the system's logic gates with every cycle of the system clock. Signals propagate through basic logic gates as fast as the electrons can move. Eventually, they get stopped and held at circuits called flip-flops until the next clock signal. The maximum clock speed is determined by the worst-case delay through the logic, so the systems assure that the correct signals are waiting at the flip-flops before being advanced to the next set of logic.

#### 1.4 • The Clock

The clock signal is fundamental to a digital system. It can be generated in a variety of different ways and most processors will support several different clock sources including some that are built-in and require no external components. In low-cost embedded systems, external clocks are typically a resistor-capacitor circuit which would cost less than a penny. Systems requiring greater precision can use other types of oscillators. Crystals are the most popular choice as they are very precise (typically 30-40ppm) and generally do not drift over power supply ranges, temperature or other operating conditions. At around 50 cents, they are very expensive compared to a simple RC circuit. Crystals also take up more board space and usually require two capacitors that must be carefully selected to make the crystal oscillate at the correct frequency.

Figure 1-18 Crystal oscillators

During the final review time of this book, we came across some amazing little oscillators from a company called SiTime. These are tiny devices (1.54mm x 0.84mm) and don't require any external components. They advertise better stability and lower power than crystals, and magically cost roughly the same. Many different frequencies are available. We won't have a chance to test them before this goes to print, but if they're as good as advertised this will quickly become a big favorite in our designs.

Figure 1-19 SiTime oscillator package

The clock frequency of a resistor and capacitor circuit is at the mercy of the component tolerances, temperature, and supply voltage. The speed of an RC oscillator is simply 1 over the RC time constant. For example, a 20 k $\Omega$  resistor with a 100 pF capacitor would yield a 500 kHz clock:

$$\tau = RC$$

$$\tau = 20 \cdot 10^{3} \times 100 \cdot 10^{-12}$$

$$\tau = 2\mu s$$

$$f_{osc} = \frac{1}{\tau} = \frac{1}{2 \cdot 10^{-6}} = 500kHz$$

Processors that have built-in RC oscillators are specially "trimmed" in the factory so they are nominally quite good, but will still never compare to a crystal. If the processor supports the use of an external RC oscillator, then the range of frequencies and, to a degree, the precision and stability of the clock can be controlled by the designer. There is some internal hardware required for an RC oscillator which will only work to a maximum frequency on the order of 1MHz. Crystals usually start at 1MHz, except for watch crystals that have a very specific frequency of 32.768kHz and happen to be very common in embedded applications where low power and precise timing is required.

Processors often support clock selection and may have both a slow RC or crystal clock source and a high-speed crystal input. The slow clock is used for sleeping or other low-power, non-urgent functions, but the fast clock can be activated for high-speed processing or functions that require precise timing if the slow clock is an RC source or just too slow.

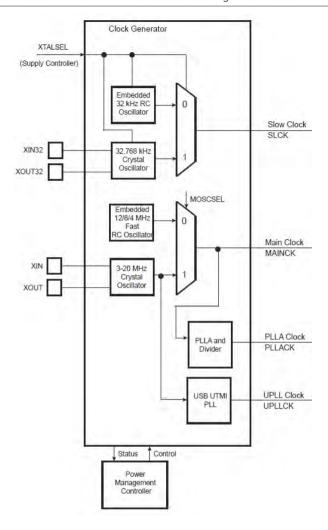

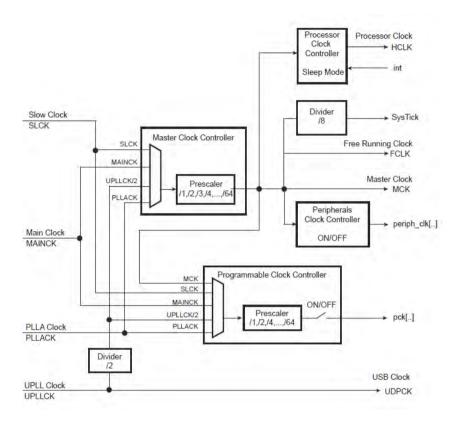

The SAM3U has a maximum clock speed of 96 MHz. The base clock is sourced from one of two crystal oscillator sources or an onboard RC. The internal RC is what the processor always starts up on. The micro offers a phase-locked loop (PLL) that can take whatever base clock signal is provided and up-convert it to a faster frequency with the same precision as the source crystal. On the EiE development board, the base clock signal is a 12.000 MHz crystal which feeds the PLL to provide a 48MHz main clock. 48MHz is chosen as it is the required speed for USB function.

Compared to today's PC and smartphone processors that are running at GHz clock speeds, an embedded processor at less than 100MHz might not seem very fast at all. However, embedded systems where microcontrollers are used rarely require high-speeds especially if they do not have to support a graphics display or high-speed external communications like Ethernet or USB. In fact, many microcontrollers are deliberately set to run at much slower speeds because they simply do not need to go faster. The slower a micro runs, the less power it consumes, and designers are often very happy to trade speed for power consumption especially in battery-powered devices. The design of the processor plays an important role, as well. An intelligently designed instruction set like the ARM core can accomplish tasks faster by adding logic to the instruction that carries out operations as the instruction is executed such as incrementing or decrementing values or pointers, conditionally branching or executing, and toggling flags.

Even if you examined clock speed on its own, is a 48 MHz system really that slow? Consider a processor's clock running 48 times slower at 1 MHz and assume that an instruction can be executed at the end of each cycle. That means that 1 million instructions are being executed every second! Alternatively, you can look at it from the view of a single instruction period. Period T is the inverse of frequency f:

$$T = \frac{1}{f}$$

where T is in seconds and f is in Hz. So.

$$T = \frac{1}{1.10^6} = 1 \mu s$$

This means that the period of a 1 MHz clock tick is only 1 microsecond (1 millionth of a second). Considering a program can evaluate an input and make a decision in 8 to 10 clock cycles, only 10 microseconds are needed to do something useful. Granted, there are some things that can take hundreds or even thousands of instructions, but MHz speeds are fast enough to handle most embedded applications and the system will still spend most of its time in a low power sleep state.

#### 1.5 • The Fundamentals

There are some important basics that you need to have on which you will build your embedded design skills. Some of this material you already know but make sure you review it. Other parts you think you know from the theory taught in school, but it can catch you once you apply it to a real circuit. Some of this material will be brand new. Whatever the case, a solid understanding of these fundamentals is essential to the embedded engineer.

#### 1.5.1 • Number Systems

We are all used to the base-10 number system that we use in our everyday lives. A base-10 system makes calculations very simple. When working with embedded systems, it becomes convenient to make use of alternative number systems like binary, octal and hexadecimal – base-2 (binary), base-8 (octal) and base-16 (hexadecimal) systems, respectively. If you are fluent in converting between the different systems, you can improve your success or at least your speed in programming.

A simple way to describe a system base is the quantity you count before rolling over to the next digit. In decimal, we count to 9 in the "ones" position and roll over to 10 – the "tens" position becomes 1, and the "ones" position goes back to zero. Each digit position is a power of 10 (starting with  $10^{\circ} = 1$ ). So the one's position is  $10^{\circ}$ , tens position is  $10^{\circ}$ , hundreds position is  $10^{\circ}$ , and so on. A base-10 system has 10 possible digits in each position, from 0 to 9. The digit in the position multiplies the power of 10, and the sum of all the digits and their positions is the number itself. That is way more complicated to explain than it is, so check out this quick example to ensure you understand.

Consider the number 709. Break it down into the sum of the all digits and their powers of 10:

$$(7 \times 10^{2}) + (0 \times 10^{1}) + (9 \times 10^{0})$$

=  $(7 \times 100) + (0 \times 10) + (9 \times 1)$

=  $700 + 0 + 9$

=  $709$

Working with a base other than 10 uses the same concepts but it's a bit difficult because you are not used to it. For the base-2 binary system, you have only digits 0 and 1. The digits in a binary number are typically referred to as "bits". The lowest value bit is bit 0 and is called the Least Significant Bit or LSB. The highest bit in a binary number is the Most Significant Bit or MSB. Of course, 8-bits make a byte and you might have heard that 4 bits are a nibble.

The EiE notation for binary numbers is b'nnnnnnn' where n is 0 or 1. On an 8-bit processor, we only have bit positions 0, 1, ..., 7. When you look at a binary number, the LSB is on the far right.

| Name:       | MSB |   |   |   |   |   |   | LSB |

|-------------|-----|---|---|---|---|---|---|-----|

| Bit number: | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

| Example:    | 1   | 1 | 0 | 1 | 0 | 0 | 0 | 1   |

A number in binary is built using the same rules as building a base-10 number, except the multipliers are only ever 0 or 1, and the powers are those of 2. As a result, binary numbers have more digits than decimal numbers when representing the same value. When converting binary numbers to decimal, the mechanics of the operation are the same.

Consider the number 145, which in binary is b'10010001'. Break it down into the sum of the digits and powers of 2:

$$(1 \times 2^7) + (1 \times 2^4) + (1 \times 2^0)$$

=  $(1 \times 128) + (1 \times 16) + (1 \times 1)$

=  $128 + 16 + 1$

=  $145$

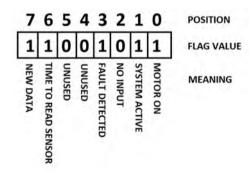

Binary representation is commonly used when programming microcontrollers because so much functionality is based on individual bits. Even though there may be a group of bits stored in a memory location, the processor or program may only look at certain bits to make a decision or manage a process.

An example is with something we call a flag register which is a memory location that a programmer might allocate to use the individual bits to track events in a program. Set bit 1 if a user pressed a button. Set bit 2 if data is ready from a peripheral. Set bit 3 if a certain event occurred. Keeping track of these three items is done simply by toggling the corresponding bit. If the program is being debugged and the programmer wants to know what flags are set, the memory location is displayed in binary so it will be easy to see what flags are set. The meaning of each flag bit is entirely independent of the other bits in the byte, and totally arbitrary based on the programmer's defined (and hopefully documented) choice.

Figure 1-20 Example flag register

A problem with working in binary is that large numbers are difficult to look at. Some compilers do not recognize binary numbers. Therefore, it makes a lot of sense to use hexadecimal numbers. The EiE notation for a hex number is "0x" followed by the value, like 0x42. Some people prefer a trailing 'h' like 42h. We almost always shorten "hexadecimal" to just "hex."

The base-16 hexadecimal system counts from 0 to 9 and then uses letters A through F to count another 6 values before rolling to the next digit. Since a larger quantity can be stored in each digit position, hexadecimal numbers have fewer digits than decimal numbers. Conversion to decimal is done in the same way, this time multiplying powers of 16 by coefficients 0 thru F, where A, B, C, D, E, F are 10, 11, 12, 13, 14, and 15, respectively.

Consider the number 499 which in hex is 0x1F3. Break it down into the sum of the digits and powers of 16:

$$(1 \times 16^2) + (15 \times 16^1) + (3 \times 16^0)$$

=  $(1 \times 256) + (15 \times 16) + (3 \times 1)$

=  $256 + 240 + 3$

=  $499$

Converting hex to decimal and vice-versa is not done very often, but converting between binary and hex is. Hex to binary conversion is performed one hex digit at a time by inspection into groups of 4 bits:

$$0x1F3 = b'0001 1111 0011'$$

Binary to hex is done by grouping 4 bits starting with the LSB and simply reading the result. Work right to left, and pad zeroes to the MSB to 4 binary digits. It is helpful to make the 4-bit groups easier to see by adding spaces:

```

b'11001001111110' = 0001 1001 0011 1110 = 0x193E

```

On an 8-bit system, the maximum hex value is 0xFF, which corresponds to 255 or b'11111111'. Base-16 numbers are the most-used number system in embedded programming – even more than decimal. The nature of working with an embedded system makes this a necessity. The whole art of making a system work really boils down to moving bits around, and the best way to show a bunch of bits is in hex. Doing so allows the programmer to see memory locations exactly the way they are stored on the actual hardware. Hex is obviously more compact than binary, and most often hex representation will show you what you need. Going back to the flag register example, that same byte displayed in hex is easy enough to translate in your head to determine what flags are set. For example, how quickly can you tell which of the flags are set if you read "0x5" in a memory location? You should see that bits 0 and 2 are set in this case.

You will find that you use decimal, binary and hex throughout an embedded programming design and you will see how they each play important roles. Octal (base-8) numbers rarely come up in our experience, so we will purposely neglect to discuss them. You will develop some preferences in your debugging for what representation you like most for certain situations. Make sure you configure the debugger to display the values in the form that makes the most sense when you look at different variables.

| Variable       | Value      | Location | Туре |

|----------------|------------|----------|------|

| bInputDetected | FALSE      | R0       | bool |

| u32Counter     | 159900     | R1       | u32  |

| u8Flags        | 0b10100100 | R2       | u8   |

| u32RegValue    | 0x7A30F1B4 | R3       | u32  |

Figure 1-21 Debugger display numerical values

The faster you can translate between number systems the better, as you often need to determine "what a number means" quickly. For example, you might have a counter that you can see in memory that is shown in hex. Rather than changing the display settings, it would be quicker to know by inspection that "0x7f" is 127 and thus the counter's 6th bit is about to overflow. Doing quick translations like that in your head is handy. Practice being really fast with values from 0 to 15.

Table 1-1 Decimal, binary and hexidecimal conversion

| Decimal | Binary   | Hex  |

|---------|----------|------|

| 0       | b'0000'  | 0x0  |

| 1       | b'0001'  | 0x1  |

| 2       | b'0010'  | 0x2  |

| 3       | b'0011'  | 0x3  |

| 4       | b'0100'  | 0x4  |

| 5       | b'0101'  | 0x5  |

| 6       | b'0110'  | 0x6  |

| 7       | b'0111'  | 0x7  |

| 8       | b'1000'  | 0x8  |

| 9       | b'1001'  | 0x9  |

| 10      | b'1010'  | 0xA  |

| 11      | b'1011'  | 0xB  |

| 12      | b'1100'  | 0xC  |

| 13      | b'1101'  | 0xD  |

| 14      | b'1110'  | 0xE  |

| 15      | b'1111'  | 0xF  |

| 16      | b'10000' | 0x10 |

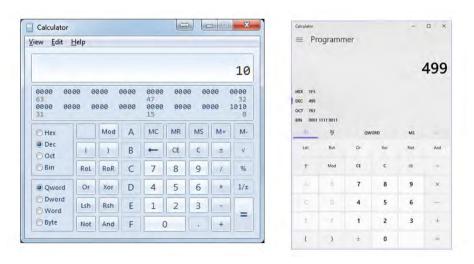

Windows Calculator is a very useful tool for embedded systems programmers. It has a "Programmer" mode that lets you quickly make conversions. We'd argue the Windows 7 version (left) is nicer than the Windows 10 version (right).

Figure 1-22 Windows 7 and Windows 10 calculator

#### 1.5.2 • Ohm's Law

One of the first electronic equations you should learn or probably learned already is Ohm's law. Even if you never design hardware, keep Ohm's law in mind if you are working with a piece of hardware to prevent yourself from doing anything that might break the board. If you do not know it, then be sure to add it into your repertoire of electronics skills. Ohm showed that:

$$V = IR$$

where,

V = voltage in volts

I = current in amperes

R = resistance in Ohms

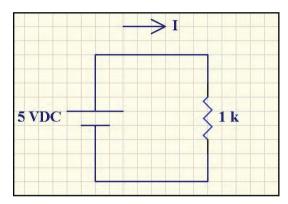

A simple example of Ohm's law is shown:

Find current I in the circuit

$$V = IR$$

$$I = \frac{V}{R}$$

$$I = \frac{5V}{1000\Omega} = 5mA$$

Figure 1-23 Finding the current in a circuit

In most embedded applications that a firmware designer is working with, voltage and current are DC, so no time-varying signals have to be considered. Ohm's Law is linear and presents no challenges when using it to analyze a circuit. However, experience tends to show that everyone knows Ohm's law until they get into the lab and build a real circuit. Remember that even a piece of wire has a finite resistance, so Ohm's law still holds true when you accidentally short your power supply.

To avoid any human-based experiments, consider what happens if you take a wire and put it across a 9V battery. What would the voltage at the terminals measure? Or perhaps the better question, could you measure the voltage before the wire melts? The answer is that the battery itself has an internal resistance that is in series with the tiny resistance of the wire. The voltage of the battery will drop low enough to ensure Ohm's Law is holding true for the amount of current that the battery can deliver through the battery resistance and the load. This is amps of current, so it is not a good idea to try. Likewise, it is not a good idea to carry a 9V battery in your pocket with your keys.

This concept is one of the things that gets people new to electronics most often when adding a load to a power supply. As with the battery example, the load that you are attempting to power is fixed and has some resistance. Therefore, the current in the circuit is going to be set based on the power supply and load. There will always be some variation in the measured power supply output depending on the load current and how

the supply adjusts - therefore we have transient responses to changing loads.

Power supplies that limit current can do so in one of two ways: increase their impedance or lower their voltage. A shorted battery drops its terminal voltage if the load is trying to draw more current than the supply can source (internally, the voltage is dropping across the resistance of the battery cell). A good lab power supply will increase its resistance to limit the current to a safe level you set. In either case, the voltage you measure at the terminals of the supply will not be what you might expect because of Ohm's Law. In any case, even outside of the extremes, Ohm's Law is at work and the power supply is changing in internal resistance to maintain current. Even a "current source" supply (it is hard to come across a current source – most power supplies look like voltage sources) will operate following Ohm's Law and will crank up the voltage to maintain a constant current. LED drivers are a great example of this.

Keep these points in mind when you are building circuits:

- 1. Make sure you know all the V's and R's in your circuit before you turn the power on. Do you have any low-impedance paths to ground? LEDs without current-limiting resistors are good examples.

- 2. ALWAYS limit the power supply current to your device. Rarely does a microcontroller circuit require more than 100 mA. If you limit your supply to this amount, the chance of accidentally damaging something in your circuit or in the supply itself is minimal even if you have dead shorts to ground. If you do not know how to current limit a power supply, ask!

- 3. Remember your load "draws" current from the supply. If you try to draw too much current, the power supply voltage will likely drop as Ohm's law prevails!

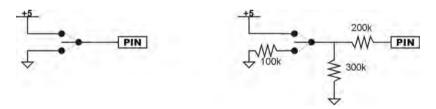

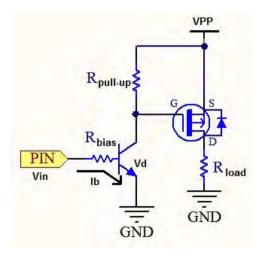

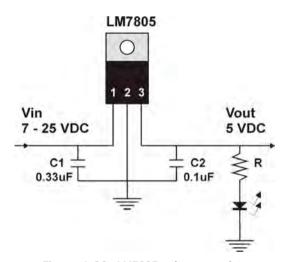

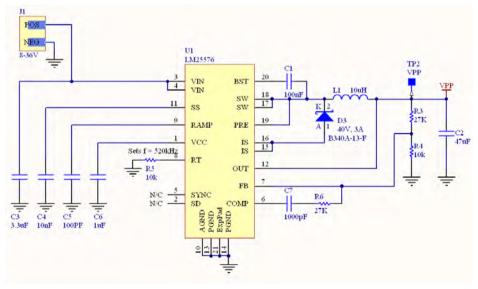

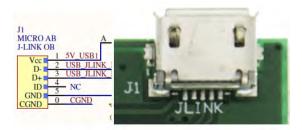

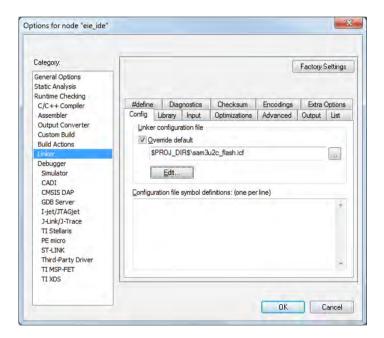

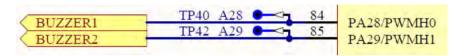

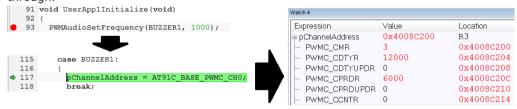

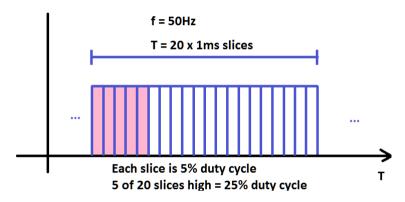

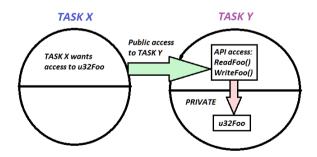

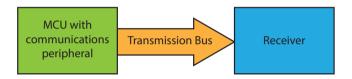

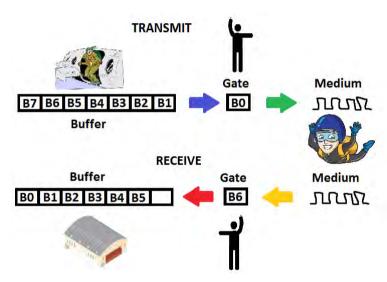

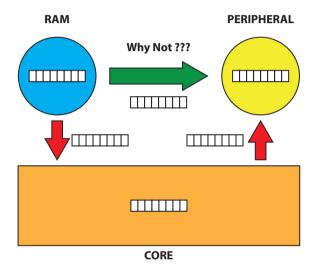

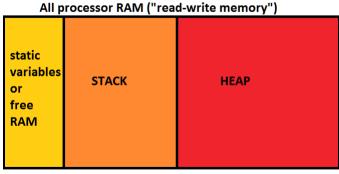

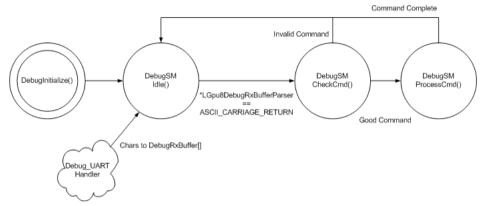

#### 1.6 • Switches