**Dual-Core Programming**

Parallel Programming with a Raspberry Pi Pico

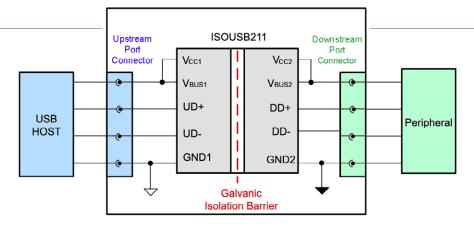

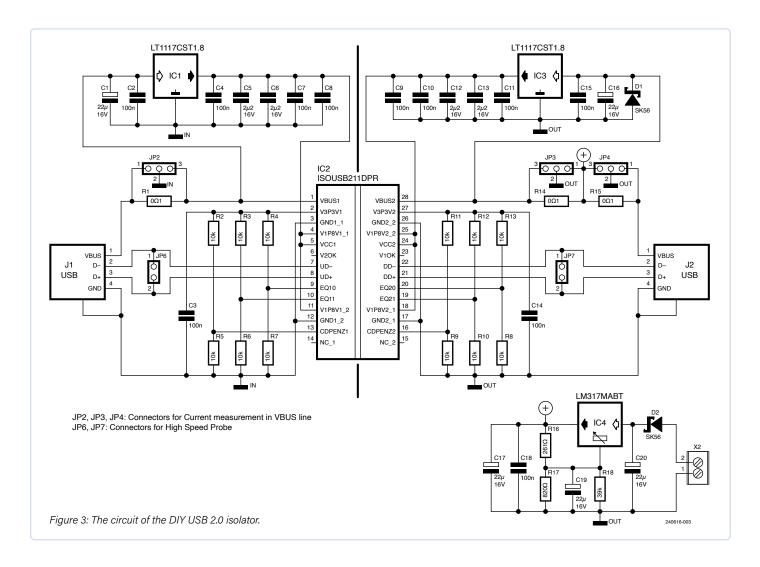

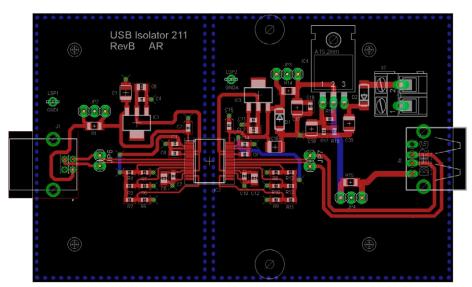

**USB 2.0 Isolator**

Electrically Isolated Connections for USB Devices

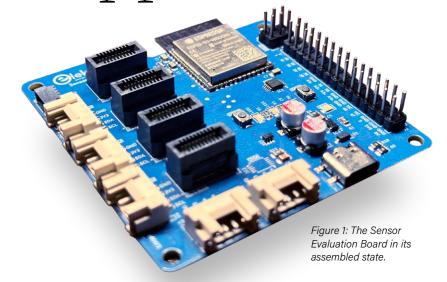

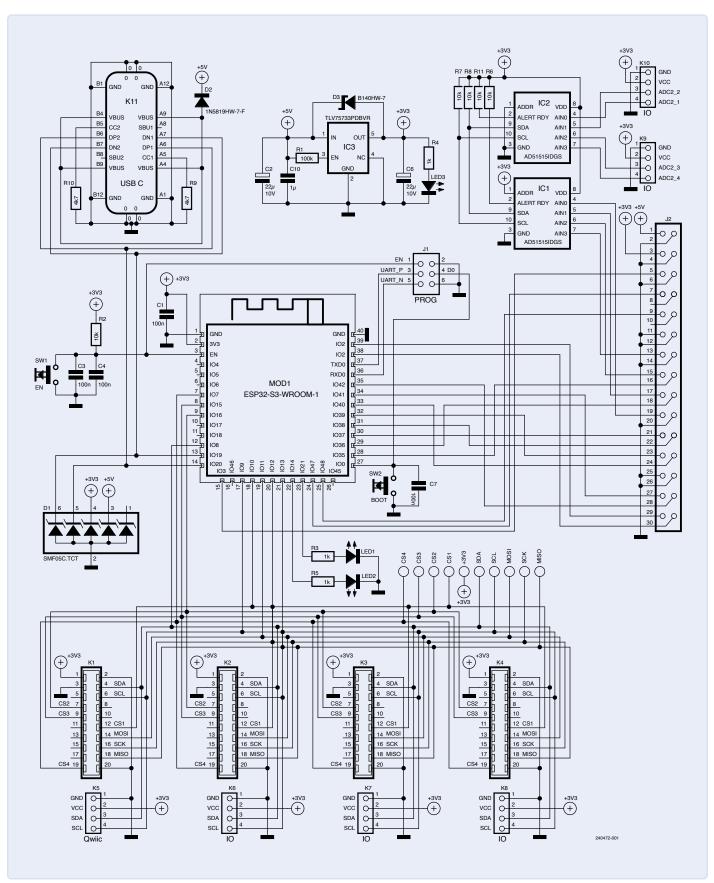

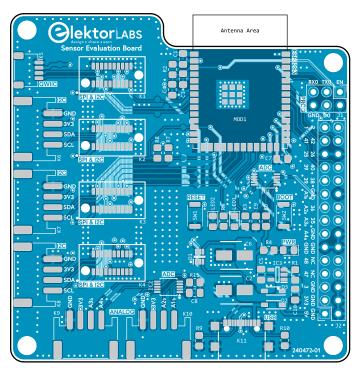

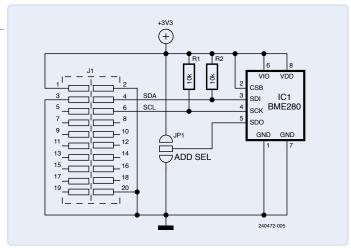

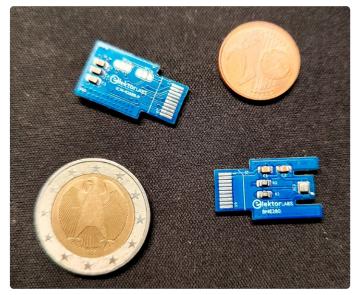

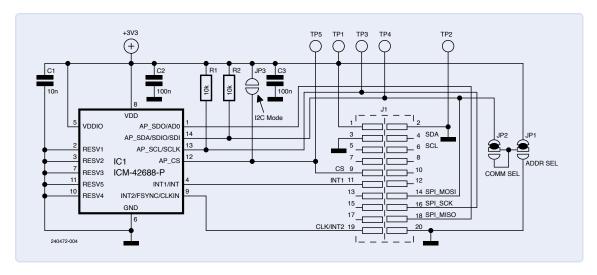

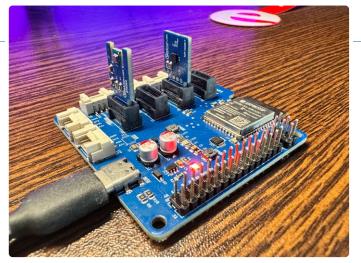

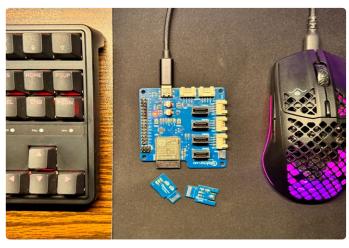

**Modular Sensor Testing**

The ESP32-S3-Based Sensor Evaluation Board

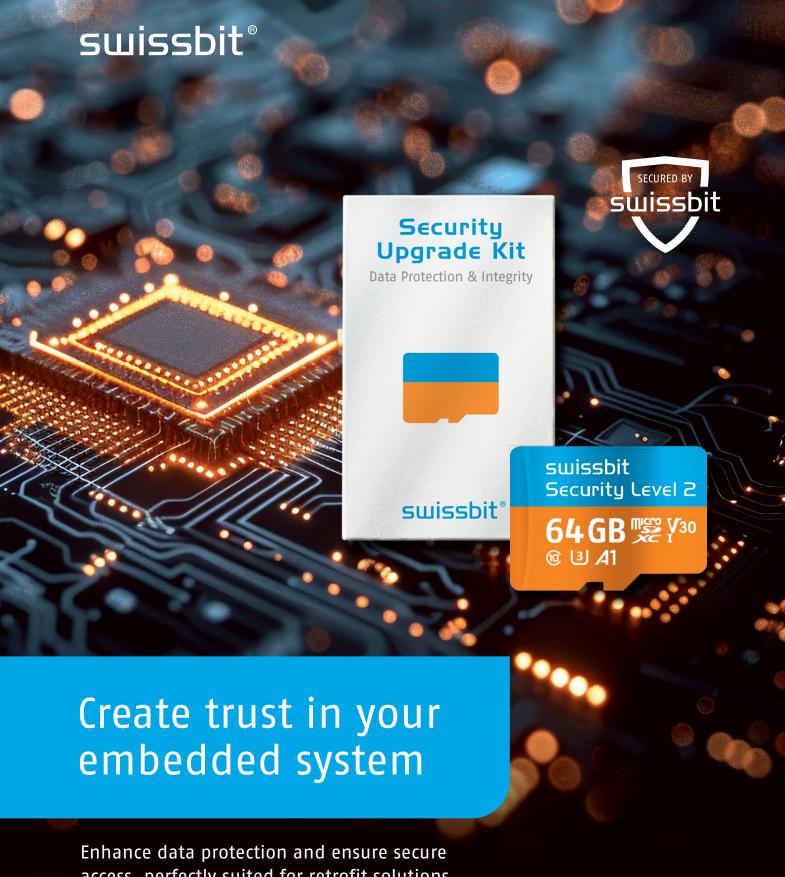

access, perfectly suited for retrofit solutions.

#### COLOPHON

Volume 51, No. 536 March & April 2025 ISSN 1757-0875

Elektor Magazine is published 8 times a year by Elektor International Media b.v.

PO Box 11, 6114 ZG Susteren, The Netherlands

Phone: +31 46 4389444

www.elektor.com | www.elektormagazine.com

Content Director: C. J. Abate Editor-in-Chief: Jens Nickel

For all your questions service@elektor.com

Become a Member

www.elektormagazine.com/membership

#### **Advertising & Sponsoring**

Büsra Kas

Tel. +49 (0)241 95509178 busra.kas@elektor.com www.elektormagazine.com/advertising

#### **Copyright Notice**

© Elektor International Media b.v. 2025

The circuits described in this magazine are for domestic and educational use only. All drawings, photographs, printed circuit board layouts, programmed integrated circuits, digital data carriers, and article texts published in our books and magazines (other than third-party advertisements) are copyright Elektor International Media b.v. and may not be reproduced or transmitted in any form or by any means, including photocopying, scanning and recording, in whole or in part without prior written permission from the Publisher. Such written permission must also be obtained before any part of this publication is stored in a retrieval system of any nature. Patent protection may exist in respect of circuits, devices, components etc. described in this magazine. The Publisher does not accept responsibility for failing to identify such patent(s) or other protection. The Publisher disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from schematics, descriptions or information published in or in relation with Elektor magazine.

Senefelder Misset, Mercuriusstraat 35. 7006 RK Doetinchem, The Netherlands

#### Distribution

IPS Group, Carl-Zeiss-Straße 5 53340 Meckenheim, Germany Phone: +49 2225 88010

#### **EDITORIAL**

#### Jens Nickel

International Editor-in-Chief, Elektor Magazine

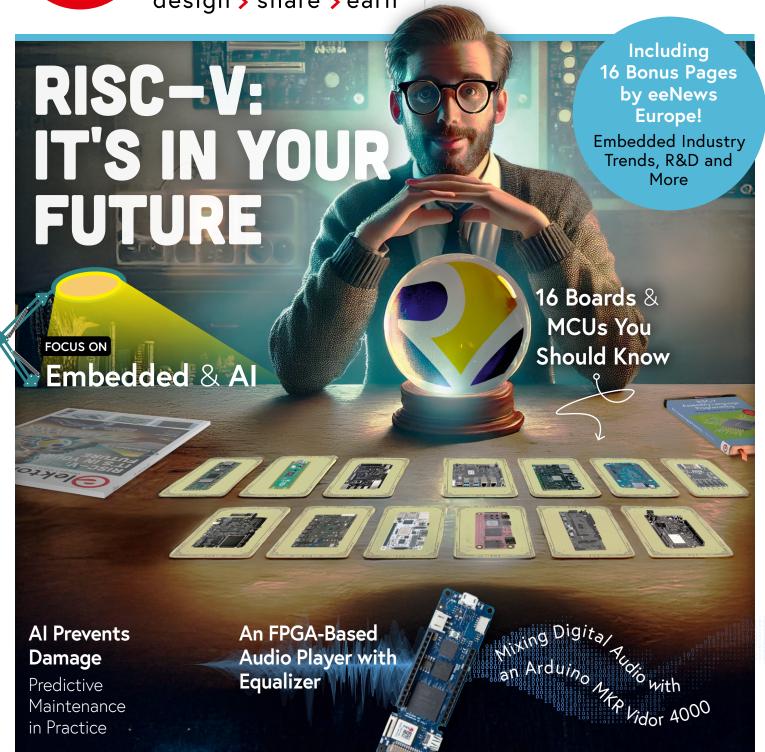

## RISC-V in Practice

When my former colleague, Mathias Claussen, suggested years ago that I should report on "RISC-V," I was immediately fascinated. It had been about 25 years since I had last dealt with processor instructions and registers. But, I could instantly see how valuable it was to have a modern, standardized, and freely usable instruction set, developed by the brightest minds from many companies and universities.

Since then, I've had the opportunity to learn more firsthand: I met an expert at a symposium who is himself part of a standardization committee, and I also spoke with Calista Redmond, at that time CEO of the RISC-V Foundation, at a trade fair. Today, RISC-V has become an everyday tool for all of us in development. That's precisely why we decided to make the open-source ISA our cover story (written by Elektor engineers Saad Imtiaz and Jean-François Simon). As a hands-on magazine, we wanted to show that there are now high-quality boards available for every need and performance class, which can be used for developing IoT, audio/video, AI, and many other projects (page 6).

Personally, I'm not particularly fascinated by the high-end boards costing several hundred euros, but rather by the other end of the spectrum. RISC-V makes it possible to use a microcontroller for just 10 cents in your own projects. Here's a small preview of the next issue: Frequent contributor Tam Hanna will bring such a controller to life in a hands-on article and test how well it works with the associated IDE.

Our colleagues from news platform eeNews Europe also regularly report on RISC-V. In this issue, you'll find about 16 extra pages from their news portal, including articles created exclusively for us. On page 120, for example, we cover a RISC-V processor that can handle GPU, CPU, and even FPGA functions within a single architecture.

What else is in this Embedded and AI issue? As an audio enthusiast, I highly recommend our FPGA-based audio mixer (page 14). It's amazing what can be achieved in terms of quality and features with an Arduino MKR board for well under €100. You should also check out the tool we introduce on page 50, which provides developers with valuable insights into what's happening inside their microcontrollers during program execution. Both articles impressively demonstrate how far you can go with hobby projects.

Get involved in development!

#### **Submit to Elektor!**

Your electronics expertise is welcome! Want to submit an article proposal, an electronics tutorial on video, or an idea for a book? Check out Elektor's Author's Guide and Submissions page:

www.elektormagazine.com/submissions

#### **Elektor Labs Ideas & Projects**

The Elektor Labs platform is open to everyone. Post electronics ideas and projects, discuss technical challenges and collaborate with others.

www.elektormagazine.com/labs

#### The Team

International Editor-in-Chief: Jens Nickel | Content Director: C. J. Abate | International Editorial Staff: Asma Adhimi, Roberto Armani, Eric Bogers, Jan Buiting, Rolf Gerstendorf (RG), Ton Giesberts, Saad Imtiaz, Alina Neacsu, Dr. Thomas Scherer, Jean-Francois Simon, Clemens Valens, Brian Tristam Williams | Regular Contributors: David Ashton, Stuart Cording, Tam Hanna, Ilse Joostens, Prof. Dr. Martin Ossmann, Alfred Rosenkränzer | Graphic Design & Prepress: Harmen Heida, Sylvia Sopamena, Patrick Wielders | Publisher: Erik Jansen | Technical Questions: editor@elektor.com

# THIS EDITION

# Regulars

- 3 Colophon

- From Life's Experience Choice Overload

- Starting Out in Electronics...

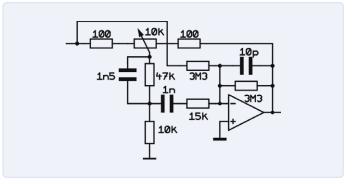

... Continues Filtering and Controls Tone

108 2025: An Al Odyssey

The Rise of Foundation Models and Their Role in Democratizing AI

117 Err-lectronics

Corrections, Updates, and Readers' Letters

## Features

- The RISC-V Open-Source Processor Architecture 16 Boards and MCUs You Should Know

- The Elektor Mini-Wheelie A Self-Balancing Robot Kit

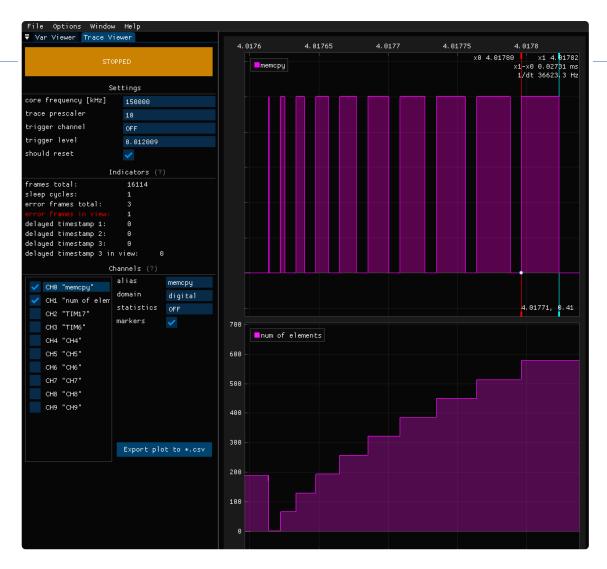

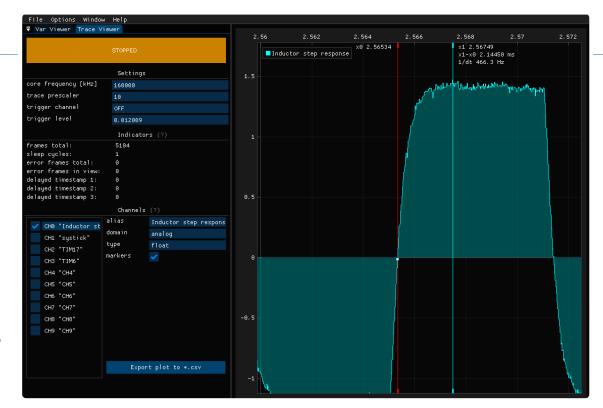

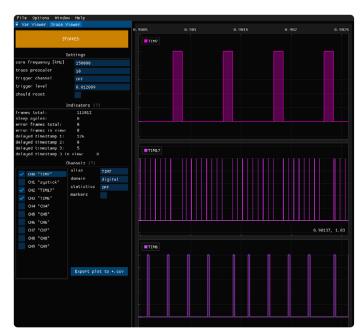

- MCU, I See You MCUViewer Open-Source Multiplatform Debugging Tool

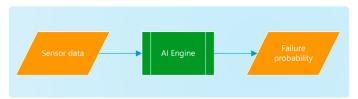

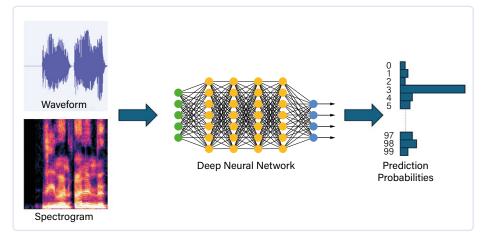

- Intervention Before Damage Predictive Maintenance in Practice

- The Battle for AI at the Edge 82

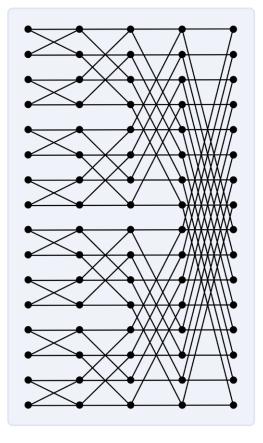

- 124 Dual-Core Programming with a Raspberry Pi Pico Venture into the World of Parallel Programming

# Projects

- An FPGA-Based Audio Player with Equalizer (1) Mixing Digital Audio with an Arduino MKR Vidor 4000

- Laser Head for Pico-Based Sand Clock Drawing with Light

- A Multi-Sensor Environmental Monitoring System for Plants Wireless Measurement of Water Supply and Lighting Conditions

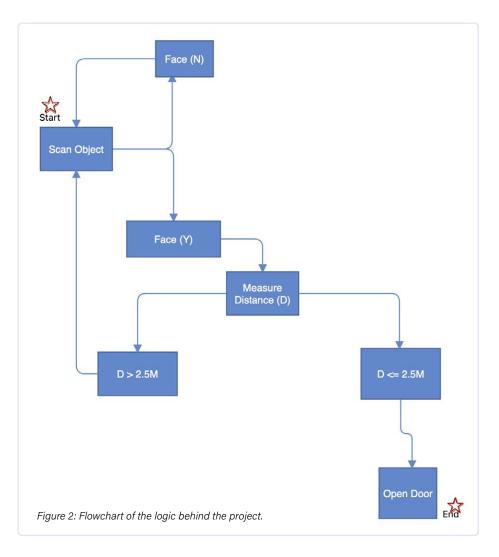

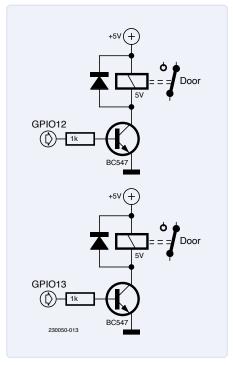

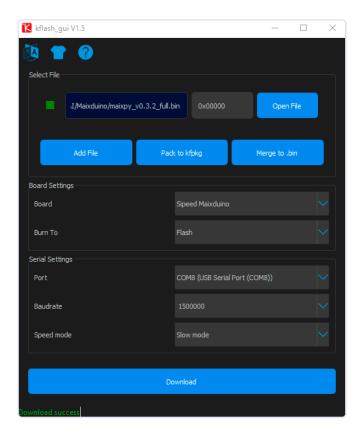

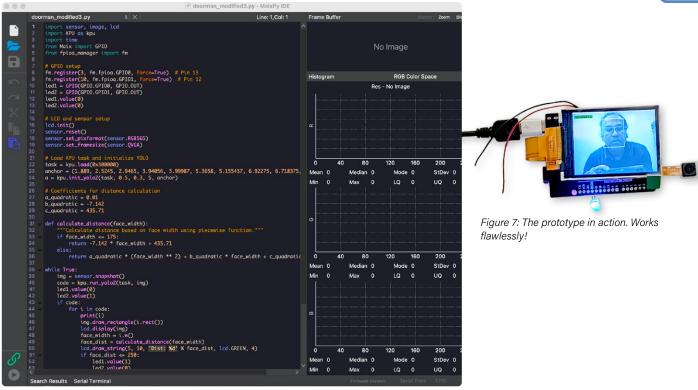

- Maixduino Al-Powered Automatic Doorman Face Detection with a Camera

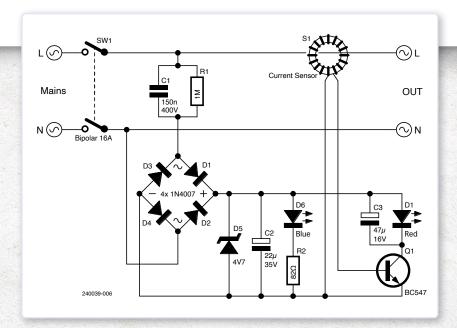

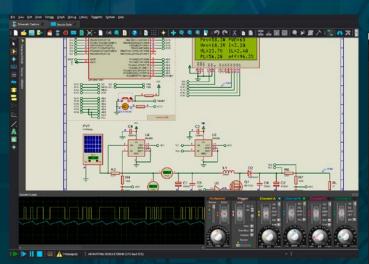

- USB 2.0 Isolator

Electrically Isolated Connections for USB Devices

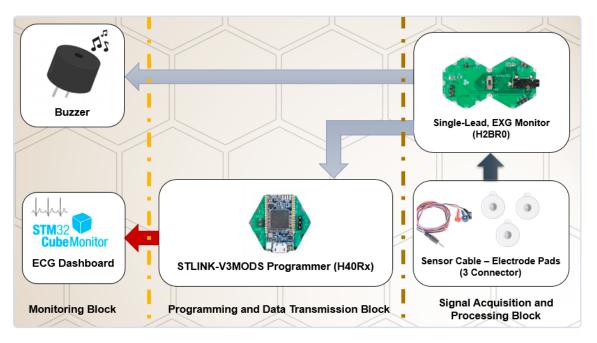

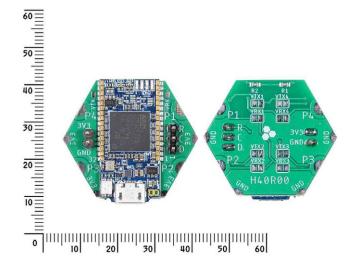

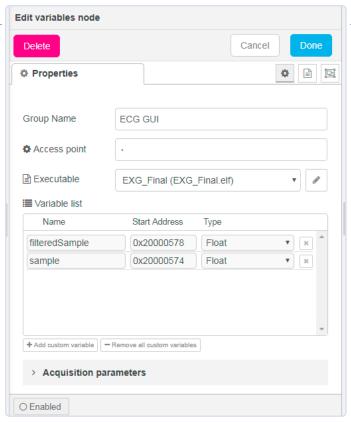

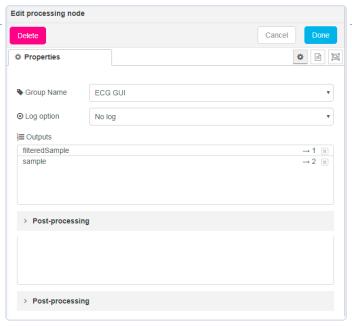

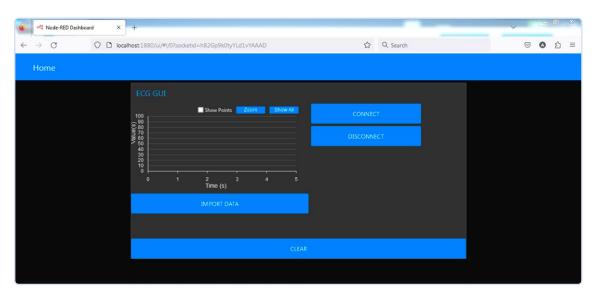

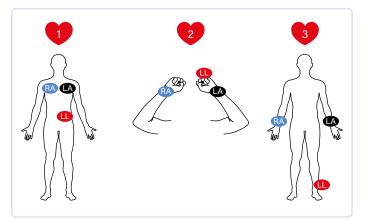

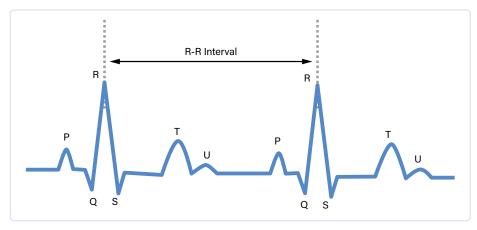

**ECG Graph Monitoring**

An Implementation with Hexabitz Modules and an STM32CubeMonitor

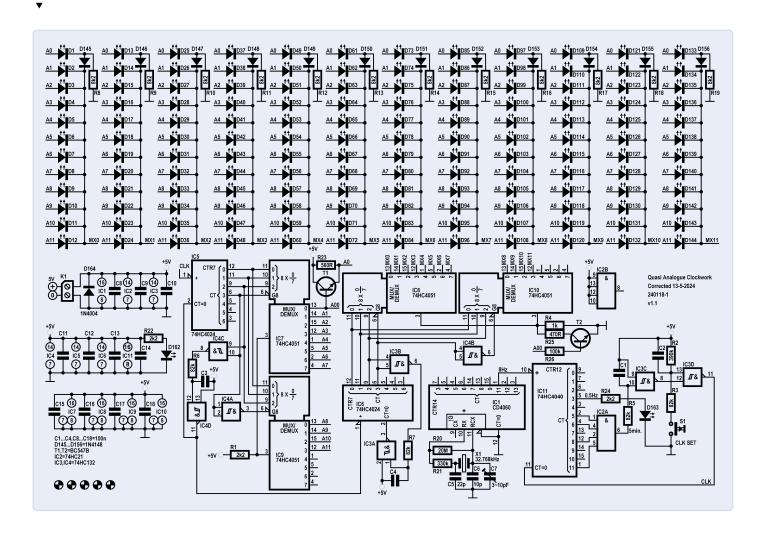

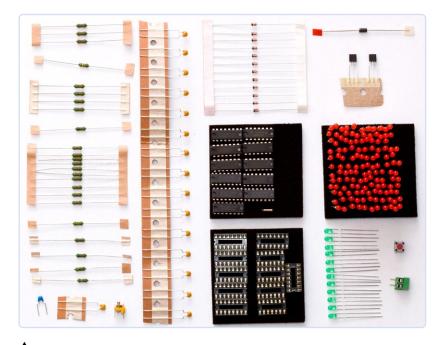

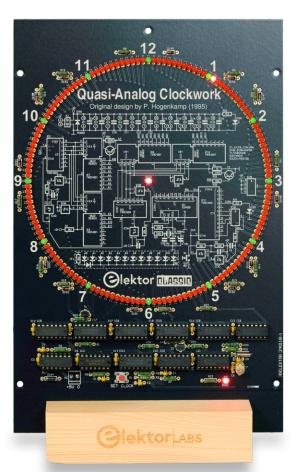

**Quasi-Analog Clockwork**

A Remake of an Elektor Classic

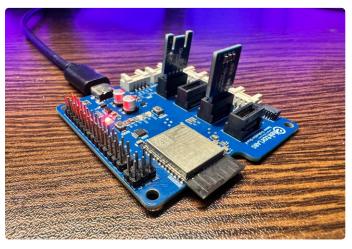

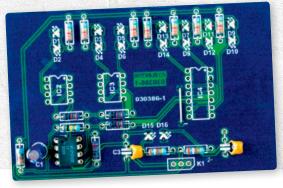

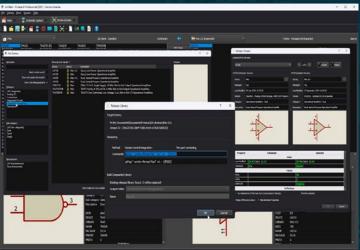

- 102 A Modular Approach to Sensor Testing The ESP32-S3-Based Sensor Evaluation Board

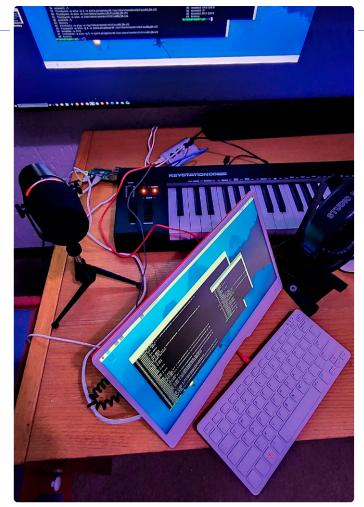

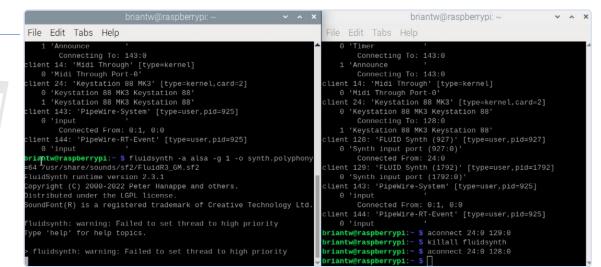

- 112 Raspberry Pi Standalone MIDI Synthesizer (1) Preparing a Platform for Some Edge AI Experiments

**Laser Head for Pico-Based Sand Clock** Drawing with Light

# Industry

- **Enter the STM32 Edge AI Contest**

- **Embedded Electronics 2024** Al Is Set to Redefine the Industry

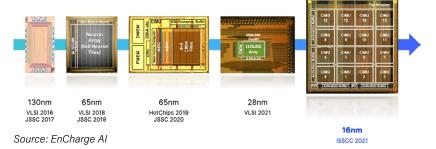

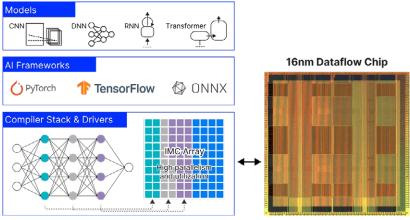

- Charge-Based In-Memory Compute at EnCharge AI 44

- Al Inferencing at 10 Times Lower Power and 46 20 Fold Lower Cost

- Click Board Helps Develop and Train ML Models for Vibration Analysis

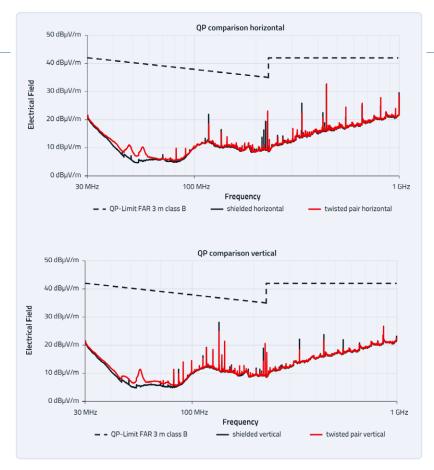

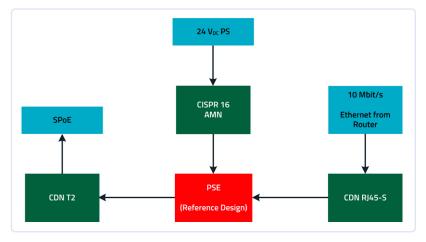

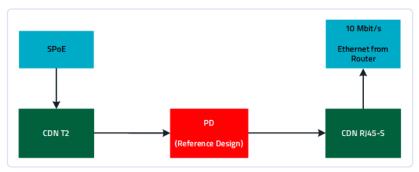

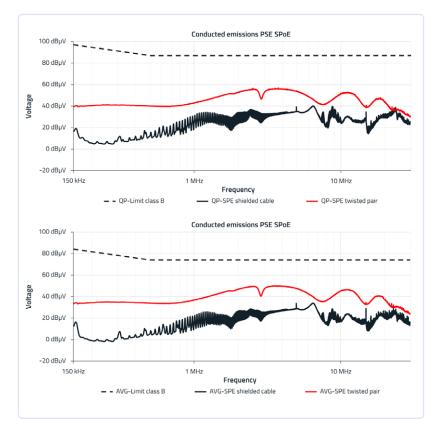

- SPoE Electromagnetic Compatibility Single-Pair with Power-Over-Ethernet Through the Eves of EMC

- Color TV: A Wonder of Its Time Creating a New World

- HaLow Hits Record 16 km Wi-Fi Distance at 900 MHz

- 88 First CHERI RISC-V Embedded Chip and Early Access **Program**

- Third-Generation Wildfire Detection Uses Satellite Links

- 120 Universal Al RISC-V Processor Does It All CPU, GPU, **DSP, FPGA**

- 122 CEO Interview: Ventiva's Thin and Cool Tech

# Next Editions

#### Elektor Magazine May & June 2025

As usual, we'll have an exciting mix of projects, circuits, fundamentals, and tips and tricks for electronics engineers and makers. Our focus will be on Test & Measurement.

- > MPP Tracker and Charge Controller

- > Sine Wave Generator with Adjustable Frequency

- > Battery Monitoring System

- > GUI for Optimizing PID Parameters

- > Frequency Counter

- > 10-Cent Controller in Practice

- > Stand-Alone Crystal Tester

- > FPGA-Based Audio Player: Mixing and Filters

Elektor Magazine's May & June 2025 edition will be published around May 14, 2025.

Arrival of printed copies for Elektor Gold members is subject to transport.

# BONUS CONTEN

Check out the free Embedded & AI bonus edition of Elektor Mag!

- > Virtual Assistant with ChatGPT and Raspberry Pi

- > Review: Makerfabs SenseLoRa

- > The Connected Autonomous Vehicle and Its Environment

- > Peculiar Parts: The Intel 8279 Keyboard/Display Interface

- > Infographics: Embedded and AI

www.elektormagazine.com/ embedded-ai

#### By Saad Imtiaz (Elektor) and Jean-François Simon (Elektor)

Discover how RISC-V, the open-source newcomer in the microcontroller world, is benefiting many engineers and innovators in the industry with its simplicity and other advantages. Join us as we explore a selection of RISC-V-based boards to experiment with!

> Microcontrollers are everywhere, powering everything from your dishwasher to powerful computing systems and millions of wearable and IoT devices. For the processor cores and architectures, names such as ARM, AVR, MIPS, Xtensa, 8051, etc., dominate the landscape, each with unique strengths and areas of application. These platforms, used in many very popular microcontrollers such as the STM32, ESP32-S3, ATmega and so on, share a common trait: They are proprietary.

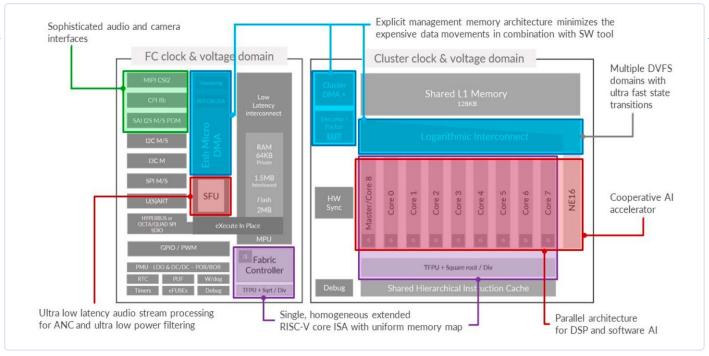

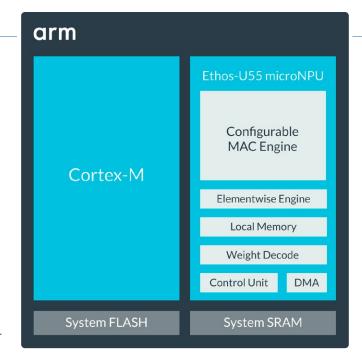

> Enter RISC-V (Figure 1), a relatively new player in the world of microcontrollers and processors. Some

of our readers may recall that we published a few articles on this topic a few years ago, when hardware choices were much more limited [1][2]. Developed at the University of California, Berkeley, starting in 2010, RISC-V was envisioned as a forward-looking architecture unburdened by legacy compatibility. Unlike traditional processor architectures, RISC-V is open-source, modular, and designed in a modern way. More precisely, it is an open-standard instruction set architecture (ISA), i.e. a standardized definition of the instructions a processor can execute. It is designed to overcome the proprietary restrictions of traditional ISAs, such as those from Intel, AMD or ARM. Unlike proprietary ISAs, RISC-V allows anyone to implement its specifications without legal restrictions, fostering innovation and collaboration between companies and leading experts.

With an open ISA, many companies can develop and sell ready-to-use RISC-V cores, in the form of intellectual property (IP) blocks. A microcontroller manufacturer can buy a RISC-V core and use it in a microcontroller, adding the manufacturer's own peripherals. This encourages competition between IP

RISC-\

Figure 1: RISC-V logo. Source: © RISC-V Foundation, CC BY-SA 4.0

providers, stimulating innovation and driving down costs. Manufacturers can switch to higher-performance ICs without being locked into proprietary ecosystems.

#### **RISC-V: A Simple Concept**

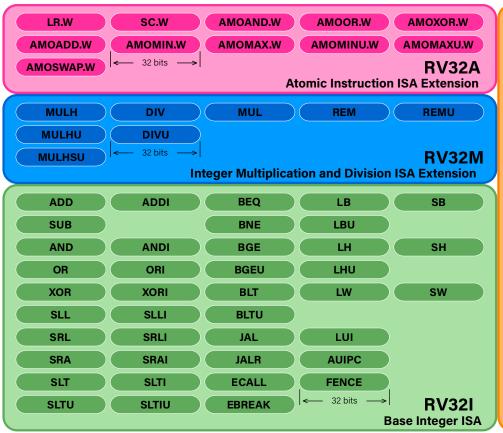

RISC-V, as its name implies, adheres to the Reduced Instruction Set Computer (RISC) principles, which emphasize a small, optimized set of instructions. This reduces the complexity of hardware design and facilitates faster development cycles. Unlike legacy architectures such as x86, which carry decades of backward-compatibility baggage, RISC-V starts with a clean slate, incorporating only what's necessary for modern applications. For example, RISC-V's base consists of just 47 instructions, compared to hundreds on the x86. You can find details about the instruction set here [3], summarized by GitHub user msyksphinz-self. This lean design makes it easier to implement and verify, resulting in lower costs and fewer bugs. While this base instruction set is indeed quite minimalist, there are optional extensions that can be added as needed.

#### **Modularity**

The extensions enable processors to be customized to specific needs. There are about 30 of them, including multiplication and division (M) for arithmetic operations, atomic instructions (A) for multithreaded programming, single and double-precision floating-point (F and D) for scientific computing and signal processing, vector processing (V) for parallel data operations, compressed instructions (C), etc. The full list can be found at [4] along with more detail. This modularity optimizes silicon utilization and energy efficiency: Chip manufacturers can produce microcontrollers that contain just what is needed for a given application, without wasting resources, thus reducing costs. For instance, a microcontroller for IoT devices

Figure 2: Instruction Set for the RV32I base core with M. A. and C extensions. Source: github.com/kuashio/ risc-v-diagrams CC BY-SA 4.0

#### **RV32IMAC**

might exclude floating-point units to save power and silicon, while a processor for AI workloads would include vector extensions for accelerated computation. As an example, a nice diagram showing the base integer instruction set for a 32-bit core (RV32I) together with the M, A, and C extensions has been put together by Github user kuashio (**Figure 2**).

#### **More Security?**

RISC-V's openness has spurred innovation in processor security. If you have an application for which security is important, then the open-source nature of RISC-V is a great feature: It's then easier to inspect. It's for the same reason that many crypto wallets are open-source! Extensions such as CHERI (Capability Hardware Enhanced RISC Instructions) enable fine-grained memory protection, reducing vulnerabilities to attacks such as buffer overflows. Unlike proprietary architectures, RISC-V allows researchers to experiment and implement security features without licensing restrictions.

#### **Reducing Costs and Sharing Results**

An open ISA eliminates licensing fees associated with proprietary ISAs. Microcontroller manufacturers can develop their own RISC-V cores or purchase ready-to-use intellectual property (IP) blocks from vendors. This competitive ecosystem drives down costs, making advanced microcontrollers and processors accessible to a wider audience. Further cost reduction is achieved by sharing the development of software ecosystems (compilers, OS support, etc.) between several companies. RISC-V's open model encourages the pooling of

resources and expertise, akin to how Linux revolutionized operating systems or Ethernet transformed networking. Companies can focus on unique differentiators rather than duplicating foundational work, accelerating innovation and improving the overall ecosystem.

#### **Legal Peace of Mind for Everyone**

For a university, how can you legally teach processor design to computer engineering students when x86 and ARM cores are not open-source? Beyond the legal constraints, there is also a technical challenge: These are not modular, which requires students to implement a massive set of instructions before achieving a potentially functional processor. Semiconductor multinationals also value this legal piece of mind. Have you heard about the legal dispute between ARM and Qualcomm [5]? RISC-V, on the other hand, offers companies a different approach, with no licensing fees.

#### **Adoption by Major Players**

RISC-V's open approach has garnered significant attention, with major companies integrating it into their products. By 2015, the RISC-V Foundation was formed, attracting major players such as Google, NVIDIA, Western Digital, and NXP. Over the years, AMD, Qualcomm, IBM, and others have joined, further solidifying its presence in the market. NVIDIA uses RISC-V for specific cores in its GPUs, while Western Digital leverages it for storage devices. SiFive, a pioneer in RISC-V development, offers a range of processors for embedded and high-performance applications. The main IP suppliers are Nuclei, SiFive, and T-Head, while some manufacturers, such as Espressif and WCH, are developing their own IPs to differentiate their products. Without knowing it, you may already have used RISC-V hardware, such as the ESP32-C3, ESP32-C6, and ESP32-P4. Even Raspberry Pi incorporated RISC-V cores into its latest microcontroller, the RP2350, used on the Raspberry Pi Pico 2.

#### **RISC-V** in Practice

Despite the hype surrounding it, is RISC-V truly "revolutionary" for the average user? Most engineers and hobbyists program in C/C++ or other high-level languages, meaning you won't need to learn this reduced instruction set. For developers and engineers, transitioning to RISC-V only requires modest changes to established workflows and habits. Tools such as compilers and development environments are already available and getting better

> every day. If you're interested in embedded development, using RISC-V microcontrollers is a very relevant skill to acquire and add to your toolbox. For those who enjoy getting hands-on and programming in assembly, one of our authors has published a short article [6] on our website about programming the RISC-V core on an ESP32-C3, with a companion Elektor book. For those who prefer programming in C on ultra-low-cost microcontrollers such as the CH32V003 from WCH, we've discovered an excellent educational site [7] created by Vincent

Defert. The site is in French, but we encourage you to use a browser extension for real-time translation to take full advantage of this outstanding content! Our bet is that the RISC-V standard is here to stay, and these skills will be easily reusable in the future. In the second part of this article, we will present some of the exciting RISC-V-based development boards available today that you can use for your next project. Have fun!

#### **Notable RISC-V Development Boards**

RISC-V development boards have been gaining traction in recent years as the RISC-V ecosystem continues to expand. These boards cater to hobbyists, researchers, and professionals looking to leverage the flexibility and open-source nature of the RISC-V architecture. Below is a detailed look at some of the most notable RISC-V development boards available today, their uses, and potential advantages.

Right now, these are just the beginning of a small selection of RISC-Vbased MCUs and CPUs. They range from Arduino Nano-grade MCUs to desktop and laptop-grade CPUs, and many more are expected to emerge in the coming years, reflecting the rapid growth and potential of the RISC-V ecosystem. ►

240736-01

RISC-V's openess has spurred innovation in processor security.

#### **High-Performance RISC-V Processors**

Besides single board computers and microcontrollers for embedded electronics, RISC-V processors are already making significant inroads into high-performance computing (HPC) and AI applications. The SiFive Intelligence X280, for example, is optimized for Al and machine learning workloads. It features scalable multicore configurations, integrated vector extensions, and support for advanced AI operations such as tensor computations. Last year, SiFive also announced their Performance P870-D processor for use in servers and datacenters [8]. For more info on the deployment of Large Language Models (LLMs) on their top-of-the-range hardware with performance benchmarks, read this interesting blog post [9]. Similarly, Alibaba's Xuantie C910 processor, which incorporates Al-specific instructions and supports high data throughput, powers cloud-based AI systems, including real-time inference platforms.

The future of RISC-V in high-performance computing is promising, with several ambitious projects underway. Ventana Micro Systems [10] is developing a server-class RISC-V chip with up to 128 cores per processor, targeting enterprise-level applications such as cloud computing, database management, and large-scale AI training. Their designs prioritize parallelism and energy efficiency, targeting resource-intensive workloads. Another player, Esperanto Technologies, is building the ET-SoC-1, a processor that integrates over 1,000 RISC-V cores onto a single chip [11]. Designed for AI inference tasks, it follows the path of extreme parallelism. Let's see what comes next!

#### **Questions or Comments?**

Do you have questions or comments about this article? Email the authors at saad.imtiaz@elektor.com and jean-francois.simon@elektor.com, or contact Elektor at editor@elektor.com.

#### **Related Products**

- Raspberry Pi Pico 2 www.elektor.com/20950

- > Milk-V Duo 256M SBC www.elektor.com/20973

- > WCH CH32V307V-EVT-R1 Dev Board www.elektor.com/20448

- > LilyGo TTGO T-Display-GD32 www.elektor.com/19510

- > Seeed Studio XIAO ESP32C3 www.elektor.com/20265

- > Luckfox Pico Mini B www.elektor.com/21011

#### WEB LINKS •

- [1] Stuart Cording, "What Is RISC-V?," elektormagazine.com, April 2021: https://elektormagazine.com/articles/what-is-risc-v

- [2] Mathias Claussen, "BL808 and Cohorts: A Look at New RISC-V MCUs," elektormagazine.com, June 2023: https://elektormagazine.com/articles/bl808-and-cohorts-new-riscv-mcus

- [3] RISC-V Instruction Set, RISC-V ISA pages, GitHub: https://msyksphinz-self.github.io/riscv-isadoc

- [4] RISC-V on Wikipedia: https://en.wikipedia.org/wiki/RISC-V

- [5] Arm vs. Qualcomm Dispute, Capacity Media: https://capacitymedia.com/article/arm-pulls-qualcomms-architecture-licence

- [6] Warren Gay, RISC-V Assembly Language Programming (Elektor 2022): https://elektormagazine.com/articles/why-risc-v-assembly-language

- [7] Embedded Development with RISC-V [French]: https://riscv-mcu.defert.com

- [8] High-performance RISC-V Datacenter Processor from SiFive: https://sifive.com/press/sifive-announces-high-performance-risc-v-datacenter-processor-for-ai-workloads

- [9] LLM Optimization and Deployment on SiFive RISC-V: https://sifive.com/blog/llm-optimization-and-deployment-on-sifive-intellig

- [10] Ventana Micro Systems: https://ventanamicro.com

- [11] 1,000 Cores on a Chip, VLSIFacts: https://tinyurl.com/et-soc-1-chip

#### **HiFive Premier P550**

The HiFive Premier P550 is a high-performance development board designed to push the boundaries of RISC-V development. Powered by the Eswin EIC7700X SoC with a quad-core SiFive P550 CPU, it provides a robust platform for developing and optimizing RISC-V operating systems and applications across diverse markets. It starts at \$399 for the 16 GB RAM variant, and can support up to 32 GB of LPDDR5-6400 memory, 128 GB of eMMC storage, and HDMI 2.0 display support, enabling intensive computational tasks. Pre-installed with Ubuntu Linux 24.04, this board is perfect for advanced development in AI, operating system design, and high-performance application.

https://sifive.com/boards/hifive-premier-p550

#### **HiFive1 Rev B**

The HiFive1 Rev B is an entry-level board designed for IoT and edge computing, powered by the FE310-G002 processor, which includes a 32-bit RV32IMAC core. Costing around \$65, its 16 KB L1 instruction cache, 16 KB data SRAM, and support for flexible clock generation make it efficient for lightweight applications. With a USB debugger upgraded to SEGGER J-Link-OB and compatibility with SiFive Freedom Studio, developers benefit from seamless drag-and-drop flash programming and robust debugging tools. This board is ideal for prototyping IoT devices, developing low-power applications, and exploring the fundamentals of RISC-V development. https://sifive.com/boards/hifive1-rev-b

#### **VisionFive 2 SBC**

The VisionFive 2 is the world's first high-performance RISC-V SBC with an integrated GPU, powered by the StarFive JH7110 SoC. With a quad-core CPU running up to 1.5 GHz and support for up to 8 GB LPDDR4 memory, it excels in multimedia processing and dual-display output via HDMI and MIPI DSI interfaces. Features such as three USB 3.0 ports, Gigabit Ethernet with PoE, and GPIO headers make it a strong contender for IoT, lightweight servers, and edge computing. Its robust multimedia capabilities, including 4K video decoding and encoding, make it ideal for developers exploring high-performance RISC-V applications in cost-effective projects, which is currently sold on Amazon's website for \$99.

https://starfivetech.com/en/site/boards

#### Milk-V Megrez

The Milk-V Megrez is a Mini-ITX RISC-V device powered by the Eswin EIC7700X SoC, featuring a quad-core SiFive P550 CPU at 1.8 GHz. Its built-in GPU supports advanced graphics standards such as OpenGL ES 3.2 and Vulkan 1.2, while the 19.95 TOPS NPU enables local AI processing for applications in machine learning and robotics. With support for up to 32 GB LPDDR5 memory, multiple storage options, including SATA SSDs and eMMC, and a range of connectivity options like HDMI, USB 3.0 and dual Gigabit Ethernet, this board is ideal for AI development, high-performance computing, and multimedia tasks. Its compatibility with Linux and versatile hardware interfaces make it a significant step forward in RISC-V desktop computing. You can grab this powerful board for \$200.

https://milkv.io/megrez

#### Milk-V Duo 256M

The compact Milk-V Duo 256M is a versatile embedded development platform powered by the SOPHGO SG2002 chip. With a memory boost to 256-MB DRAM, it caters to applications requiring larger memory capacities. The platform features a dual-core RISC-V CPU (C906 at 1 GHz and 700 MHz) alongside a Cortex-A53 Arm CPU, enabling seamless switching between RISC-V and Arm architectures. Its TPU delivers 1.0 TOPS of AI computing power, making it ideal for edge intelligence in smart cameras, visual doorbells, and IoT devices. Rich GPIO interfaces (SPI, UART) and multimedia capabilities like H.265 video encoding, HDR, and noise reduction further enhance its suitability for industrial and smart home applications. The Duo also supports Linux and RTOS, offering developers a powerful and flexible platform for diverse projects. The boards are available for about €30.

https://milkv.io/docs/duo/getting-started/duo256m

#### Bouffalo Lab BL616/BL618 and Sipeed MOS

The Bouffalo Lab BL616 and BL618 are 32-bit RISC-V wireless MCUs built for IoT applications. They support Wi-Fi 6, Bluetooth 5.2, and Zigbee, making them ideal for smart home devices and Matter-based automation. Running at up to 320 MHz with an integrated FPU and DSP, they bawlance performance and efficiency. With 480 KB SRAM, embedded flash, and multiple communication interfaces (USB 2.0, SDIO, SPI, I<sup>2</sup>S), they are versatile for embedded projects. Their ultra-low-power modes and secure boot features make them well-suited for battery-powered devices requiring reliable connectivity and security. Additionally, Sipeed has launched the compact M0S module based on the BL616. With 4 MB flash, 512 KB SRAM, and USB 2.0 support, this tiny (11×10 mm) module is designed for ultra-low-cost IoT applications. With all these features, a board is available for a modest \$4.

https://openbouffalo.org/index.php/BL616 https://wiki.sipeed.com/hardware/en/maixzero/m0s/m0s.html

#### **Milk-V Mars**

The Milk-V Mars is a compact and high-performance RISC-V SBC powered by the StarFive JH7110 SoC, featuring a quad-core CPU clocked up to 1.5 GHz. It supports up to 8 GB of LPDDR4 memory, an eMMC slot, and SPI flash for bootloader storage, making it highly adaptable for development tasks. With three USB 3.0 ports, one USB 2.0 port, and an HDMI 2.0 output supporting 4K resolution, it is well-suited for multimedia projects, lightweight servers, and general-purpose Linux development. Additional features such as a 40-pin GPIO, PoE-enabled Ethernet, and MIPI interfaces for cameras further enhance its versatility, enabling use in IoT, edge computing, and embedded systems. At around \$70 for the 8 GB variant, it's a steal for the performance it delivers. https://milkv.io/mars

#### MangoPi MQ-Pro SBC

Compact and efficient, this board serves as a viable alternative to the Raspberry Pi Zero, tailored for IoT and lightweight embedded systems. Equipped with the D1 RISC-V core, it supports Tina-Linux/Debian and runs complete Python applications. Its peripheral-rich design includes GPIO, I<sup>2</sup>C, SPI, and HDMI, making it ideal for small-scale automation, portable gadgets, and educational projects requiring minimal space and power. Its community-driven ecosystem ensures flexibility and ease of use in diverse lightweight applications. Surprisingly, you can get all these features for as low as \$35. https://mangopi.org/mqpro

#### **Nuclei DDR200T Development Board**

This board by Nuclei System integrates a Xilinx XC7A200T-2 FPGA for hardware acceleration, prototyping, and custom logic development, along with abundant storage and extended interfaces for versatile connectivity. The RISC-V microcontroller, the GD32VF103, enhances programmability, making it ideal for control tasks and interfacing with the FPGA. Its combination of FPGA flexibility and MCU integration supports industrial automation and embedded development. While priced at \$770, the board justifies its cost with its advanced features and exceptional performance for demanding applications.

https://nucleisys.com/developboard.php

#### **Banana Pi BPI-F3**

The Banana Pi BPI-F3 is an industrial-grade RISC-V development board powered by the SpaceMiT K1 8-core RISC-V processor, which integrates 2.0 TOPS of AI computing power. It offers flexible configurations with 2/4/8/16 GB DDR and up to 128 GB eMMC storage. With dual Gigabit Ethernet ports, four USB 3.0 ports, PCIe for M.2 expansion, and support for HDMI and dual MIPI-CSI cameras, this board excels in advanced prototyping, industrial applications, and Al-driven tasks. Its compatibility with Linux distributions and diverse hardware interfaces makes it ideal for high-performance computing and robust development environments. Available at \$70, it strikes a perfect balance between cost and capability.

https://banana-pi.org/en/banana-pi-sbcs/175.html

### **Espressif ESP32 boards**

Espressif's RISC-V-based MCUs, including the ESP32-P4, ESP32-C3, and ESP32-C6, are among our favorites and highly favored by the community for their versatility and robust software ecosystem. The latest and greatest ESP32-P4 features a dual-core CPU running at up to 400 MHz, an auxiliary low-power core, and 768 KB of on-chip SRAM with external PSRAM support. It excels in AI, IoT, and HMI applications, boasting 55 programmable GPIOs and extensive peripheral support, including USB OTG 2.0 HS, Ethernet, and MIPI-CSI for high-resolution cameras. With hardware accelerators and media encoding for H.264 at 1080p, it is a top choice for multimedia-rich projects. The wider Espressif RISC-V family offers excellent framework compatibility, making firmware development seamless across multiple platforms. These boards are also budget-friendly, with prices ranging from as low as \$3 to \$50, depending on the variant and features. One of the best options is the Seeed Studio XIAO ESP32C3, equipped with the ESP32-C3 SoC, combining 400-KB SRAM and 4-MB Flash in a compact thumb-sized design. It is ideal for the IoT, wearables, and low-power networking.

https://espressif.com/en/products/socs/esp32-p4 https://wiki.seeedstudio.com/XIAO\_ESP32C3\_Getting\_Started

#### **BeagleV Ahead**

The BeagleV Ahead is an open-source RISC-V SBC powered by the T-Head TH1520 SoC, featuring a 2 GHz quad-core XuanTie C910 processor with advanced GPU and NPU capabilities. Its compatibility with BeagleBone Black cape headers allows for hardware expansion, making it suitable for robotics, AI, and multimedia applications. With support for Linux and open-source frameworks, it is designed to enable developers to explore the potential of RISC-V architecture in complex AI and machine learning projects. For only \$150, this SBC punches well above its weight.

https://beagleboard.org/boards/beaglev-ahead

#### WCH CH32V003 boards

The CH32V003 by WCH is the most cost-effective of this bunch, a 32-bit RISC-V MCU designed for industrial and general-purpose applications. It features a QingKe V2A core running at up to 48 MHz, 16 KB flash, and 2 KB SRAM. With support for multiple low-power modes, it is optimized for energy-efficient operations. It includes a 10-bit ADC, op-amp comparator, and standard interfaces such as USART, I<sup>2</sup>C, and SPI. The ultra-small package and 1-wire serial debug interface make it ideal for compact embedded systems, automation, and low-power IoT devices. The chip itself costs less than \$0.20, and I was even able to spot a CH32V003 development board on AliExpress, being sold for less than \$1 — a deal that's hard to resist. By the way: In one of the next editions, author Tam Hanna will try out the CH32V003 and the corresponding IDE.

https://wch-ic.com/products/CH32V003.html

#### WCH CH32V307V-EVT-R1

The WCH CH32V307 on the CH32V307V-EVT-R1 board is a feature-rich RISC-V microcontroller designed for interconnected applications. It runs at up to 144 MHz, with a single-precision FPU and hardware stack area for improved performance. The controller includes 64-KB SRAM, 256-KB Flash, and a wide range of peripherals, such as eight UART ports, USB 2.0 HS, Ethernet with built-in PHY, and multiple timers. Its GPIOs can be mapped to external interrupts, and it supports ADC, DAC, SPI, and I<sup>2</sup>C interfaces, making it versatile for industrial automation, real-time data processing, and communication-centric tasks. Its efficient low-power modes and robust connectivity make it a solid choice for advanced embedded systems. You can find the dev board at different suppliers (including the Elektor Store) for around €20.

https://github.com/openwch/ch32v307

#### GigaDevice GD32VF103CBT6 boards

The GD32VF103CBT6 microcontroller by GigaDevice can be found on development boards like the Sipeed Longan Nano and the LilyGo TTGO T-Display-GD32 RISC-V Development Board (available in the Elektor Store for a discounted price of just €12.95). Both boards are equipped with a small LCD and SD card socket, making all kinds of stand-alone devices possible. The 32-bit RISC-V CPU integrates a Bumblebee Core by Nuclei System, 128-K Flash and 32-K SRAM, an RTC, 3x USART and many other interfaces like USB, I2C, SPI, I2S and CAN.

www.gigadevice.com/product/mcu/main-stream-mcus/gd32vf103-series

#### **Raspberry Pi Pico 2**

Raspberry Pi surprised everyone by adding two Hazard3 RISC-V cores to the recent RP2350 powering the Raspberry Pi Pico 2! It offers 520 KB of SRAM, 4 MB of flash storage, 26 multi-purpose GPIO pins, including 4 that can be used for ADC, and a comprehensive set of peripherals including two UART interfaces for serial communication, two SPI plus two I<sup>2</sup>C controllers and 24 PWM channels. Additionally, the board includes 12 PIO (programmable I/O) state machines and a USB 1.1 controller with PHY supporting both host and device modes. Priced at only \$5, the Pico 2 is perfect for learning and experimenting with RISC-V.

https://raspberrypi.com/products/raspberry-pi-pico-2

# An FPGA-Based An FPGA-Based An FPGA-Based With Audio Player With Equalizer (1)

Mixing Digital Audio with an Arduino MKR Vidor 4000

By Dr. Christian Nöding (Germany)

Have you ever wanted to know what is inside a digital audio mixing console? Or have you already programmed some MP3-player based on an ESP32 and the great Arduino libraries, but without the option for processing these audio signals? In this two-part series, we will create a multichannel digital mixing console with multiband equalizers, an audio file player and an analog input. Rock your next party with an expandable DIY system!

This is the first part of a two-part series exploring the design and implementation of an FPGA-based audio player with equalizer functionality, using the Arduino MKR Vidor 4000. In this part, I'll explain the foundational aspects of the project, including the required toolchain, the interplay between FPGA logic and microcontrollers, and an introduction to the basics of audio signal processing. By the end, you'll have a clear understanding of the project and its goals. The full documentation and source files are available online, with links provided at the end of the article.

#### **The Starting Point**

For over 10 years, I've been a fascinated user of digital audio mixing consoles without questioning their inner workings. However, when I found a defective digital Behringer P16-I at a flea market, I saw an opportunity to dig deeper and understand how such a device operates.

The P16-I features 16 analog inputs and six Ethernet-like jacks for digital audio output via Cat5e cables, using a protocol called "Ultranet." Ultranet is a slightly modified AES/EBU signal, which we'll explore later in detail.

# The Challenge: Building a Versatile Audio Mixer

Studying the P16-I fascinated me and gave me the idea of designing my own audio mixer. My goal was to design an audio system capable of inputting up to 20 channels from various analog and digital sources, processing these signals in real time, and mixing them with advanced audio features like equalization and dynamic control. This project replicates a mixing console's core functionality, and we'll also keep it flexible and see how to expand its functionality.

#### **Choosing the Right Platform**

Since the advent of digital audio, signals have been processed at specific bit depths and sample rates. Modern audio, often 24-bit with sample rates starting at 48 kHz, demands high processing power, which

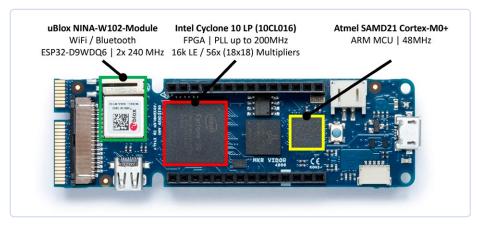

Figure 1: Arduino MKR Vidor 4000.

smaller microcontrollers struggle to manage in real time. This is where digital logic, and particularly FPGAs, excel. So, how to find the right FPGA board for our needs, one that's both user-friendly and appealing in terms of hardware?

While researching an FPGA solution for this project, I came across the Arduino MKR Vidor 4000. This board from Arduino's MKR family combines an ideal set of components for digital audio processing: two microcontrollers, built-in Wi-Fi and Bluetooth, and of course an FPGA — making it a perfect starting point for this project.

Figure 1 shows this Arduino board. Next to the USB port, a SAMD21 microcontroller from Microchip connects to a host computer and acts like a bridge to the onboard FPGA at the same time, as both share pins of the MKR pin header. The NINA W102 module made by U-blox, containing a full-featured dual-core ESP32, connects to the FPGA as well. In its original condition the NINA module contains a special software from Arduino, to communicate via Wi-Fi and Bluetooth. An onboard Flash chip contains a predefined logic from Arduino for the FPGA. But for our audio application we will change the setup of all three devices for our own purpose.

#### **Setting Up the Toolchain**

First, we must prepare our toolchain to support all desired devices. For the NINA/ESP32, follow the tutorial at [2] to install the ESP32 package to the Arduino IDE. For the SAMD21 you find the official Arduino sources by searching for "SAMD" in the board manager library. As we are planning to upload our own bitstream to the FPGA, we must download the design software Quartus Prime Lite from Intel [3]. The usual way to upload a new bitstream to these kinds of FPGAs is using a special JTAG adapter. Thankfully, there is an Arduino library under [4] to upload own bitstreams by embedding it into a regular header file of the Arduino sketch directly.

Quartus will output the created logic in several output formats. One of them is the tabular text file, containing the configuration data for use outside of the Quartus software. To feed our JTAG emulation with these data, we

must flip the bit order of the file to generate an Arduino-compatible header file. We can use the small program *vidorcvt* from [5] on the command line:

#### vidorcvt.exe < FPGA.ttf > bitstream.h

At each boot of the SAMD21, when the function setup\_fpga() is called within our Arduino sketch, the FPGA is configured with the content of bitstream.h copied to the onboard SPI-Flash during flashing the SAMD21. This occurs at every power-up, as FPGAs are losing their logic on a voltage loss.

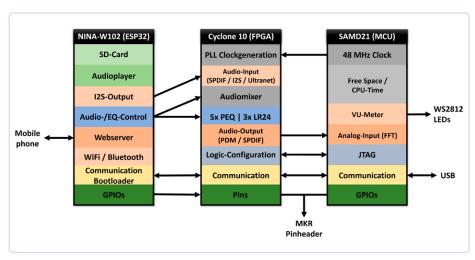

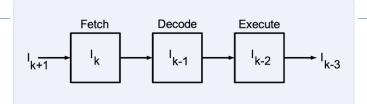

#### Mixing C Code and Digital Logic

A digital audio system consists of both time-critical real-time processing, as well as less critical, but more complex calculations based on user inputs. The former use the fast and parallel processing properties of the FPGA; for the latter we benefit from the advantages of microcontrollers to handle complex calculations. Figure 2 shows the connection of all three devices on the MKR board: the USB port is used for software updates of the USB controller (SAMD21) piggy-backing the bitstream of the FPGA and programming the onboard SPI Flash during the upload-process. Once we have a working FPGA, we can route some communication lines through the FPGA to the NINA/ESP32 to program it via the built-in bootloader. Furthermore, the SAMD21 is used for calculating some nice VU-meter effects and has a lot of free program space and calculation time remaining for your own ideas.

The FPGA will be able to receive digital audio data from a variety of sources: either from a coaxial or optical S/PDIF or TOSLINK jack (stereo), an analog-to-digital converter with stereo I2S output, the ESP32 (with playback from MP3 files on an SD Card) via I2S and finally, the already mentioned 16-channel input from the Behringer Ultranet signal. In this article, I will focus on the digital signal processing aspect of the project. For testing, I used jumper wires for all connections. To read data from a micro SD card, you can use an extension board like the Arduino MKR SD Proto Shield or a similar module. To implement all these audio inputs more neatly in a more advanced version, it would be necessary to create a small motherboard with two rows of pins matching the headers of the MKR Vidor 4000 and equipped with all the appropriate connectors.

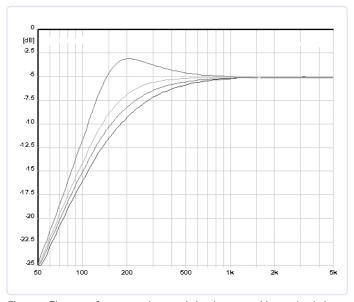

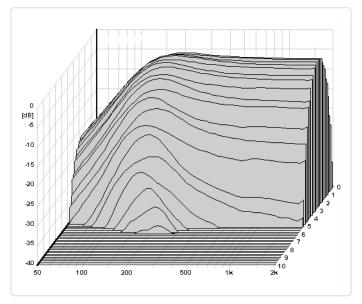

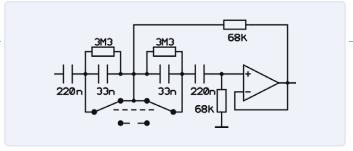

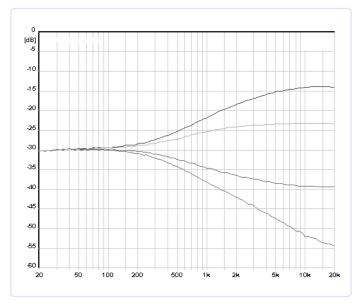

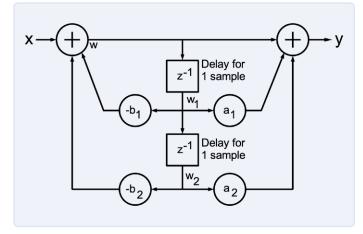

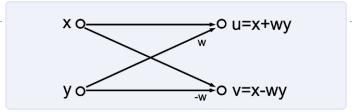

Besides processing all the input signals, the FPGA will be equipped with five full-featured parametric equalizers followed by a Linkwitz-Riley Crossover filter to feed a 2.1 stereo set with connected subwoofer — we want to hear and "feel" the sound, right? As mentioned, some calculations are better for a microcontroller. Calculating the filter coefficients for the used IIR filters is certainly a task for a CPU rather than FPGA, but we get back to this in a moment.

#### Webserver

Another task for the ESP32 is the communication with the environment – specifically with

Figure 2: Overview of the multi-controller-system.

Figure 3: AES/EBU signal containing up to 24 bits of digital audio data.

Figure 4: Inter-IC-Sound (I2S) signal.

our mobile phone. As shown in many projects in Elektor, we are using the SD card to load the webpages and we are using the well-known Bootstrap framework to style our interface. With some basic HTML knowledge, it is possible to create a fancy and responsive user interface. A small Javascript within the website is polling some update information using AJAX over a REST-like API fed by the webserver of the ESP32, like current title, progress, volumes, equalizer settings, and more. User inputs are passed to the file cmd.php. Even though we are not implementing a full-blown PHP server, the browser will transmit the parameters which our webserver will parse and call the desired functions. For example the call /cmd.php?mixer:volume:main=-6 will be translated to the C function executeComman d("mixer:volume:main@-6") and set the volume to -6 dB. The same command can be sent via USB as well. With this ASCII-based command system, it would also be very easy to add MQTT commands to the firmware, like fbape/mixer/volume/main -6, for example.

#### **From Stereo to Multi-Channel**

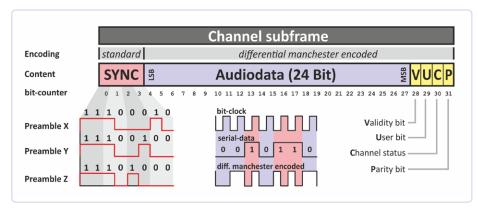

But enough said about web interfaces - our audio data waits to be processed. As FPGAs are great to handle parallel tasks, we can implement the inputs for all desired signals as parallel logic. The idea is, to convert the serial data (mainly S/PDIF, Ultranet and I2S) into individual 24-bit logic vectors that we can handle quite easily. Let's start with S/PDIF and Ultranet. Both use AES/EBU, an interface for digital audio data specified in 1985. It transmits between 16 and 24 bits of stereo audio data with sample rates between 32 kHz and 192 kHz. According to the App Note [6], AES/EBU contains a data structure shown in **Figure 3**, representing a single subframe. Ultranet transmits four stereo channels on two separate lines with 48 kHz, to maintain the maximum sample rate of 192 kHz.

Most of the S/PDIF data is encoded using a differential Manchester encoding, so that the bit clock is transmitted multiplexed with the serial data (see **Figure 3** again). An exception

is the sync-block, that contains conventional bits forming the so-called "preamble", an eight-bit pattern. For the preamble three different bit patterns using invalid Manchester codes are specified. That allows us to identify the beginning of channel 1 on receiving the preamble Z which is sent every 192 subframes. The four status bits can be ignored when receiving the pure audio samples.

Now, the first task for the FPGA is to decode the Manchester-coded S/PDIF serial data. Therefore, it must collect the individual bits into a shift-register and search for the three high bits of the preamble. Within a state machine, the synchronization to the signal is monitored and the inherent bit clock of the Manchester code is restored to an internal clock signal. As the space for this article is limited, I'm not going into details of this specific block as I'm using a slightly modified VHDL block from OpenCores.org, a nice page with lots of VHDL snippets [7]. The receiver block outputs a conventional I<sup>2</sup>S signal, that is much easier to handle.

As Ultranet is using AES/EBU, as S/PDIF, we can convert our individual subframes into an I<sup>2</sup>S signal with the same receiver block. The only additional task is a channel counter, counting from channel 1 to channel 8 instead of the stereo signals of S/PDIF, synchronized to the Z preamble again.

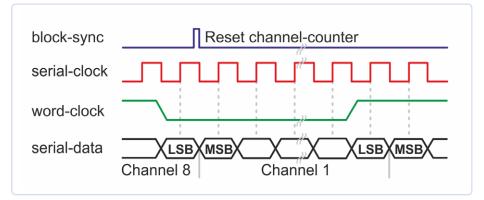

"Inter-IC Sound," or I<sup>2</sup>S (see **Figure 4**), uses a fixed serial clock (bit clock) as well as a word-select signal (also called word clock or LR clock) to transmit audio data. So at least three connection lines are necessary. Here we must create a logic, that searches for the falling or rising edges of the word-select as synchronization. So, we can read individual bits into a shift register on each rising edge of the serial clock. One pitfall is, that the word-select is shifted by one clock cycle.

#### **The Digital Logic**

So, let's dive into the digital logic (see **Listing 1**). First, we define our input and output signals. Here we need the main clock, which must be much faster as the signal to be read, followed by the other signals, each defined as logic signal as we are reading serial data bits. The output then is defined with two

logic vectors with a width of 24 bit as we are processing all audio data with this bit depth within the FPGA. 16-bit signals will be scaled to 24-bit by bit-shifting by 8 bits to the left to keep the 0 dB Fullscale (dBfs) level.

Now we are ready to detect the edges of our three signals. The way to do this is shown in Listing 2. In this case, it is the bit clock that is considered, but for the word clock it is comparable. Here we are only reacting on the positive edge and will create a process for this. Within this process, we will use a shift register to detect a change within the serial clock sclk by comparing it to the previously sampled zsclk. If a positive edge is detected, we set b\_pos\_edge to 1, otherwise to 0.

On each positive edge of b\_pos\_edge we will then store the read bit into a shift register. As in the I2S signal the first received bit is the most significant bit, we must add the current serial bit sdata from the right into the register while removing the left most bit (see Listing 3).

We can now take the word clock into account to copy the correct bits to the output logic vectors. As the word clock is shifted by one bit clock, the shift register has more bits than the designated payload data. Finally, we remove the least significant 8 bits from the 2× 32-bit buffer and output the desired 24-bits (Listing 4).

#### **FPGA Audio Processing**

All serial audio data is now within our FPGA represented in handy logic vectors with a bit depth of 24 bits. These bits contain signed audio-samples and will be updated with a sample rate of 48 kHz (or whatever the original signal will use). This represents a fairly large number of signals: assuming an external stereo ADC connected via I2S, the I2S stream from the ESP32's SD card, and the AES/EBU input (which represents between 2 channels in case of S/PDIF and 2 × 8 channels in case of Ultranet), there are between 6 and 20 input signals now. Great!

#### **Going Further**

With the toolchain prepared and the foundational concepts of FPGA and microcontroller interaction established, we've also begun our journey into audio signal processing by

#### Listing 1: Defining the inputs and outputs.

```

entity i2s_32bit_rx is

port (

c1k

: in std_logic := '0'; -- Mainclock

: in std_logic := '0'; -- I2S serial-clock

sclk

: in std_logic := '0'; -- I2S serial-data

sdata

wordclk : in std_logic := '0'; -- I2S word-clock

out_l : out std_logic_vector(23 downto 0) := (others=>'0');

out_r : out std_logic_vector(23 downto 0) := (others=>'0');

sync_out : out std_logic := '0' -- high for 1 clock if successful

);

end i2s_32bit_rx;

```

#### **Listing 2: Syncing with the clock.**

```

detect_edge : process(clk)

begin

if rising_edge(clk) then

zsclk <= sclk; -- save current serial-clock</pre>

if zsclk = '1' and bclk = '0' then

b_pos_edge <= '1';</pre>

b_pos_edge <= '0';</pre>

end if;

end if;

end process;

```

#### Listing 3: Bit-shifting the received signal.

```

get_data : process(clk)

begin

if rising_edge(clk) then

if b_pos_edge = '1' then

s_shift <= s_shift(s_shift'high - 1 downto 0) & sdata;</pre>

end if;

end if;

end process;

```

#### Listing 4: Processing the output data.

```

detect_sample : process(clk)

begin

if rising_edge(clk) then

if wclk_neg_edge = '1' then

signal_l <= s_shift(62 downto 31);</pre>

elsif wclk_pos_edge = '1' then

signal_r <= s_shift(62 downto 31);</pre>

sync_out <= '1';</pre>

sync_out <= '0';</pre>

end if;

end if;

end process:

-- take only 24 bits beginning at MSB (signed-bit)

output_l <= signal_l(31 downto 8);</pre>

output_r <= signal_r(31 downto 8);</pre>

```

converting stereo data into a manageable format for FPGA-based manipulation. In the next part of this series, we'll build on this groundwork to implement advanced features like volume control, parametric equalizers, dynamic compressors, and crossover filters, bringing the project to life as a full-fledged digital audio system. The documentation is available on my GitHub repository [8]. Stay tuned for the second part in the next edition of *Elektor*!

230632-01

#### **Questions or Comments?**

Do you have questions or comments about this article? Feel free to contact the author at christian@noeding-online.de, or contact Elektor at editor@elektor.com.

#### **About the Author**

Dr.-Ing. Christian Nöding studied electrical engineering at the University of Kassel from 2003 to 2009. He then began working at the department of Power Electronics at the University of Kassel and completed his PhD in 2016. His main interests lie in the design and control of electronic power converters for decentralized energy supply, stage and lighting as well as music and digital audio technology.

- Dogan and Ahmet Ibrahim, Practical Audio DSP Projects with the ESP32 (Elektor 2023) www.elektor.com/20558

- > Elektor Audio Collection (USB Stick) www.elektor.com/19892

#### WEB LINKS =

- [1] The Arduino MKR Vidor 4000: https://docs.arduino.cc/hardware/mkr-vidor-4000/

- [2] ESP32 Package for the Arduino IDE: https://docs.espressif.com/projects/arduino-esp32/en/latest/installing.html

- [3] Quartus Prime Lite from Intel: https://www.intel.com/quartus

- [4] An Arduino library that uploads your custom FPGA bitstream: https://github.com/HerrNamenlos123/JTAG\_Interface

- [5] Software for Arduino Vidor boards: https://github.com/wd5gnr/VidorFPGA/tree/master/C

- [6] Application Note from NTI Audio: https://www.nti-audio.com/Portals/0/data/en/NTi-Audio-AppNote-AES3-AES-EBU.pdf

- [7] Simple AES3 or SP/DIF receiver on OpenCores: https://opencores.org/projects/aes3rx

- [8] Author's GitHub repository: https://www.github.com/xn--nding-jua

# FREE Download Now! Mac, Windows and Linux

# Edit and color correct using the same software used by Hollywood, for free!

DaVinci Resolve is Hollywood's most popular software! Now it's easy to create feature film quality videos by using professional color correction, editing, audio and visual effects. Because DaVinci Resolve is free, you're not locked into a cloud license so you won't lose your work if you stop paying a monthly fee. There's no monthly fee, no embedded ads and no user tracking.

#### **Editing, Color, Audio and Effects!**

DaVinci Resolve is the world's only solution that combines editing, color correction, visual effects, motion graphics and audio post production all in one software tool! You can work faster because you don't have to learn multiple apps or switch software for different tasks. For example, just click the color page for color, or the edit page for editing! It's so incredibly fast!

#### **Professional Editing**

DaVinci Resolve is perfect for editing sales or training videos! The familiar track layout makes it easy to learn, while being powerful enough for professional editors. You also get a library full of hundreds of titles, transitions and effects that you can add and animate! Plus, DaVinci Resolve is used on high end work, so you are learning advanced skills used in TV and film.

#### **Creative Color Correction**

DaVinci Resolve's color page is Hollywood's most advanced color corrector and has been used on more feature films and television shows than any other system! It has exciting new features to make it easier to get amazing results, even while learning the more advanced color correction tools. There's PowerWindows<sup>TM</sup>, qualifiers, tracking, advanced HDR grading tools and more!

#### **Designed to Grow With You**

DaVinci Resolve is designed for collaboration so as you work on larger jobs you can add users and all work on the same projects, at the same time. You can also expand DaVinci Resolve by adding a range of color control panels that let you create unique looks that are impossible with a mouse and keyboard. There's also edit keyboards and Fairlight audio consoles for sound studios!

DaVinci Resolve 19 Free

DaVinci Resolve Micro Color Panel Only £425

Learn the basics for free then get more creative control with our accessories!

usive of VAT

turned the Elektor Sand Clock of 2017 into a clock that writes the time on glowin-the-dark film instead of in sand. A few years later, the Sand Clock was redesigned to use the Raspberry Pi Pico instead of the Arduino UNO — this version is currently available in the Elektor Store. Therefore, it is only logical to also reissue the laser head modification for the current Sand Clock. And why not use the clock to make drawings? In this article, we explain how you can achieve this.

In January 2017, Elektor published the Sand Clock, a novel clock that wrote the time in a sand bed [1]. It was based on an Arduino UNO. A year later, a modification was published [2] that replaced the sand bed by a sheet of glow-in-the-dark film and the pen by an ultraviolet laser. The laser clock was more discreet than the Sand Clock, as it didn't need to shake the sand bed every time to clear it before writing the new time.

A second update [3] added a stand to allow the laser clock to be placed vertically on a horizontal surface instead of hanging it on a wall. A PIR sensor was added too, so the clock could be made to write the time only if there was someone around to see it.

A few years later, the Sand Clock with the PIR sensor option was redesigned to use the Raspberry Pi Pico instead of the Arduino UNO. This version of the Sand Clock is currently available in the Elektor Store. Therefore, it is only logical to also reissue the laser head modification for the current Sand Clock, which is what we did.

#### **Hardware Update**

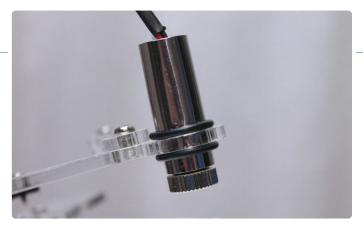

The new laser head kit is almost identical to the kit from 2018, except for the laser holder arm that was made a bit more robust. Instead of an open, clamping grip, the holder is now a closed ring that cannot break, at least not easily (Figure 1). The laser is kept in place with two rubber rings with the arm sandwiched in between (Figure 2). Because the rest of the pantograph remained the same, assembling it is identical to the way described in 2018. Note that the stand-offs that carry the sand bed must be turned upside down for use with the laser head (Figure 3).

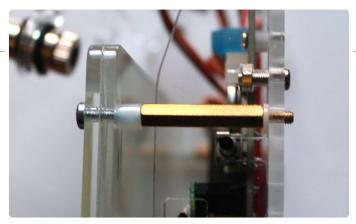

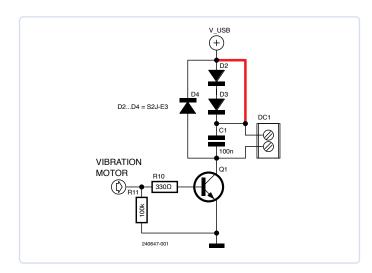

The UV laser replaces the two vibration motors used by the Sand Clock to level the sand. These motors are powered with a voltage of about 3 V. Diodes D2 and D3 take care of lowering the 5-V power supply to a

Figure 1: The new laser head mount has a ring rather than a grip to hold the laser.

Figure 2: The laser is fixed with two rubber rings.

suitable level. The laser, on the other hand, needs a 5 V supply, and so diodes D2 and D3 must be bypassed, see Figure 4. This is easily done by running a length of wire from the 5-V pin of the PIR connector to the M+ pin of the vibration motor's screw terminal (Figure 5). That's the only modification required for the circuit board.

Note that the new laser head is compatible with the original Arduinobased Sand Clock from 2017. It requires a similar modification for the laser's power supply as described above. Refer to [2] and [3] for the details.

#### **Software Update**

The software of the Raspberry Pi Pico-Based Sand Clock has been updated to drive the laser instead of the vibration motors. The main changes are the dimensions of the new pantograph arms that differ slightly from the Sand Clock and, of course, the On/Off control of the laser that replaces the vibration motor control.

While we were working on the new software, it was thought interesting to add a vector-drawing option to the clock. The functions required to draw lines, arcs, and circles were already available in the clock's software, and the observant user might have noticed the comments describing serial commands for them in the source code. Therefore, we added the possibility to receive a drawing script and execute it. Instead of just writing the time, the clock can now also be used to create ephemeral works of art (Figure 6).

Furthermore, as the Raspberry Pi Pico has plenty of program memory, scripts can also be placed in memory. This allows you to create animations, turning the clock in a fun decorative object for, e.g., Christmas or other special events. Making a script is a bit laborious, though, as it requires you to convert a drawing into line and arc segments with millimeter coordinates. However, a PCB design program like KiCad or a mechanical 2D-design program capable of drawing in millimeters can help you here. We've left the implementation of a g-code interpreter as used by CNC machines as an exercise to the reader.

#### **Drawing Commands**

The commands available for drawing are simple text-based commands that can be sent over a serial link. Make sure that the serial port speed of your terminal program is set to 115,200 baud (with eight databits, no parity, one stopbit, i.e., 115200n81). Also, serial commands must be terminated with both CR (carriage return) and LF (line feed). In Tera Term this is configured in Setup → Terminal → New-Line → Transmit: CR+LF. To send a script file using Tera Term, use the File → Send File command.

Figure 3: The stand-offs must be faced pointy threaded-side down.

Figure 4: The red line shows the electrical modification of the main board.

Figure 5: The electrical modification in practice.

The following commands can be used:

- f: Script start, not required when a script is stored in internal memory. @: End of script, not required when a script is stored in internal memory.

- pld: Laser head down.

- plu: Laser head up.

- le: Laser enable (on).

- ld: Laser disable (off).

Figure 6: A script received over the serial link is being processed.

#### **Moving**

pm  $\langle x \rangle$   $\langle y \rangle$  and ps  $\langle x \rangle$   $\langle y \rangle$

Move to position (x,y). Both commands pm and ps produce the same result. The values of <x> and <y> are in millimeters. The horizontal origin (x = 0) of the canvas is in the horizontal middle of the bed, therefore x-values may be negative. The vertical origin (y = 0) is 10 mm below the bed; therefore, when drawing, the y-value should not be smaller than about 10 mm. The exact limits depend on your construction and calibration. Example:

Move to x = 25 mm, y = 48 mm (i.e., up and to the right):

pm 25 48

#### **Arcs and Circles**

pa <rx> <ry> <ab> <ae>

Starting at the current position, draw an arc with a horizontal radius of  $\langle rx \rangle$ , a vertical radius of  $\langle ry \rangle$ , and from angle  $\langle ab \rangle$  to angle  $\langle ae \rangle$ . If the end angle <ae> is greater than the begin angle <ab>, the laser will move counterclockwise, else the laser moves clockwise. The angles are in radians, unless they are postfixed with the letter d, in which case they are interpreted as degrees. Example:

Draw a counterclockwise arc from 73° to 253° with a horizontal and vertical radius of 5.2 mm:

pa 5.2 5.2 73d 253d

Draw an ellipse with a horizontal radius of 5 mm and a vertical radius of 10 mm:

pa 5 10 0d 360d

Numerical values may have decimals and signs, which in theory allows for very precise positioning of the laser. In practice, however, this precision is not respected at all due to play in the pantograph joints and the wideness of the laser beam that is highly dependent on the writing height.

Note that the real origin of the pantograph (0,0) is right between the two servos that drive the arms. Therefore, it is unattainable by the laser.

The file scripts.h included in the source code available from [4] contains a few example drawings. To execute a built-in drawing script from the command line, use the command z with the number of the script as parameter (starting at 0). For example, execute built-in drawing script no. 0.:

7 0

You can, of course, add your own scripts to this file. Enjoy!

240647-01

# Firmware Update for Raspberry Pi-Pico-Based Sand

A byproduct of adapting the Raspberry Pi-based Sand Clock software for the laser head was a correction of an issue sometimes observed with the Sand Clock. When connected to a computer, everything worked fine, but when in stand-alone mode (i.e., only connected to a power supply), it would write the time just once. This issue has been fixed in V1.5. You can download it from [1].

#### **Questions or Comments?**

Do you have technical questions or comments about his article? Email the author at clemens.valens@elektor.com or contact Elektor at editor@elektor.com.

#### **Related Products**

- > Laser Pen for Sand Clock www.elektor.com/21107

- > Sand Clock Kit (based on Raspberry Pi Pico) www.elektor.com/20679

#### WEB LINKS =

- [1] Ilse Joostens & Peter S'heeren, "Sand Clock A Real Eye-Catcher," Elektor 1-2/2017: https://elektormagazine.com/magazine/elektor-201701/40130

- [2] Ilse Joostens & Peter S'heeren, "Laser Time Writer Writing with light," Elektor 1-2/2018: https://elektormagazine.com/magazine/elektor-201801/41254

- [3] Ilse Joostens & Peter S'heeren, "Laser Time Writer Revisited!," Elektor 7-8/2018: https://elektormagazine.com/magazine/elektor-201807/41746

- [4] Downloads for this article: https://elektormagazine.com/labs/laser-head-for-raspberry-pi-pico-based-sand-clock

# **ENTER THE STM32 EDGE AI CONTEST**

#### **By the Elektor Content Team**

Unleash your creativity in the STM32 Edge AI Contest! Turn bold ideas into reality with the STM32N6 and showcase your Edge AI skills. Submit a project idea by April 30, 2025, to have a chance to get a free well-equipped STM32N6570-DK Development Kit!

Explore the cutting edge of artificial intelligence and edge computing by participating in the STM32 Edge Al Contest, powered by STMicroelectronics. This is your chance to bring your most innovative Edge AI ideas to life using the STM32N6570-DK Discovery Kit. Whether you're an experienced developer or a passionate maker, this competition is your platform to demonstrate your expertise, creativity, and problem-solving skills.

#### **Timeline**

- > Deadline for Project Ideas: 30 April 2025

- > Deadline for Final Project Submissions: 1 September 2025

- > Nominees Revealed: 30 September 2025

- ➤ Grand Winner Announcement: November 2025 Stay Tuned!

#### **Prizes**

> 1st Prize: €2,500 > 2nd Prize: €1,500 > 3rd Prize: €1,000

Visit www.elektormagazine.com/stm32ai for details and to submit a project. With €5,000 in cash prizes up for grabs, the judges are looking for Edge Al-driven projects that inspire and innovate. Your journey to cutting-edge innovation starts now! ►

250006-01

#### The STM32N6570-DK Dev Kit

The first high-performance STM32 MCU with AI acceleration is your ultimate tool for advanced prototyping and development. With the STM32N6570-DK Discovery Kit, you can bring your Al vision projects to life with unparalleled ease and efficiency. Whether you're developing next-gen applications or exploring innovative prototypes, this kit has everything you need to succeed. Elevate your Al projects today!

#### **Key Features**

- STM32N657 microcontroller with Neural-ART accelerator and 4.2 MB SRAM

- STLINK-V3 debugger Effortless debugging and programming

- STMod+ & Arduino UNO connectors Expand with unmatched flexibility

- MIPI connector High-speed camera interface for seamless Al vision

- 2 USB ports Lightning-fast data transfer

- 1 Gbit Ethernet Reliable, high-speed networking

- 32 MB Hexadeca-SPI PSRAM Power your most complex tasks

- Audio Jack and Codec— Built-in audio for versatile applications

- MicroSD Card Slot Simplify storage expansion

- 5" capacitive multi-touch display

- 2 User LEDs and 3 Buttons

- ST AI Camera Module included

- Fan-Out Board with mikroBUS socket and Grove connectors included

#### Find out more

https://st.com/en/evaluation-tools/stm32n6570-dk.html

The ST Neural-ART Accelerator enables the execution of advanced embedded AI applications on an MCU.

- \* Significantly reduces CPU load.

- \* Increases frames per second.

#### By Alain Romaszewski (France)

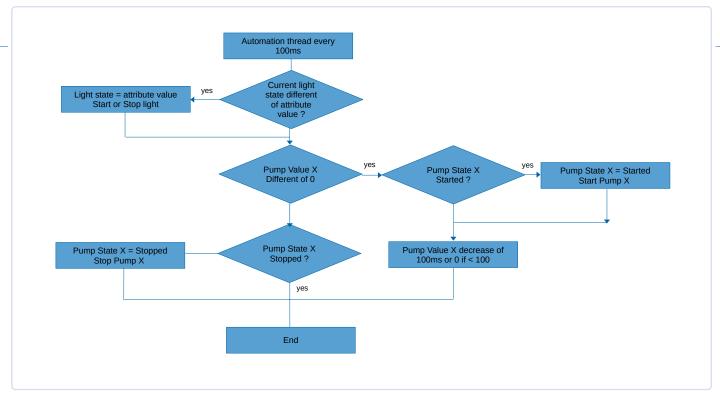

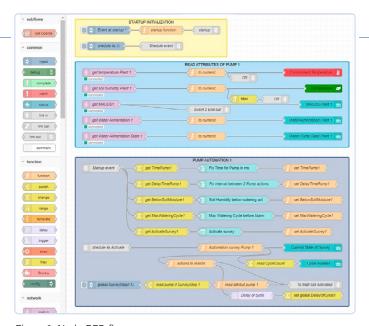

This project was designed to care for indoor plants or a greenhouse during times when you may be away, while also storing data to analyze and optimize watering cycles. It uses the STM32WB5MM-DK board with multiple sensors and Zigbee communication, alongside software like Node-RED and Zigbee2MQTT for automation and remote control. The project was entered in the ST Wireless Innovation competition organized by Elektor and ST — and won the second prize.

My goal was to create a multi-sensor environmental monitoring system for plants and greenhouses, using a wireless development board from STMicroelectronics and various sensors to measure soil moisture, temperature, humidity, air quality, and light conditions. It wirelessly transmits data via the Zigbee protocol, with the ability to remotely control irrigation and lighting, and stores the collected data in an SQL database. Automation is managed through Node-RED, allowing real-time adjustments and remote monitoring through a web interface.

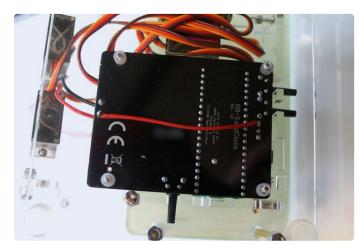

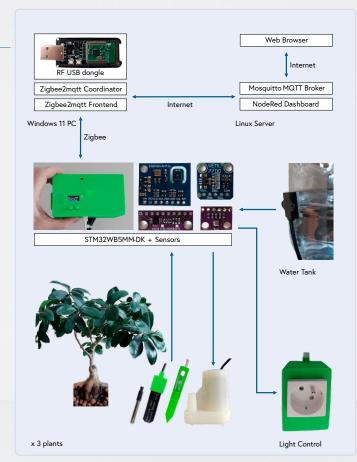

An overview of the project is shown in Figure 1. The STM32WB5MM-DK development board is coupled to a custom-made extension shield, all integrated in a 3D-printed case. This main module integrates several internal sensors to measure environmental conditions. External sensors are used to monitor soil moisture and soil temperature for three different plants. For water supply management, the board controls the irrigation pumps for the three plants and checks that enough water is left in the reservoir using the sensor. When it comes to lighting, the system measures luminosity and controls the lighting based on these readings.

The data gathered by these various sensors are transmitted as attributes over the Zigbee protocol. (See more details in the text frame More about Zigbee.) A USB dongle is used as a wireless interface and the ZigBee2MQTT application, installed on a Windows 11 machine, creates a Zigbee Coordinator, which additionally bridges between ZigBee events and a remote MQTT server. Each attribute defined in the measurement system updates on the MQTT server, and any changes made on the server can be sent back to the measurement system.

Figure 1: General architecture of the project.

Figure 2: The system in use.

Figure 3: The STM32WB55MM-DK development board.

Since the data is accessible via the MQTT server, I chose to use Node-RED to subscribe to the server and track events, enabling automation. In my case, Node-RED is running on a Virtual Private Server (VPS) hosted by OVH and running Debian. The Dashboard feature of Node-RED provides a user interface accessible through a web browser from all over the world. Furthermore, all data is stored in an SQL database for further analysis. The system can be seen being used in Figure 2.

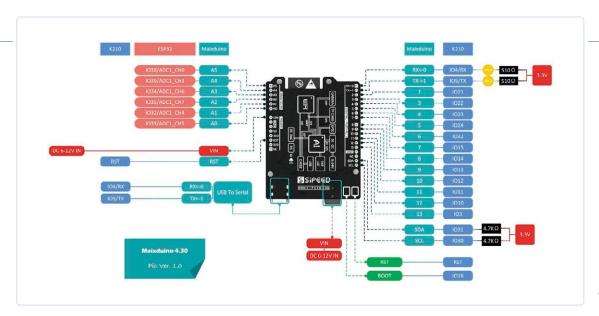

#### **Main Board**

The STM32WB5MM-DK board (Figure 3) is built around the STM32WB5MMG microcontroller from STMicroelectronics, which includes a Cortex M4 core and a Cortex M0+ communication coprocessor. To operate, the coprocessor needs to be flashed with the appropriate firmware based on the selected protocol and settings. The board provides 1 MB of flash memory and 256 KB of RAM.

I use the integrated temperature sensor on the board. This board has two I<sup>2</sup>C interfaces named I2C1 and I2C3; the temperature sensor connects to the latter. Measurements are displayed on the onboard LCD screen, and navigation through the various display screens is controlled via two buttons. Other I/Os (including the I2C1 bus and six other GPIOs) available through the Arduino-compatible set of headers are used for managing pump and light controls, water level readings, and interfacing with the soil temperature sensors.

The board is powered through USB; I also installed a battery backup to supply three low-power water pumps (operating at 3 V), used to water each plant individually from a shared reservoir. A three-part enclosure, designed for easy mounting of the PCB and the additional daughterboards (see below) while allowing button access, was 3D printed with ASA material.

#### **Sensors**

For each plant, a soil moisture sensor is used. Like all the sensors in this project, these are easy to find at various places on the internet. They are capacitive, with two electrodes forming a capacitor. A 1-MHz signal is applied to the electrodes. The capacitance between the electrodes changes with the soil's moisture content, which changes the frequency. That frequency change is finally converted into an output voltage. To protect the electronic components of the sensor, I 3D-printed an enclosure in ASA material and filled it with two-part resin. The result is shown in Figure 4.

An ADS1115 (16-bit, four-channel analog-to-digital converter) from TI connected via the I2C1 bus is used to measure the voltage from the soil moisture sensors. I found this converter and sensor arrangement to be fairly robust against interference caused by noise and long wire lengths. The soil moisture sensors have been modified to operate on

Figure 4: Soil moisture sensor.

Figure 5: Custom PCBs to connect sensors.

3.3 V by removing the voltage regulator and are connected to three inputs of the ADS1115 analog-to-digital converter. One input of the converter is used to measure the battery voltage, which is divided by two to respect the ADS1115's maximum input voltage.

To monitor soil temperature, three DS18B20 sensors from Analog Devices are used, each housed in a stainless steel tube. These sensors operate over a shared 1-wire bus. Other environmental measurements, such as temperature, humidity, and pressure, are provided by a BME280 sensor from Bosch, while CO<sub>2</sub>, total volatile organic compounds (TVOC) and indoor air quality (IAQ) levels are measured using an ENS160 sensor from ScioSense. An AHT25 sensor (Aosong) is also used for temperature and humidity compensation. Finally, luminosity is measured by a VEML7700 lux meter from Vishay. All these sensors operate on the I2C1 bus. The water level in the tank is monitored using a capacitive sensor mounted at the low level of the tank.

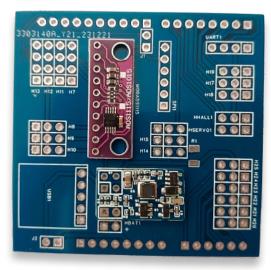

#### **External Interfaces**

An Arduino-compatible interface card was developed to simplify sensor connectivity. This card includes a switching power supply module to power the sensors and recharge the battery, which provides additional power for the pumps. It also houses the ADS1115 converter on a PCB module. Additionally, a custom interface card was made to control the pumps. This PCB has several N-channel power MOSFETs connected to the microcontroller's ports. The interface boards are shown on Figure 5; see the connected sensors in Figure 6. Another external module, equipped with a solid-state relay in a custom 3D-printed enclosure, is used to control a 230 V / 200 W light source.

#### A Short Review of the STM32WB5MM-DK

The STM32WB5MM-DK is a good development board offering many options for those working on IoT projects. On the plus side, the board is equipped with a rich set of sensors, an integrated debugger, and a well-sized flash memory and RAM. The processor also integrates the entire RF part, which is a notable advantage, although its implementation on a PCB can be tricky and adds to production costs. It's very easy to use, and the abundance of provided examples allows for quick learning and implementation.

However, there are some limitations to be aware of. The Zigbee firmware is somewhat obscure, though ST can provide the sources under certain conditions. Additionally, custom endpoints and clusters do not behave as expected, and only 8 attributes can be edited or read per request, which can be restrictive. Managing two processors with two applications can also feel cumbersome. In this respect, using the NUCLEO-WBA52CG board (also available for this ST contest) would have been more flexible, as it only has a single microcontroller.

While the board offers great functionality, the lack of examples using FreeRTOS, no external antenna option, and no Arduino support for Zigbee are drawbacks. Furthermore, the examples don't use STM32CubeMX, which complicates adding peripherals or tweaking settings. Overall, it's a solid development board, you just need to keep its limitations in mind.

#### **Programming**

Firmware (version 1.18 in this case) from the manufacturer must be downloaded into the memory area reserved for the M0+ radio processor. There are several firmware options for BLE, Thread, Zigbee, and BLE-Zigbee combinations, which are selected based on the specific use case. These firmware versions (the current version is 1.20) can be found online [1].

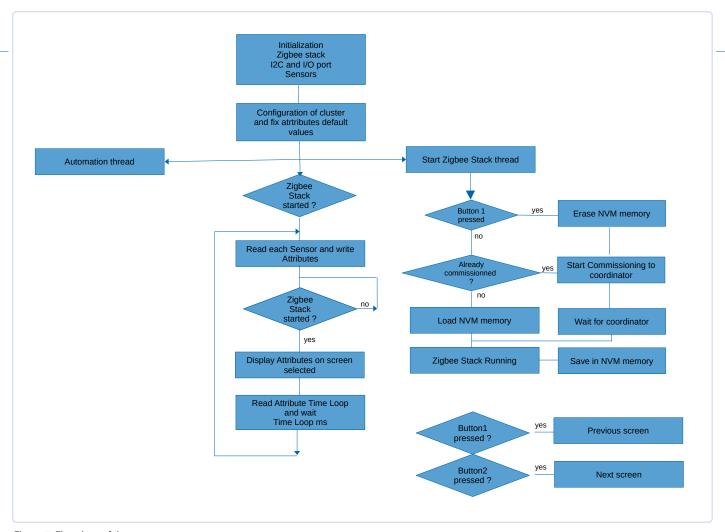

The programming for this project was carried out using the C language and the STM32CubeIDE 1.14 environment. The project is based on an example from the STM32WB library [2]. The example program can be found online [3]. The system uses a pseudo-preemptive multitask-

Figure 6: Connected sensors.

Figure 7: Flowchart of the program.

In this case, for physical measurements, a client-server architecture is used, where the client is the PC while the server is the STM32WB-5MM-DK. The Zigbee coordinator/client is responsible for regularly querying the server's attributes in order to retrieve and store the information. To perform actions, the coordinator can modify the values of the attributes on the endpoint, the latter upon receipt will execute the requested tasks, indicating its status by modifying the attributes.

To help with this, STMicroelectronics provides a pre-compiled library for cluster management. A Zigbee cluster is a group of related attributes and commands within a Zigbee device that defines a specific functionality, such as temperature measurement or lighting control, standardized across Zigbee devices for interoperability. I chose to use a standard temperature measurement cluster. The application was configured on Zigbee channel 15, with a single server endpoint. A basic cluster is automatically added by the stack. Proprietary attributes are then added to this standardized cluster.

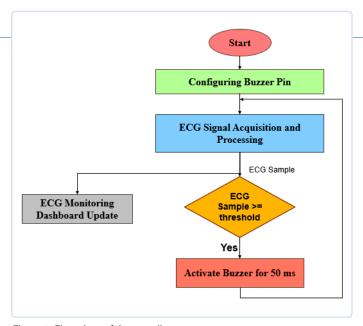

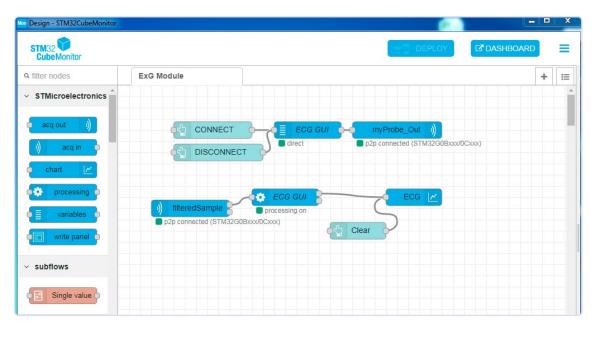

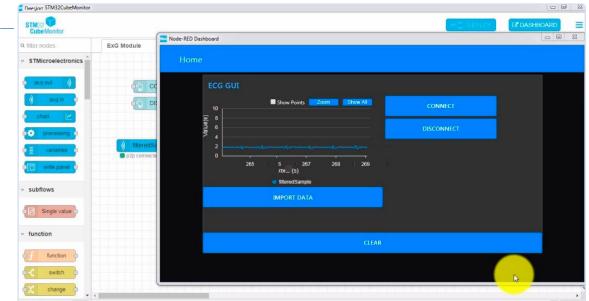

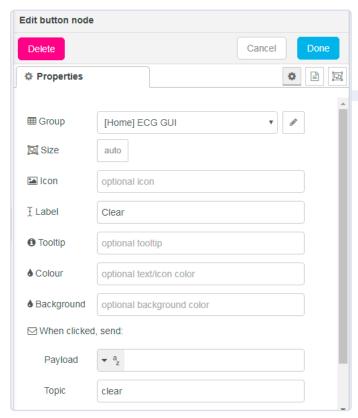

All sensors are queried cyclically, and the results are stored in the respective cluster attributes. By default, this occurs every 20 s, though the time interval can be modified through the measuring time loop cluster attribute.