## Signal Integrity and Radiated Emission

of High-Speed Digital Systems

SPARTACO CANIGGIA FRANCESCAROMANA MARADEI

## SIGNAL INTEGRITY AND RADIATED EMISSION of high-speed digital systems

**Spartaco Caniggia** *Italtel (retired) and Expert of Comitato Elettrotecnico Italiano (CEI), Italy*

**Francescaromana Maradei** Sapienza University of Rome, Italy

## SIGNAL INTEGRITY AND RADIATED EMISSION of high-speed digital systems

## SIGNAL INTEGRITY AND RADIATED EMISSION of high-speed digital systems

**Spartaco Caniggia** *Italtel (retired) and Expert of Comitato Elettrotecnico Italiano (CEI), Italy*

**Francescaromana Maradei** Sapienza University of Rome, Italy

This edition first published 2008 © 2008 John Wiley & Sons Ltd

#### Registered office

John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester, West Sussex, PO19 8SQ, United Kingdom

For details of our global editorial offices, for customer services and for information about how to apply for permission to reuse the copyright material in this book please see our website at www.wiley.com.

The right of the author to be identified as the author of this work has been asserted in accordance with the Copyright, Designs and Patents Act 1988.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, except as permitted by the UK Copyright, Designs and Patents Act 1988, without the prior permission of the publisher.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic books.

Designations used by companies to distinguish their products are often claimed as trademarks. All brand names and product names used in this book are trade names, service marks, trademarks or registered trademarks of their respective owners. The publisher is not associated with any product or vendor mentioned in this book. This publication is designed to provide accurate and authoritative information in regard to the subject matter covered. It is sold on the understanding that the publisher is not engaged in rendering professional services. If professional advice or other expert assistance is required, the services of a competent professional should be sought.

Library of Congress Cataloging-in-Publication Data

Caniggia, Spartaco. Signal integrity and radiated emissions of high-speed digital systems / Spartaco Caniggia, Francescaromana Maradei. p. cm. Includes bibliographical references and index. ISBN 978-0-470-51166-4 (cloth) 1. Electromagnetic interference. 2. Digital electronics. 3. Very high speed integrated circuits. 4. Crosstalk. 5. Signal processing. I. Maradei, Francescaromana. II. Title. TK7867.2.C36 2008 621.382'24–dc22 2008013159

A catalogue record for this book is available from the British Library

ISBN 978-0-470-51166-4 (HB)

Typeset in 10/12pt Times by Aptara Inc., New Delhi, India. Printed and bound in Singapore by Markono Print Media Pte Ltd, Singapore.

## Contents

| Lis | t of Examples                                                              | xiii |

|-----|----------------------------------------------------------------------------|------|

| For | eword                                                                      | xvii |

| Pre | face                                                                       | xix  |

| 1   | Introduction to Signal Integrity and Radiated Emission in a Digital System | 1    |

| 1.1 | Power and Signal Integrity                                                 | 2    |

|     | 1.1.1 Power Distribution Network                                           | 3    |

|     | 1.1.2 Signal Distribution Network                                          | 5    |

|     | 1.1.3 Noise Limitations and Design for Characteristic Impedance            | 7    |

| 1.2 | Radiated Emission                                                          | 9    |

|     | 1.2.1 Definition of Radiated Emission Sources                              | 9    |

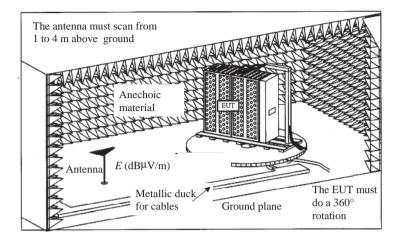

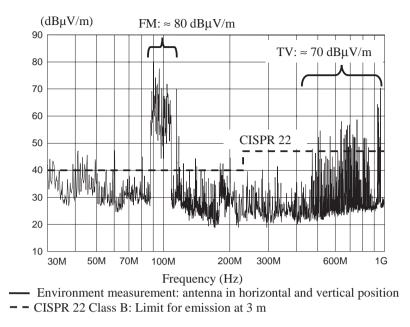

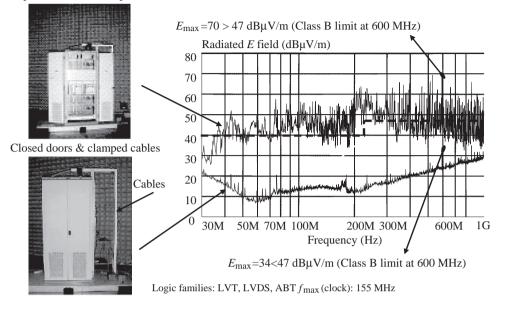

|     | 1.2.2 Radiated Emission Standards                                          | 11   |

|     | 1.2.3 Radiated Emission from a Real System                                 | 17   |

| 1.3 | Signaling and Logic Devices                                                | 19   |

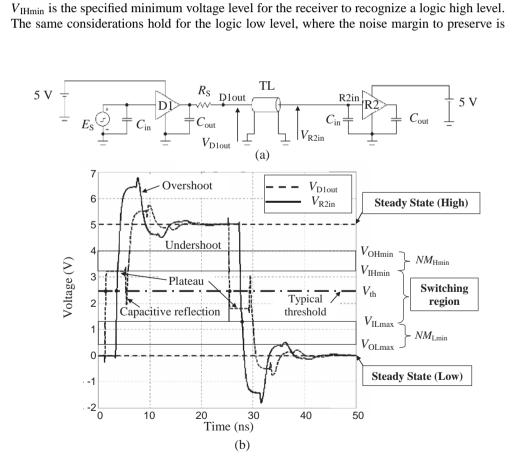

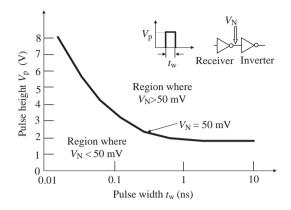

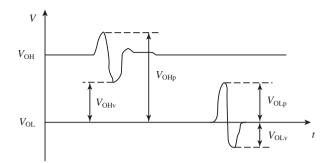

|     | 1.3.1 Overshoot, Undershoot and Plateau                                    | 20   |

|     | 1.3.2 Noise Immunity                                                       | 24   |

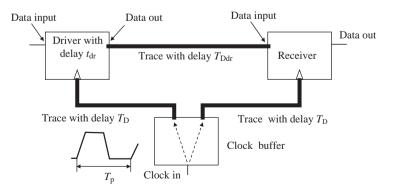

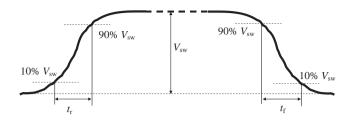

|     | 1.3.3 Timing Parameters                                                    | 25   |

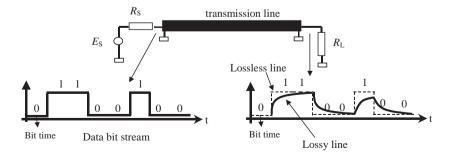

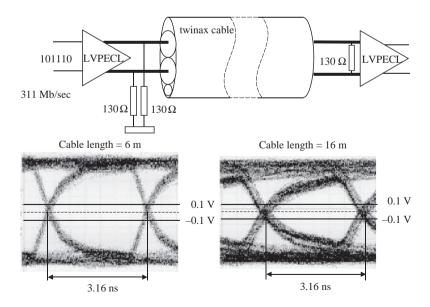

|     | 1.3.4 Eye Diagram                                                          | 27   |

| 1.4 | Modeling Digital Systems                                                   | 29   |

|     | 1.4.1 Mathematical Tools                                                   | 29   |

|     | 1.4.2 Spice-Like Circuit Simulators                                        | 30   |

|     | 1.4.3 Full-Wave Numerical Tools                                            | 31   |

|     | 1.4.4 Professional Simulators                                              | 34   |

|     | References                                                                 | 34   |

| 2   | High-Speed Digital Devices                                                 | 37   |

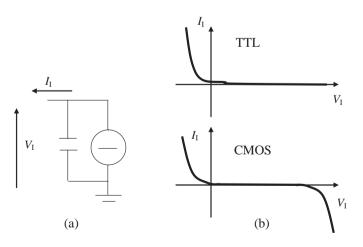

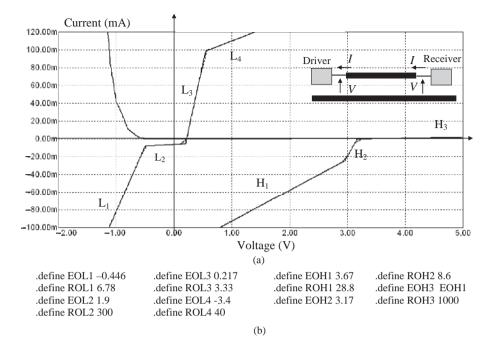

| 2.1 | Input/Output Static Characteristic                                         | 37   |

|     | 2.1.1 Current and Voltage Specifications                                   | 37   |

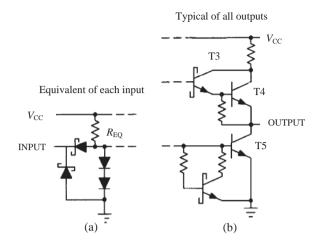

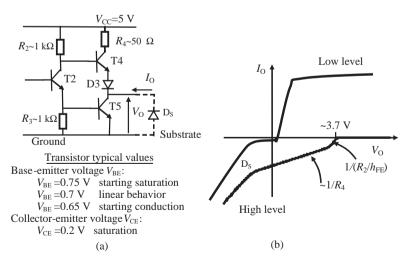

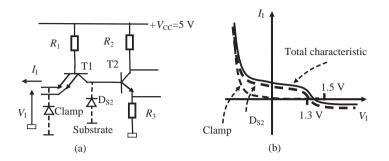

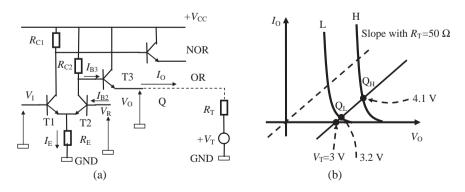

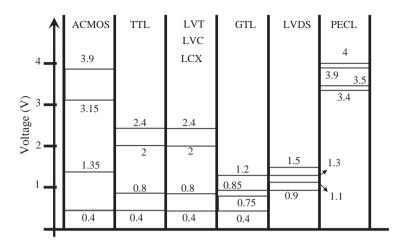

|     | 2.1.2 Transistor–Transistor Logic (TTL) Devices                            | 39   |

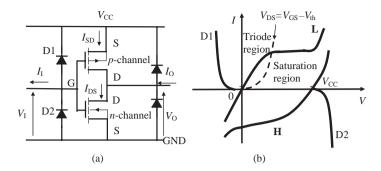

|     | 2.1.3 Complementary Metal Oxide Semiconductor (CMOS) Devices               | 42   |

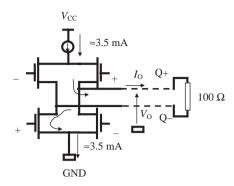

|     | 2.1.4 Emitter-Coupled Logic (ECL) Devices                                  | 44   |

|     | 2.1.5 Low-Voltage Differential Signal (LVDS) Devices                       | 45   |

|     | 2.1.6 Logic Devices Powered and the Logic Level                            | 45   |

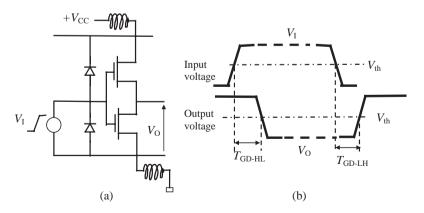

| 2.2 | Dynamic Characteristics: Gate Delay and Rise and Fall Times                | 46   |

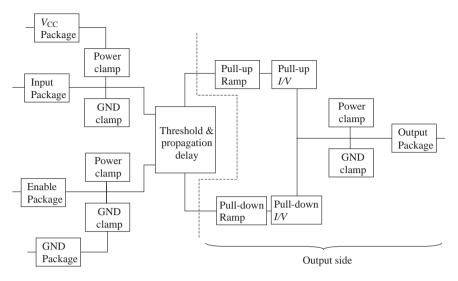

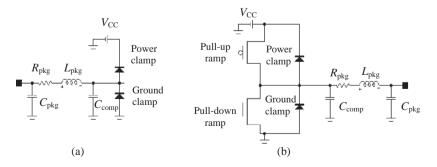

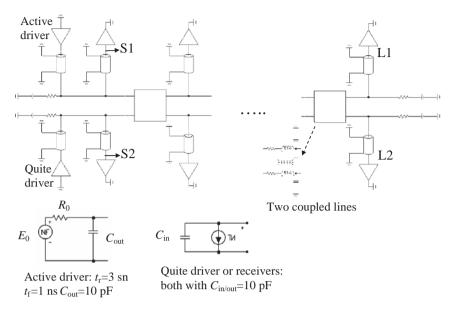

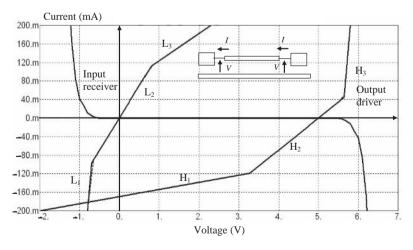

| 2.3 Driver and Receiver Modeling                                    | 48 |

|---------------------------------------------------------------------|----|

| 2.3.1 Types of Driver Model                                         | 48 |

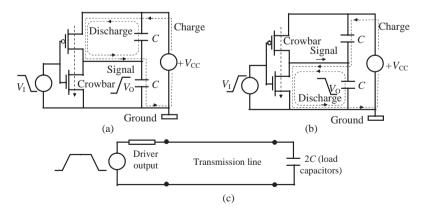

| 2.3.2 Driver Switching Currents Path                                | 50 |

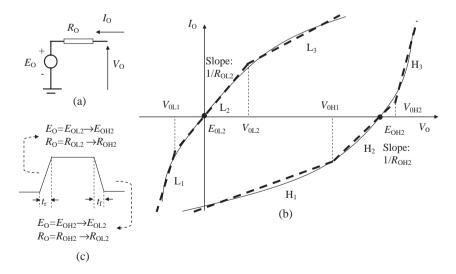

| 2.3.3 Driver Non-Linear Behavioral Model                            | 51 |

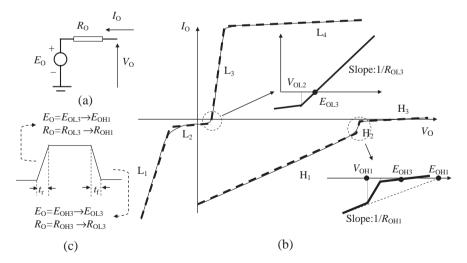

| 2.3.4 Receiver Non-Linear Behavioral Modeling                       | 53 |

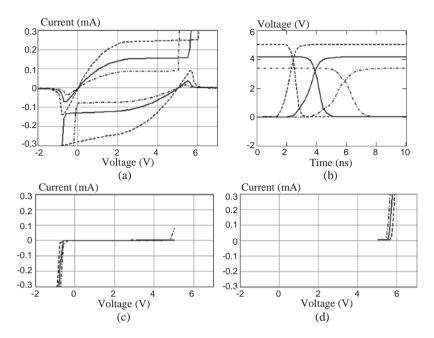

| 2.4 I/O Buffer Information Specification (IBIS) Models              | 54 |

| 2.4.1 Structure of an IBIS Model                                    | 54 |

| 2.4.2 IBIS Models and Spice                                         | 56 |

| References                                                          | 58 |

| 3 Inductance                                                        | 59 |

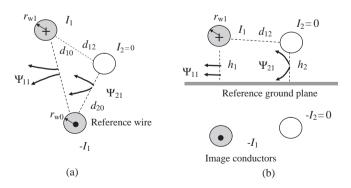

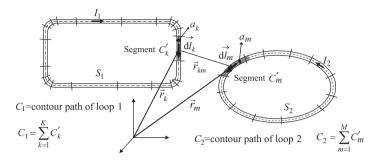

| 3.1 Loop Inductance                                                 | 59 |

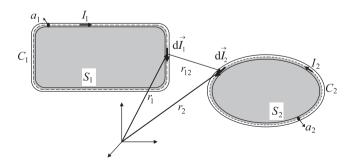

| 3.1.1 Inductances of Coupled Loops                                  | 60 |

| 3.1.2 Inductances of Thin Filamentary Circuits                      | 62 |

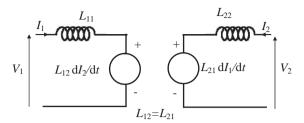

| 3.1.3 Equivalent Circuit of Two Coupled Loops                       | 62 |

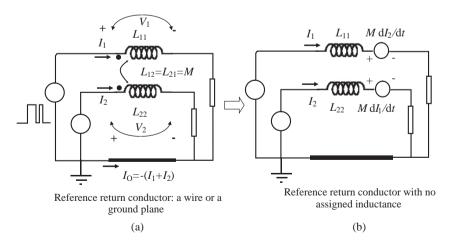

| 3.1.4 L Matrix of Two Coupled Conductors Having a Reference         |    |

| Return Conductor                                                    | 63 |

| 3.1.5 L Calculation of a Three-Conductor Wire-Type Line             | 65 |

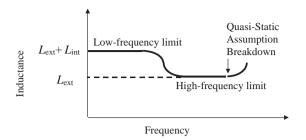

| 3.1.6 Frequency-Dependent Internal Inductance                       | 66 |

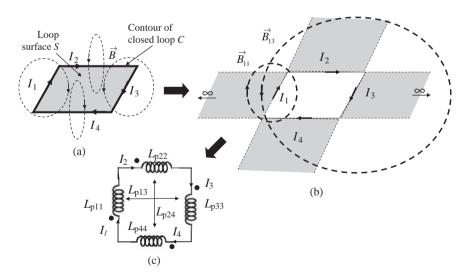

| 3.2 Partial Inductance                                              | 67 |

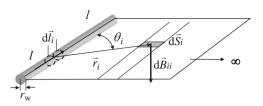

| 3.2.1 Partial Inductances of Coupled Loops                          | 67 |

| 3.2.2 Flux Area of Partial Inductance of Thin Filamentary Segments  | 68 |

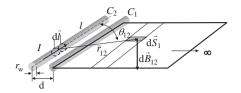

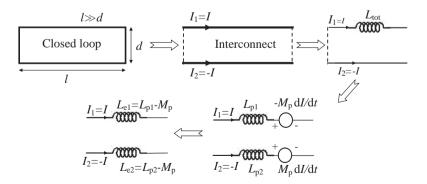

| 3.2.3 Loop Inductance Decomposed into Partial Inductances           | 70 |

| 3.2.4 Self and Mutual Partial Inductance                            | 72 |

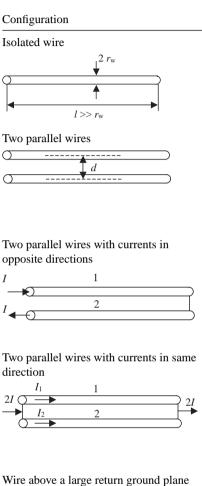

| 3.2.5 Inductance Between Two Parallel Conductors                    | 74 |

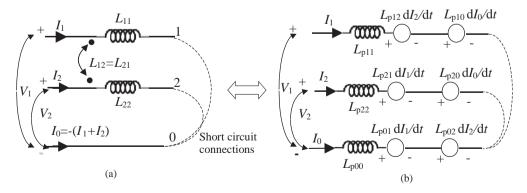

| 3.2.6 Loop Inductance Matrix Calculation by Partial Inductances     | 75 |

| 3.2.7 Partial Inductance Associated with a Finite Ground Plane      | 76 |

| 3.2.8 Solving Inductance Problems in PCBs                           | 77 |

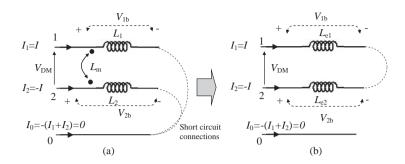

| 3.3 Differential Mode and Common Mode Inductance                    | 79 |

| 3.3.1 Differential Mode Inductance                                  | 79 |

| 3.3.2 Common Mode Inductance                                        | 80 |

| References                                                          | 81 |

| 4 Capacitance                                                       | 83 |

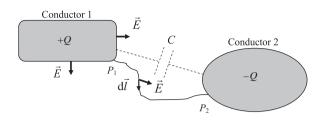

| 4.1 Capacitance Between Conductors                                  | 83 |

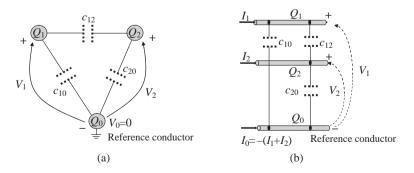

| 4.1.1 Definition of Capacitance                                     | 83 |

| 4.1.2 Partial Capacitance and Capacitance Matrix of Two Coupled     |    |

| Conductors Having a Reference Return Conductor                      | 85 |

| 4.1.3 Capacitance Matrix of n Coupled Conductors Having a Reference |    |

| Return Conductor                                                    | 86 |

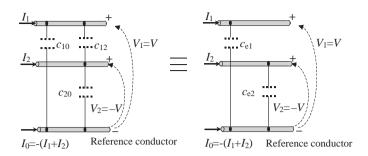

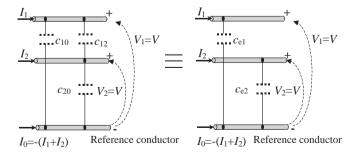

| 4.2 Differential Mode and Common Mode Capacitance                   | 87 |

| 4.2.1 Differential Mode Capacitance                                 | 87 |

| 4.2.2 Common Mode Capacitance                                       | 88 |

| References                                                          | 89 |

| 5   | Reflection on Signal Lines                                                   | 91  |

|-----|------------------------------------------------------------------------------|-----|

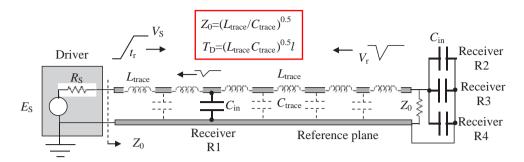

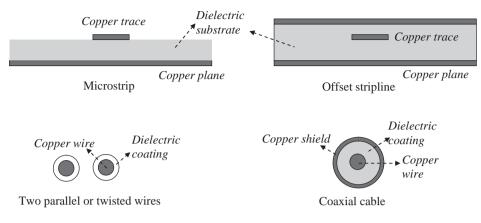

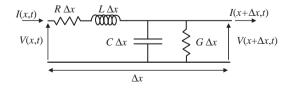

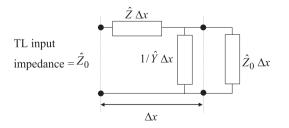

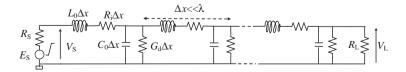

| 5.1 | Electrical Parameters of Interconnects                                       | 91  |

|     | 5.1.1 Typical Interconnects                                                  | 91  |

|     | 5.1.2 Equivalent Circuit of a Short Interconnect                             | 92  |

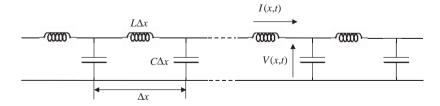

|     | 5.1.3 Lossless Transmission Lines                                            | 94  |

|     | 5.1.4 Transmission-Line Modeling by Using Partial Inductances                | 96  |

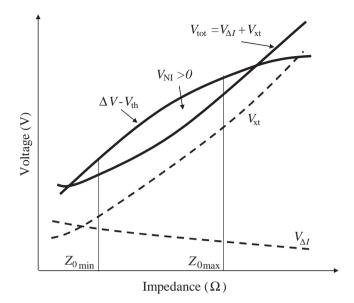

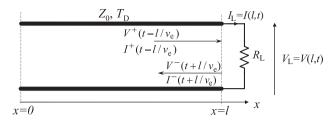

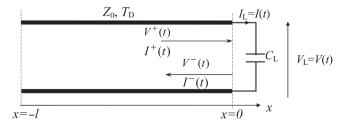

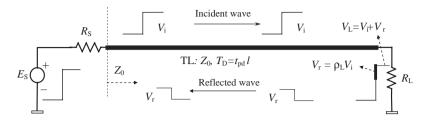

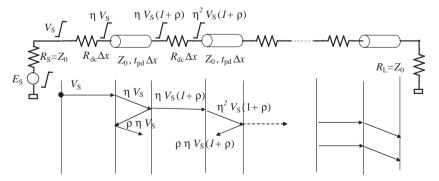

| 5.2 | Incident and Reflected Waves in Lossless Transmission Lines                  | 96  |

|     | 5.2.1 Resistive Discontinuity                                                | 97  |

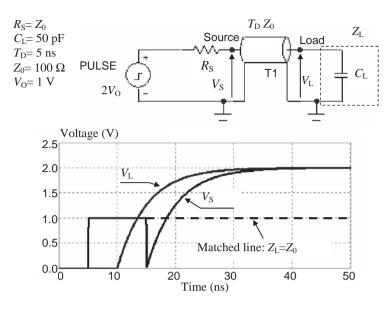

|     | 5.2.2 Capacitive Discontinuity                                               | 97  |

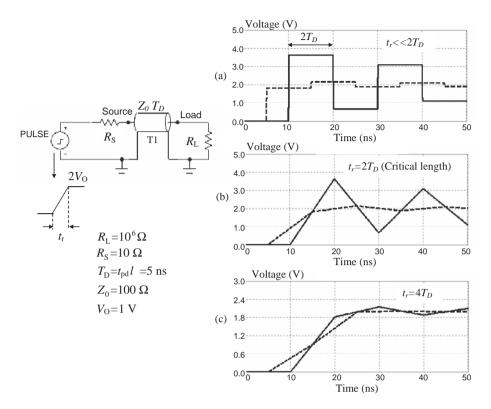

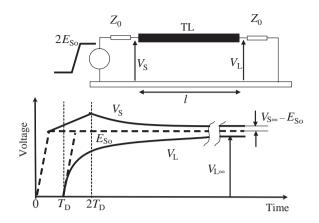

|     | 5.2.3 Reflections in Interconnects Terminated with Resistive Loads           | 99  |

|     | 5.2.4 Critical Length of Interconnects                                       | 100 |

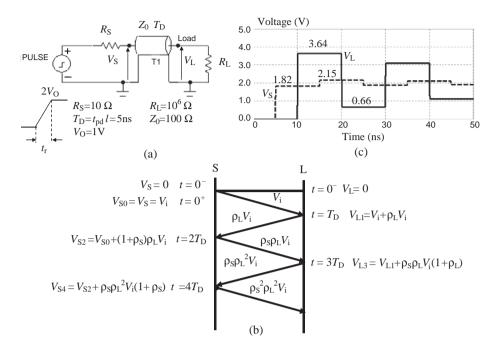

|     | 5.2.5 Lattice Diagram for Reflection Calculation                             | 101 |

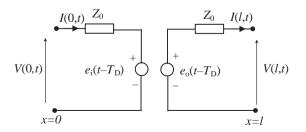

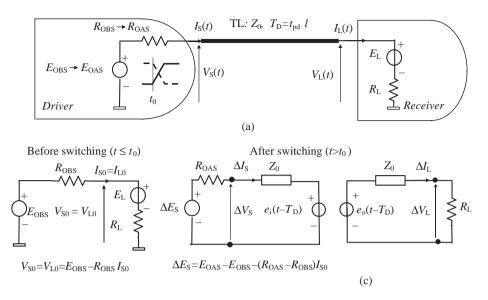

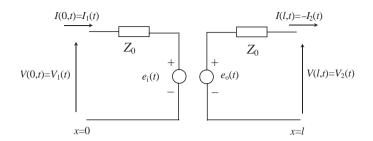

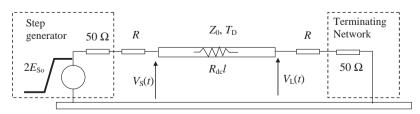

|     | 5.2.6 Exact Model of a Lossless Transmission Line                            | 102 |

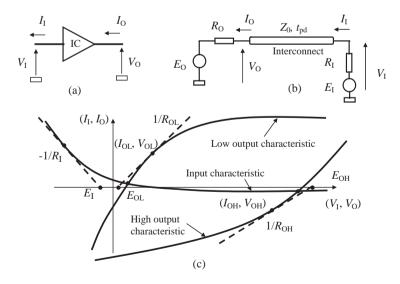

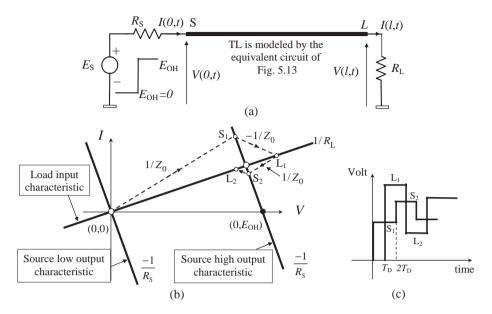

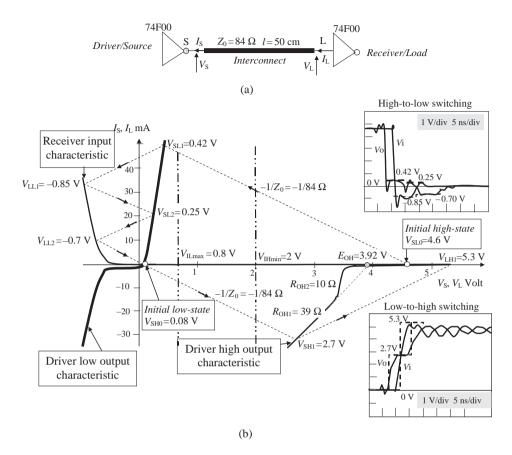

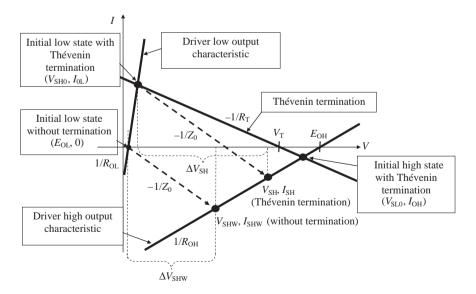

|     | 5.2.7 Graphical Solution for Line Voltages                                   | 105 |

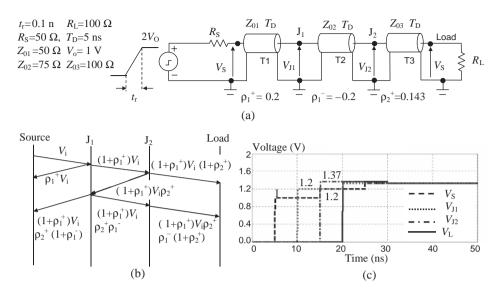

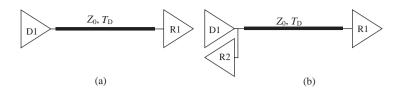

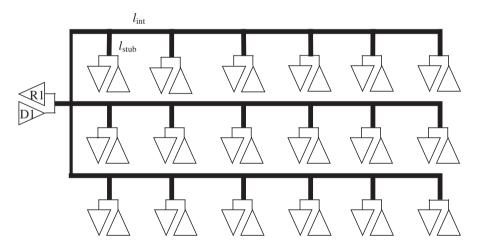

| 5.3 | Signal Distribution Architecture                                             | 109 |

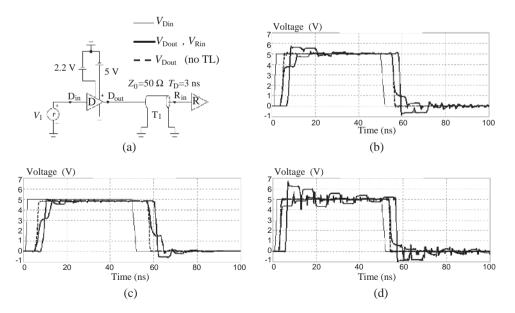

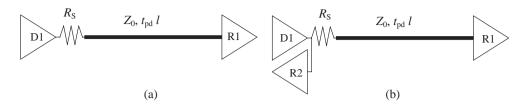

|     | 5.3.1 Point-to-Point Structure                                               | 110 |

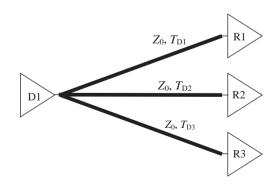

|     | 5.3.2 Star Structure                                                         | 110 |

|     | 5.3.3 Chain Structure                                                        | 111 |

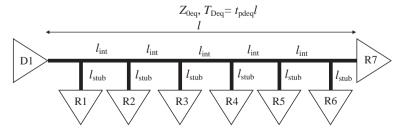

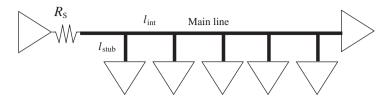

|     | 5.3.4 Bus Structure                                                          | 112 |

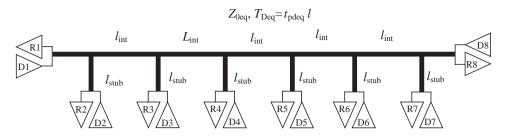

|     | 5.3.5 H-Tree Structure                                                       | 112 |

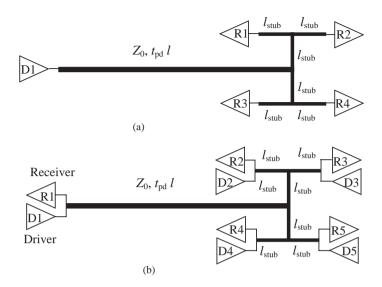

|     | 5.3.6 Comb Structure                                                         | 112 |

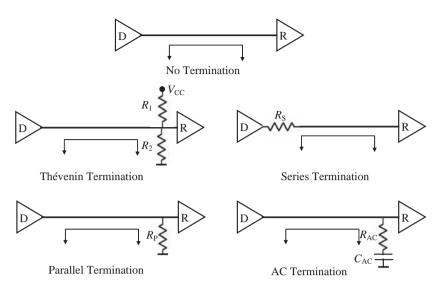

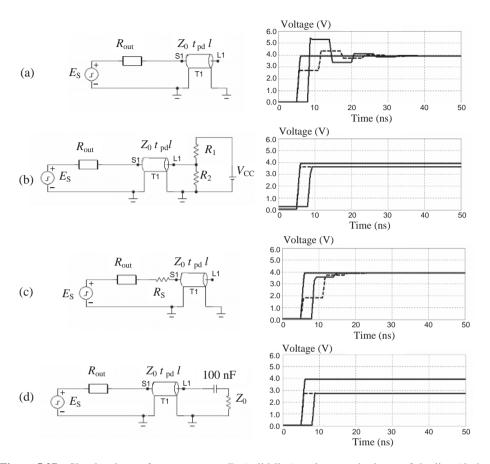

| 5.4 | Line Terminations                                                            | 114 |

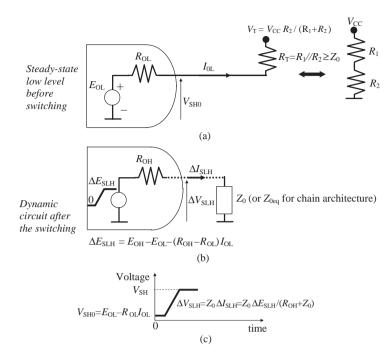

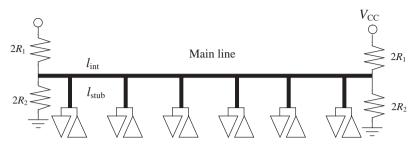

|     | 5.4.1 Thévenin Termination                                                   | 114 |

|     | 5.4.2 Series, Parallel, and AC Terminations                                  | 117 |

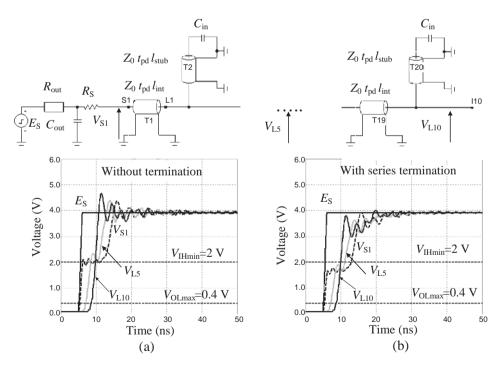

|     | 5.4.3 Series Termination and Comparison with Other Terminations by           |     |

|     | Circuit Simulations                                                          | 117 |

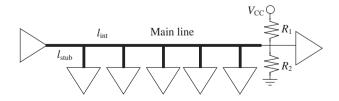

|     | 5.4.4 Thévenin Termination Applied to Chain Structures and                   |     |

|     | Circuit Simulations                                                          | 118 |

|     | 5.4.5 Series Termination Applied to Chain Structures and Circuit             |     |

|     | Simulations                                                                  | 120 |

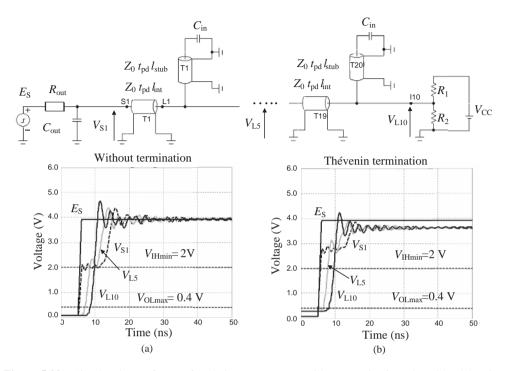

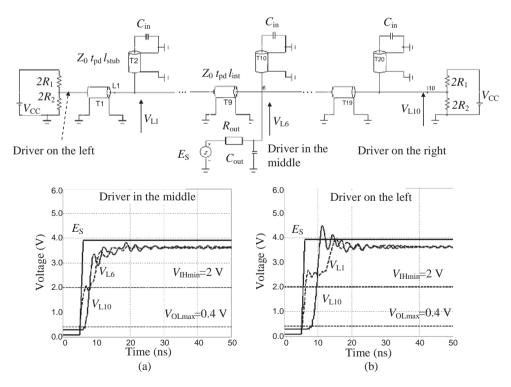

|     | 5.4.6 Thévenin Termination Applied to Bus Structures and Circuit Simulations | 121 |

|     | 5.4.7 Termination and Interconnection Structures                             | 123 |

|     | 5.4.8 Termination Performance                                                | 123 |

|     | References                                                                   | 124 |

| 6   | Crosstalk                                                                    | 125 |

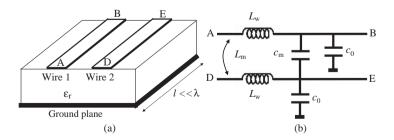

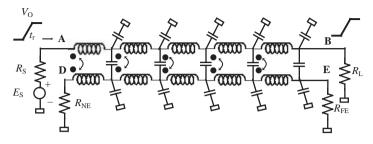

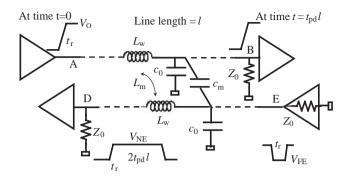

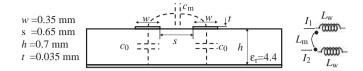

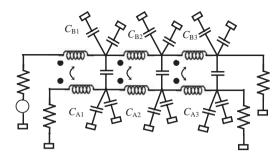

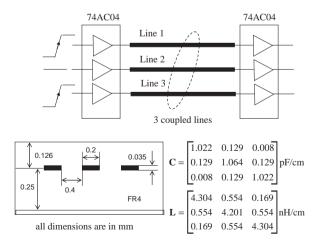

| 6.1 | Lumped-Circuit Model of Coupled Lines                                        | 126 |

|     | 6.1.1 Equivalent Circuit of Two Coupled Lines with a Reference Ground        | 126 |

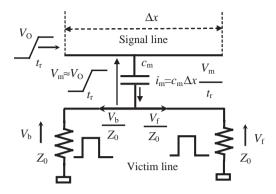

|     | 6.1.2 Capacitive Coupling                                                    | 127 |

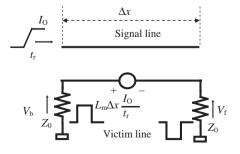

|     | 6.1.3 Inductive Coupling                                                     | 129 |

|     | 6.1.4 Total Coupling                                                         | 130 |

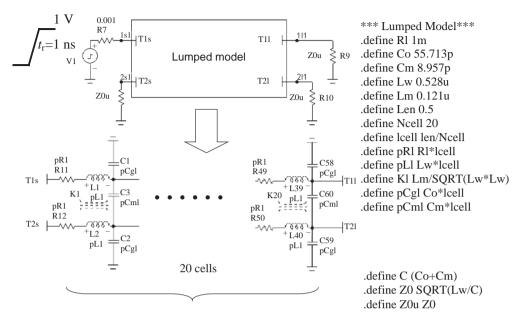

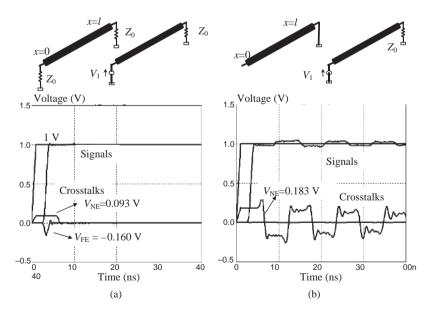

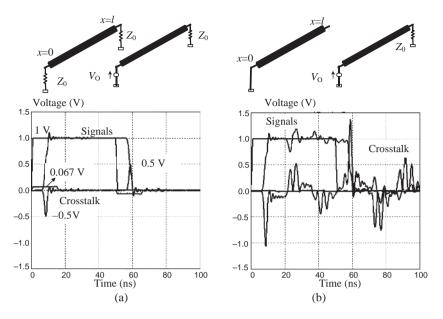

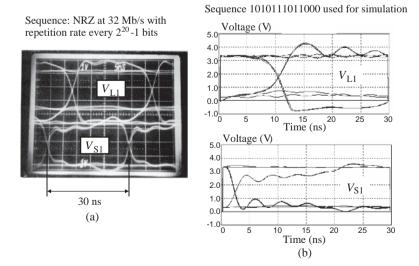

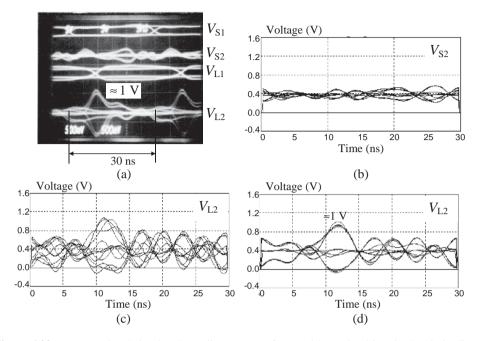

|     | 6.1.5 Simulations of Two Coupled Lines                                       | 130 |

| 6.2 | Common and Differential Modes                                                | 133 |

|     | 6.2.1 Definition of Even and Odd Modes                                       | 134 |

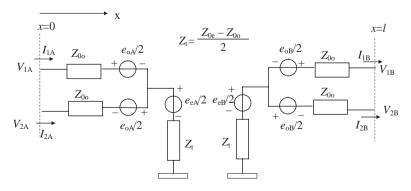

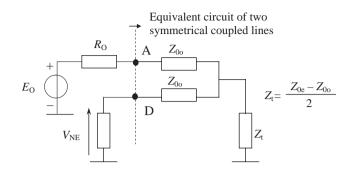

|     | 6.2.2 Equivalent Circuit Based on Even and Odd Modes                         | 136 |

|     | 6.2.3 Equivalent Circuit for the Differential Transmission Mode               | 137               |

|-----|-------------------------------------------------------------------------------|-------------------|

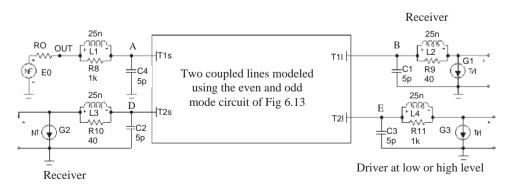

|     | 6.2.4 Simulations of Point-to-Point and Chain Structure by Even and Odd Modes | 137               |

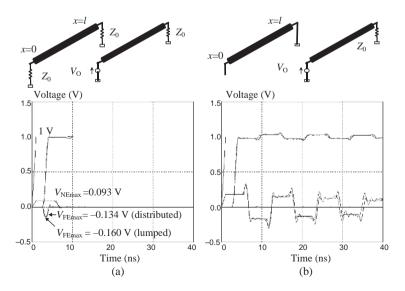

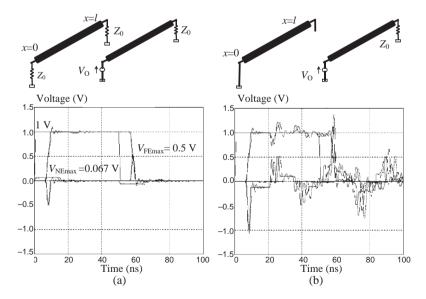

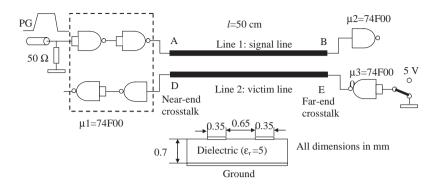

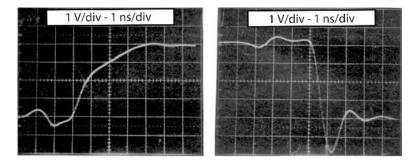

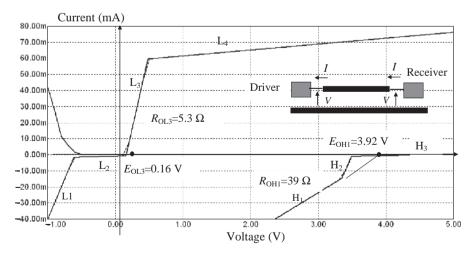

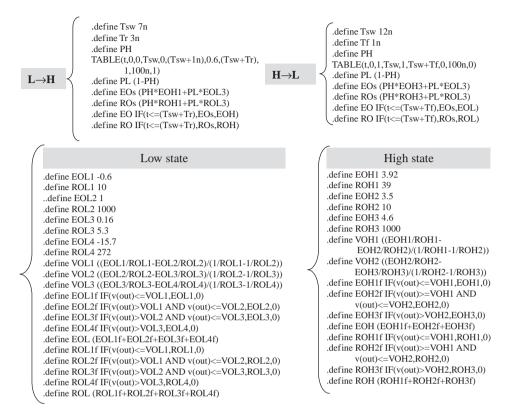

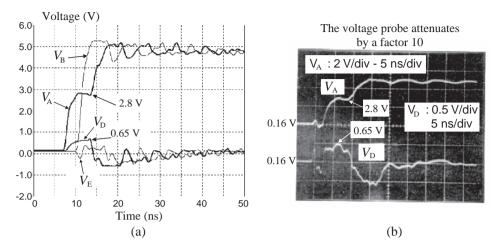

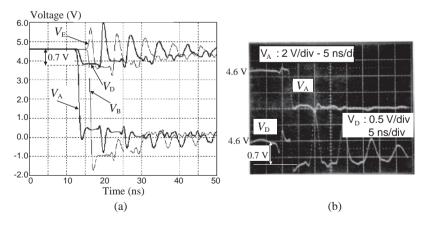

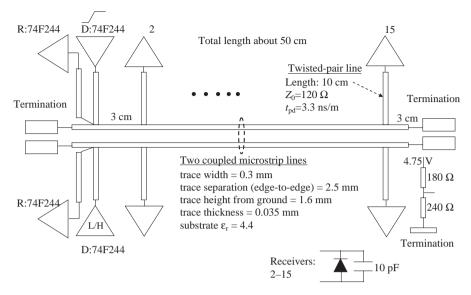

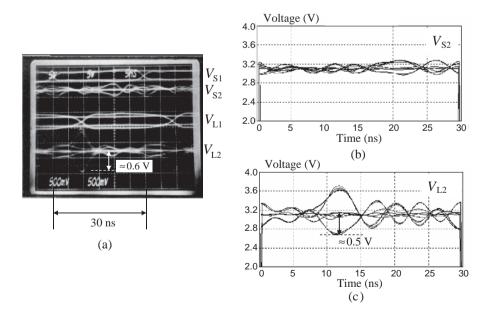

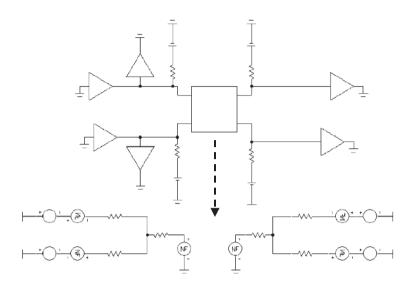

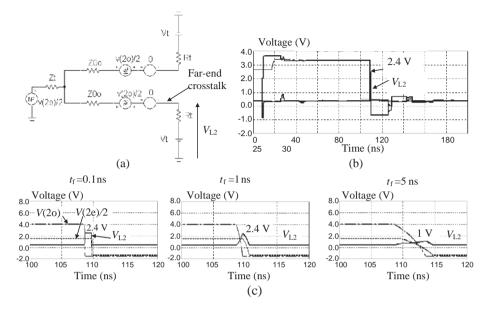

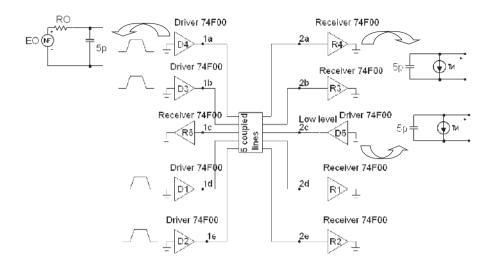

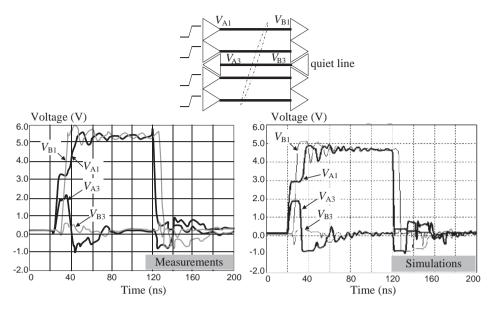

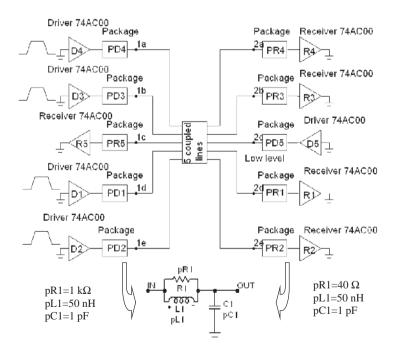

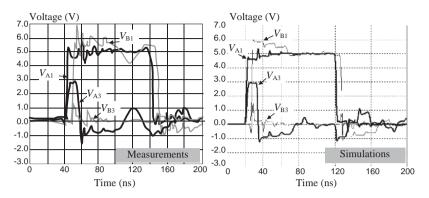

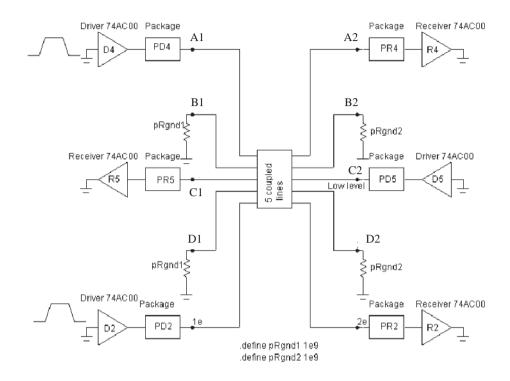

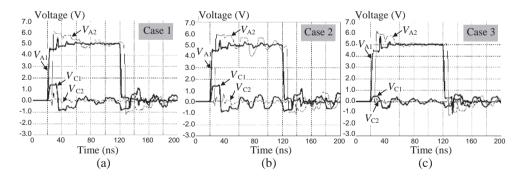

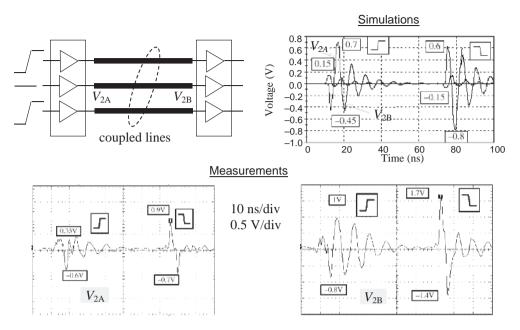

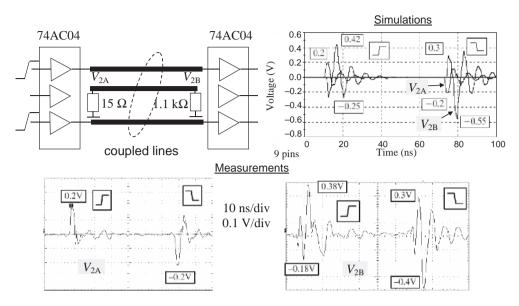

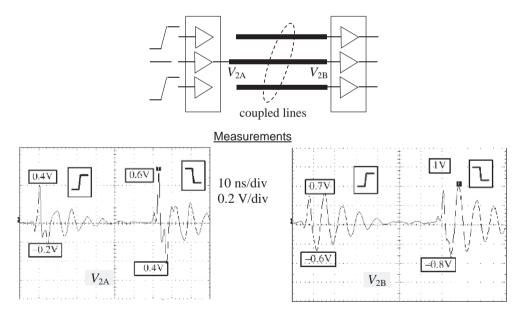

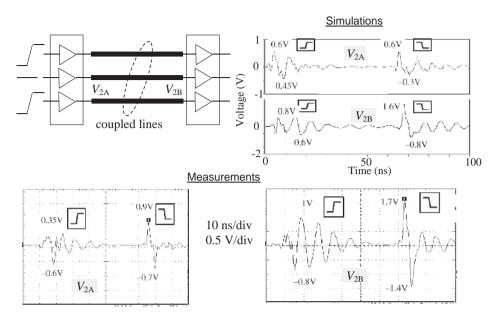

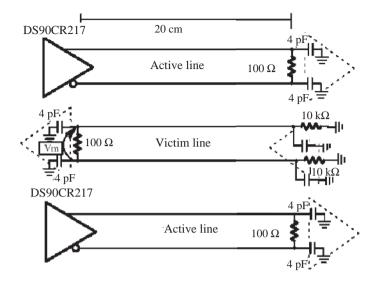

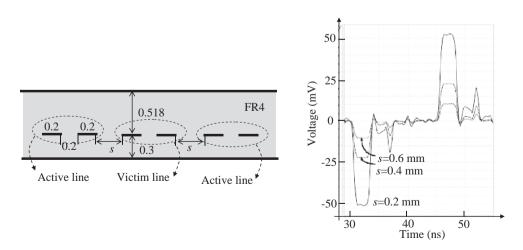

| 6.3 | Models for Digital Devices: Simulation and Measurements                       | 140               |

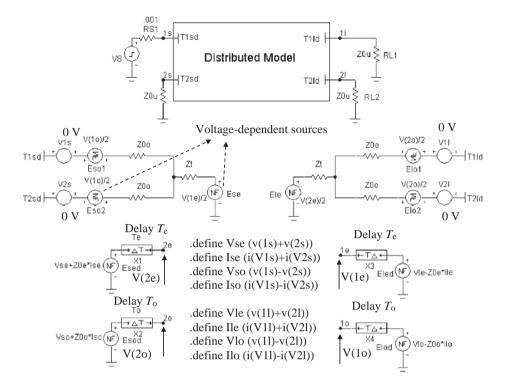

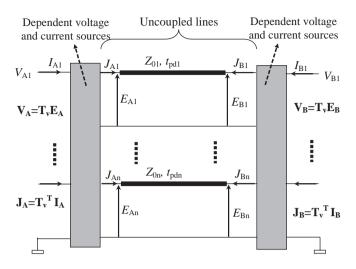

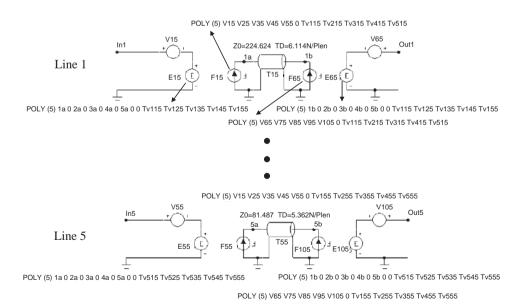

| 6.4 | General Distributed Model for Lossless Multiconductor Transmission Lines      | 150               |

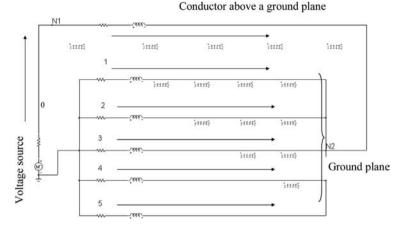

|     | 6.4.1 Equivalent Circuit of n Coupled Lossless Lines                          | 151               |

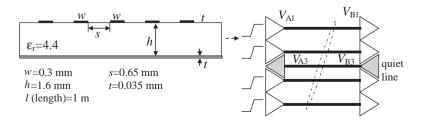

|     | 6.4.2 Measurements and Simulations of Five Coupled Lines with TTL             |                   |

|     | and CMOS Devices                                                              | 152               |

| 6.5 | Techniques to Reduce Crosstalk                                                | 157               |

|     | 6.5.1 Fixes to Reduce Crosstalk                                               | 157               |

|     | 6.5.2 Simulations of Coupled Lines with Grounded Traces used as               |                   |

|     | a Shield                                                                      | 158               |

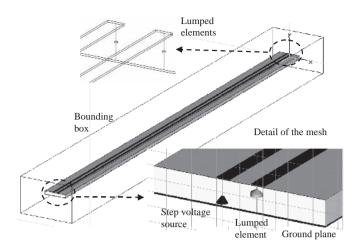

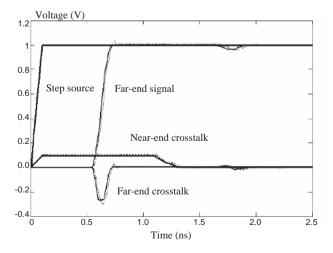

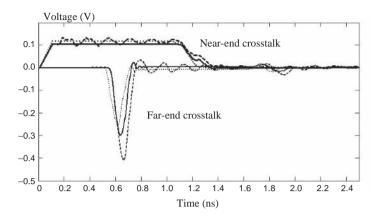

|     | 6.5.3 Full-Wave Numerical Simulations of Two Coupled Lines                    | 158               |

|     | References                                                                    | 161               |

| -   | Learn Thomasian Lines                                                         | 1(2               |

| 7   | Lossy Transmission Lines                                                      | <b>163</b><br>164 |

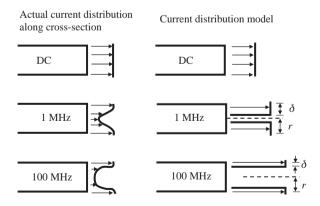

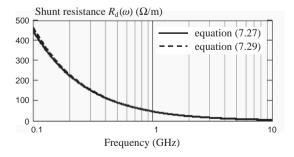

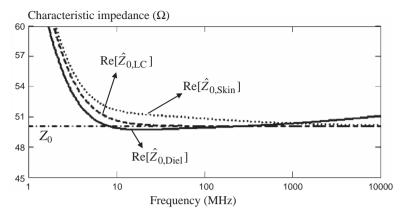

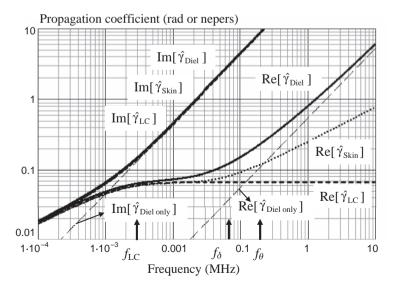

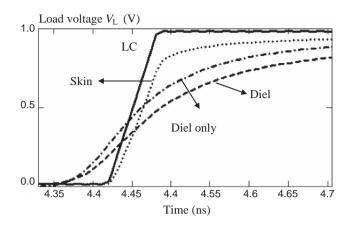

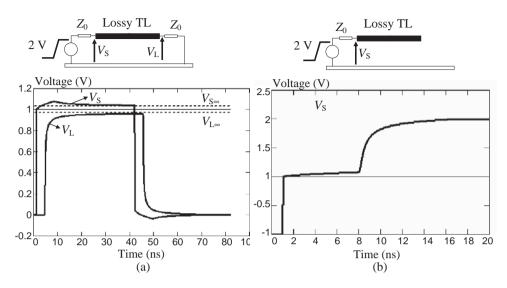

| /.1 | Lossy Line Fundamental Parameters                                             | 164               |

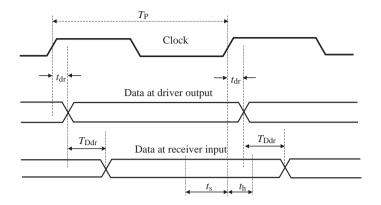

|     | 7.1.1 Reflection Mechanism in a Lossy Line                                    |                   |

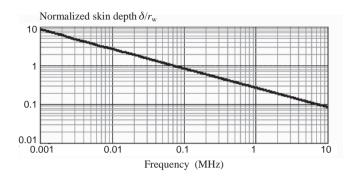

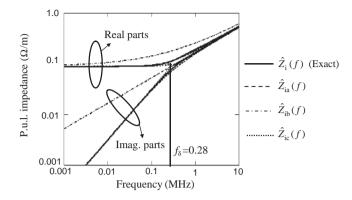

|     | 7.1.2 Skin Effect                                                             | 167               |

|     | 7.1.3 Proximity Effect                                                        | 171               |

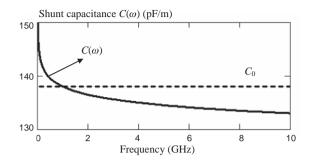

|     | 7.1.4 Lossy Dielectric Effect                                                 | 173               |

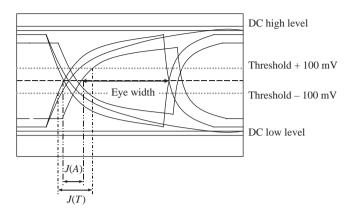

| 7 2 | 7.1.5 Data Transmission with Lossy Lines                                      | 175               |

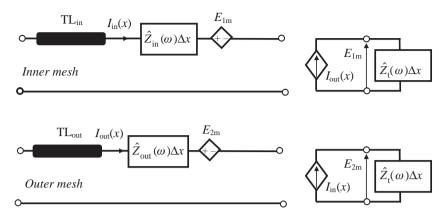

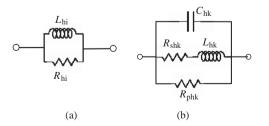

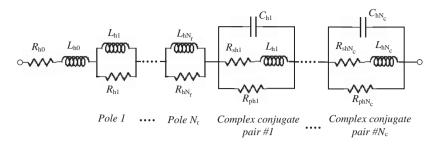

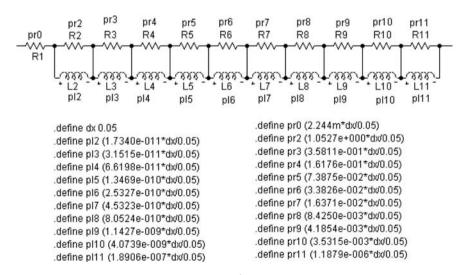

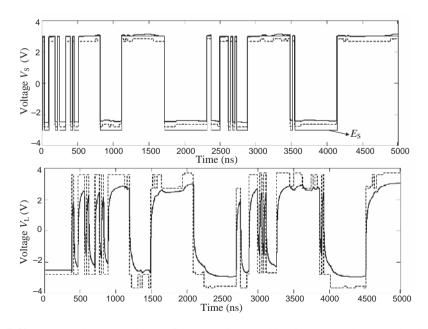

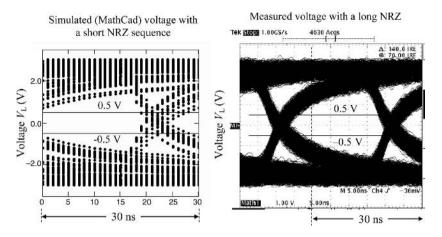

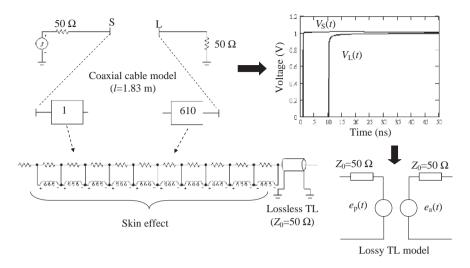

| 1.2 | Modeling Lossy Lines in the Time Domain by the Segmentation Approach          | 102               |

|     | and Vector Fitting Technique                                                  | 183               |

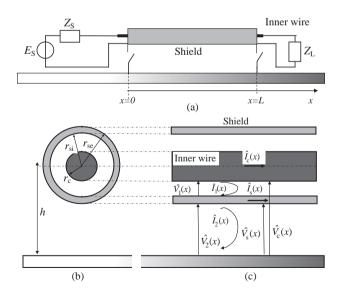

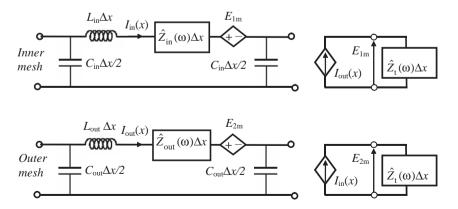

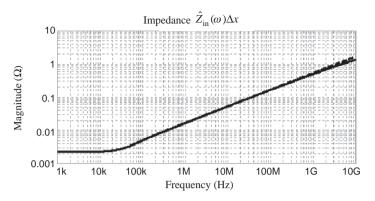

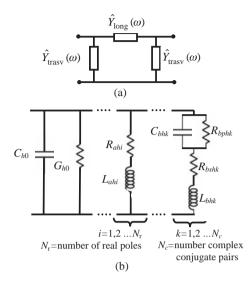

|     | 7.2.1 Circuit Extraction of Coaxial Cables                                    | 184               |

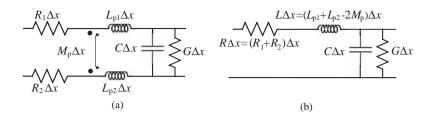

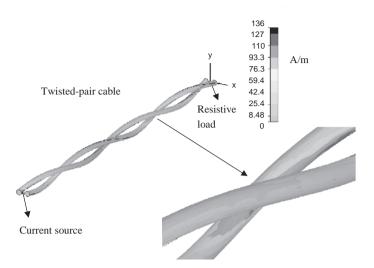

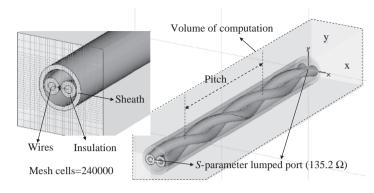

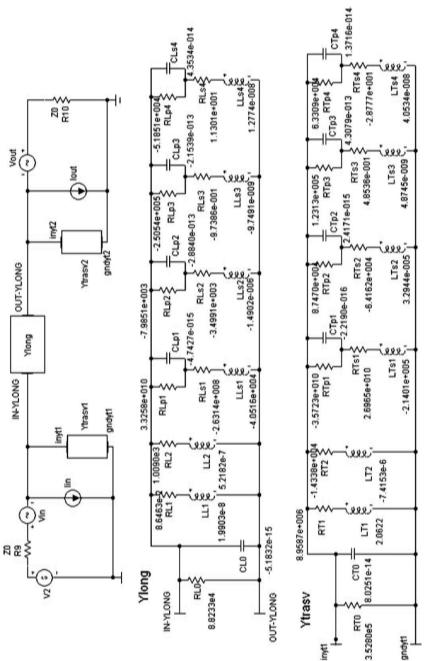

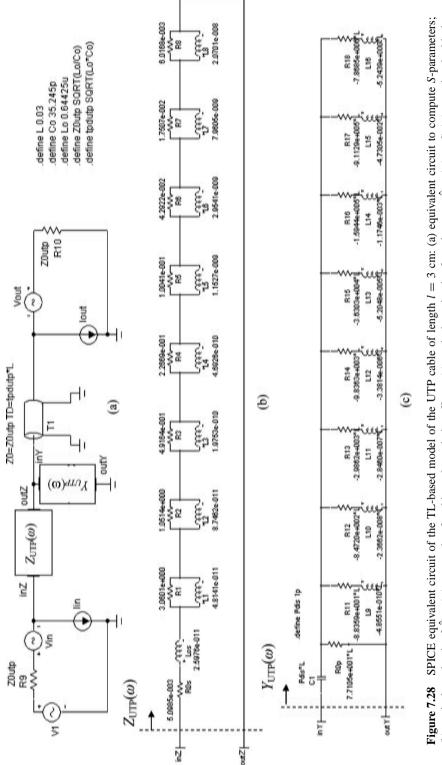

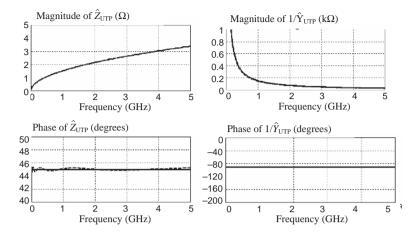

| 72  | 7.2.2 Circuit Extraction of Twisted-Pair Cables                               | 195               |

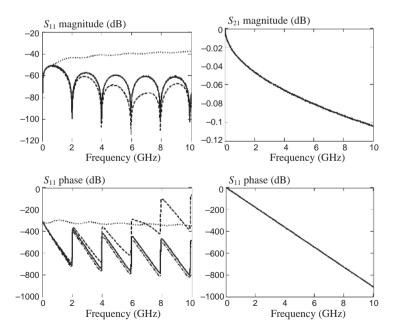

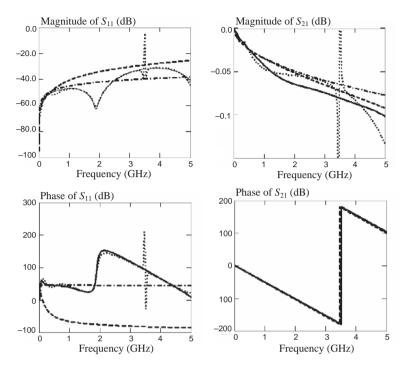

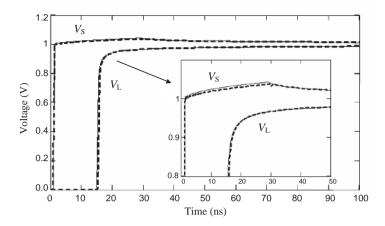

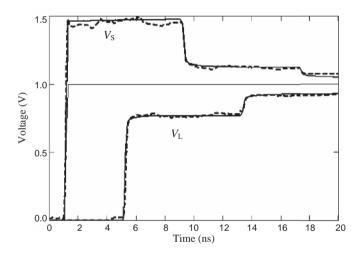

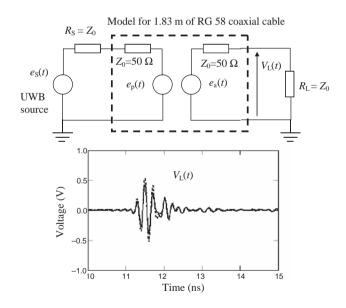

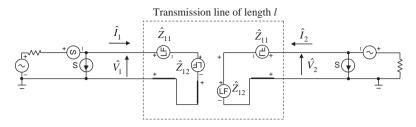

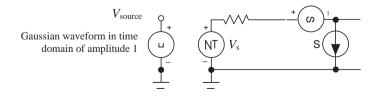

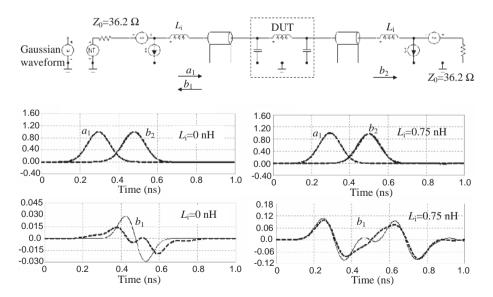

| 1.5 | Modeling Lossy Lines in the Time Domain by the Scattering Parameters          | 207               |

| 74  | Technique                                                                     | 207<br>215        |

| 7.4 | Conclusions                                                                   |                   |

|     | References                                                                    | 216               |

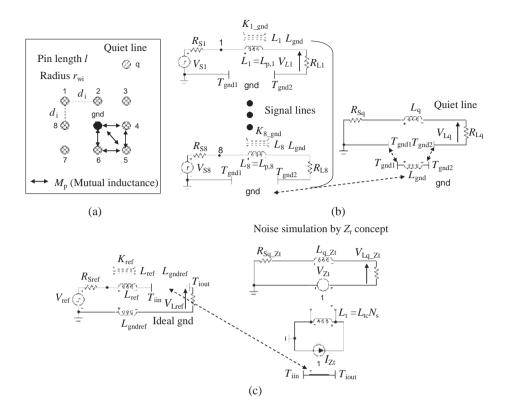

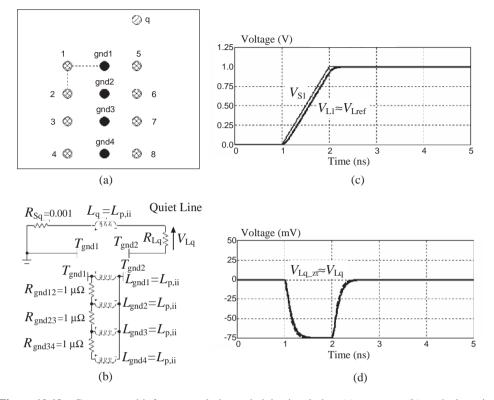

| 8   | Delta I-Noise                                                                 | 219               |

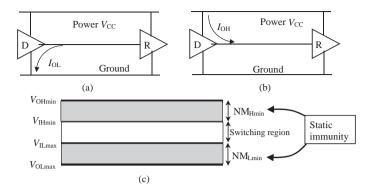

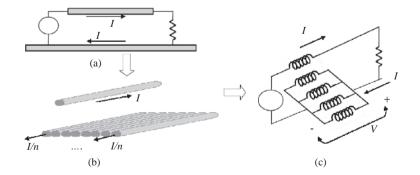

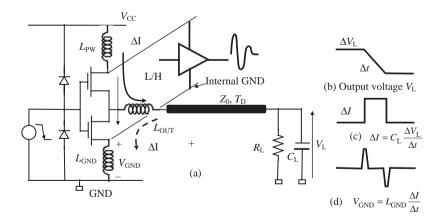

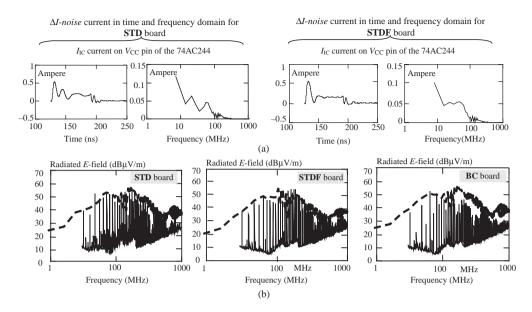

| 8.1 | Switching Noise                                                               | 220               |

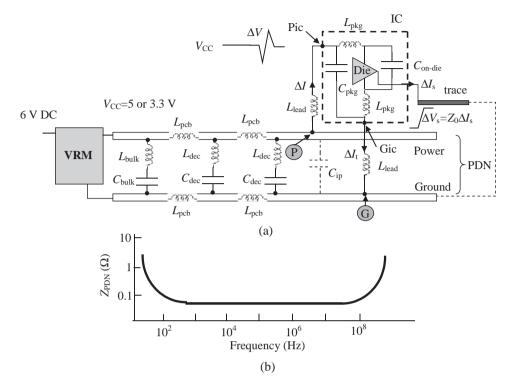

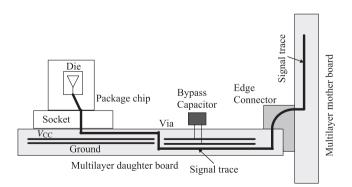

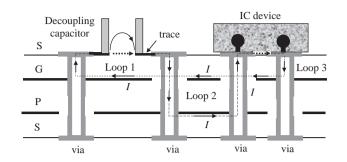

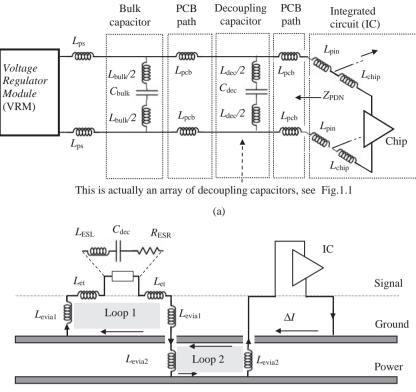

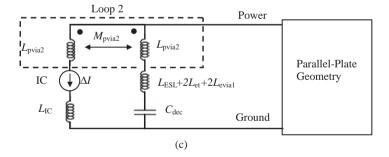

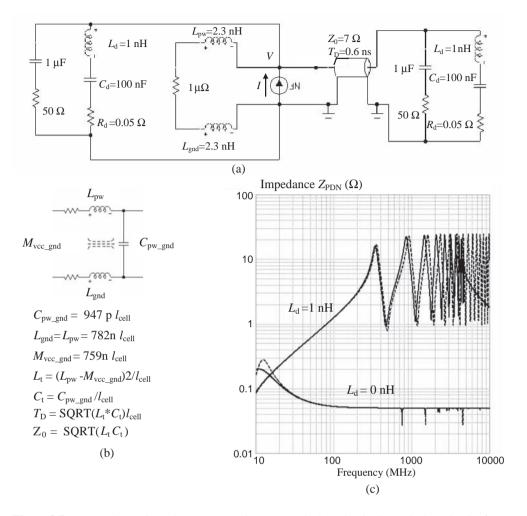

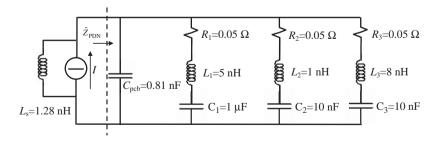

|     | 8.1.1 Power Distribution Network                                              | 220               |

|     | 8.1.2 Switching Current Path                                                  | 225               |

|     | 8.1.3 Design Rules                                                            | 236               |

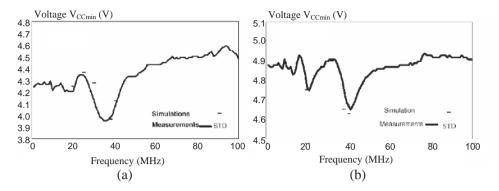

| 8.2 | Filtering Power Distribution                                                  | 237               |

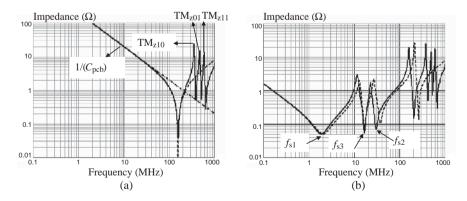

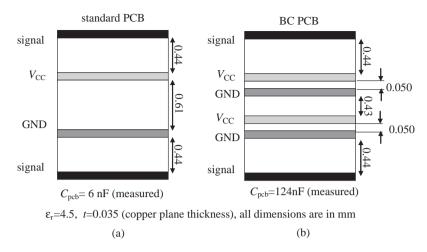

|     | 8.2.1 Filtering Multilayer PCBs                                               | 237               |

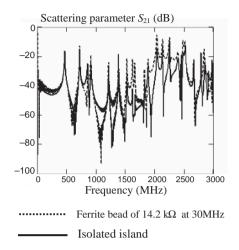

|     | 8.2.2 Measurement of Power Distribution Network Impedance                     | 244               |

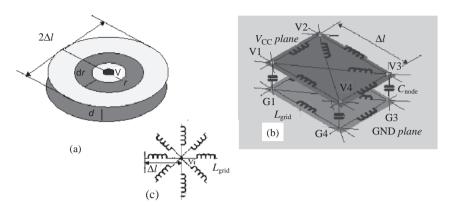

|     | 8.2.3 PCB Circuit Model Based on Radial Transmission Line Theory              | 245               |

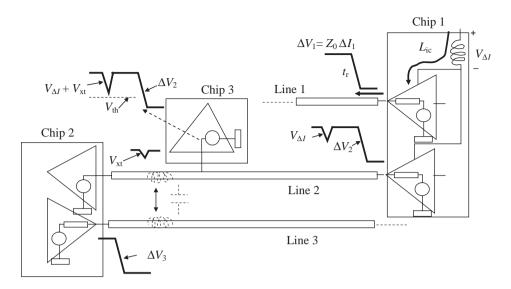

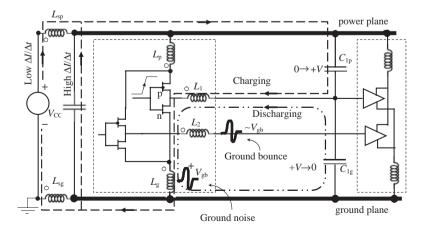

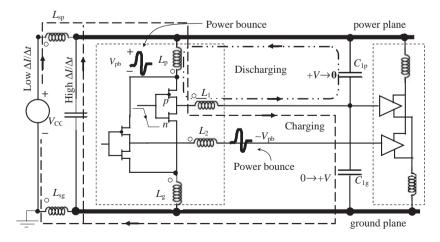

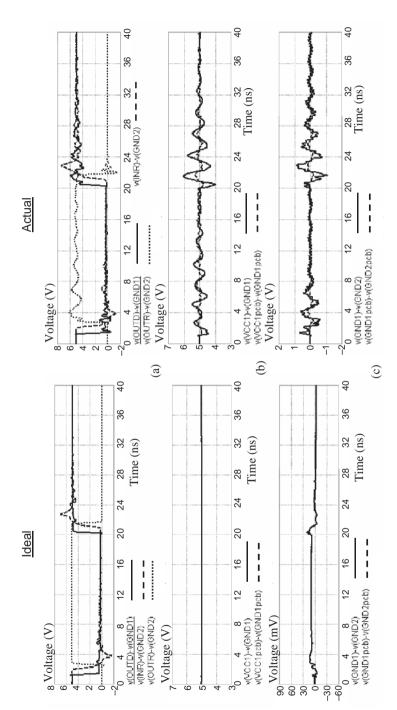

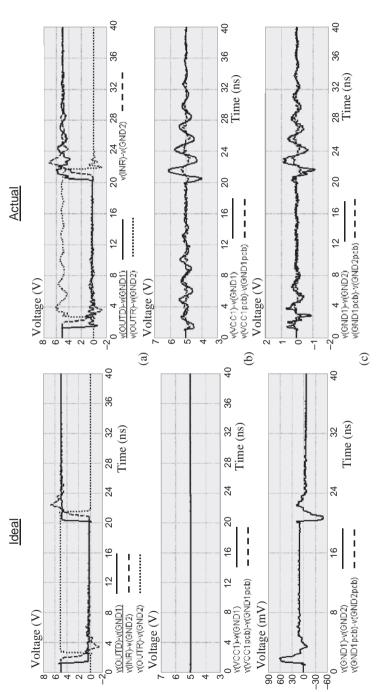

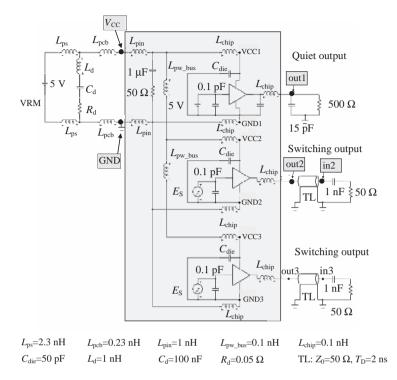

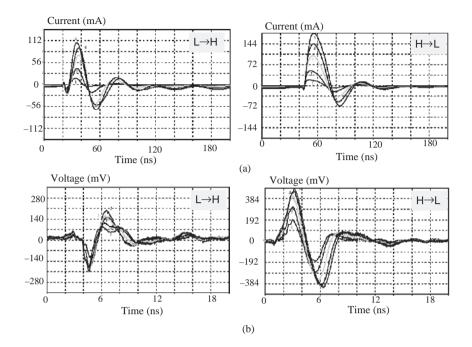

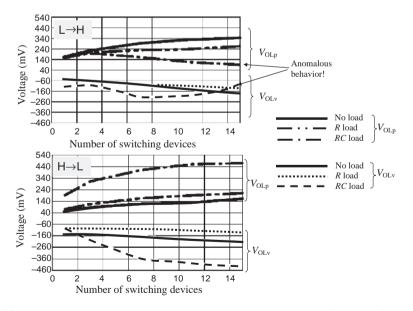

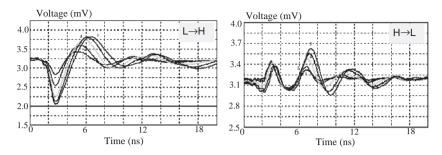

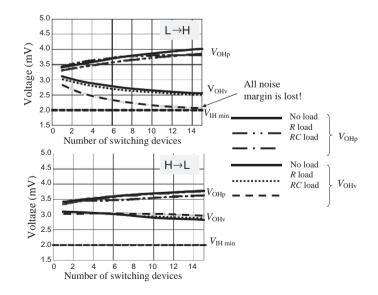

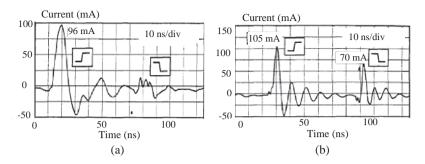

| 8.3 | Ground Bounce                                                                 | 254               |

|     | 8.3.1 Ground Bounce Mechanism                                                 | 255               |

|     | 8.3.2 Circuit Simulations to Understand the Ground Bounce Mechanism           | 256               |

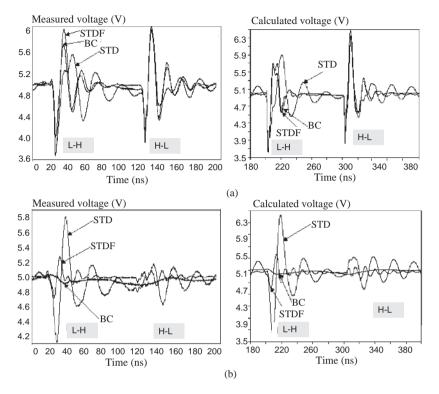

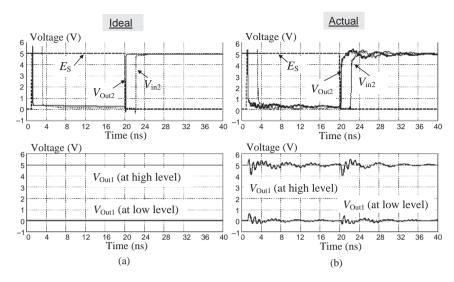

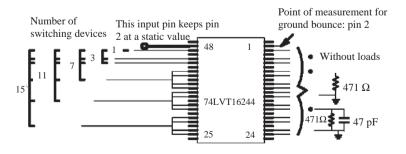

|     | 8.3.3 Measurements of an LVT Benchmark                                        | 257               |

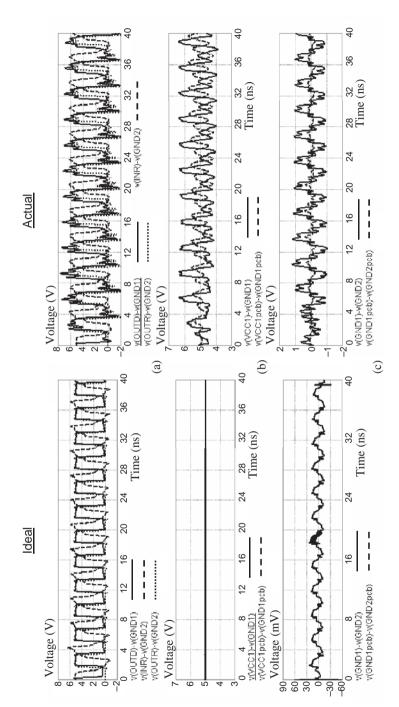

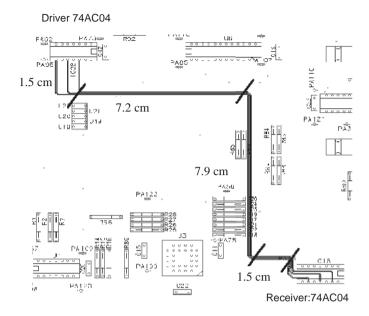

| 8.4 | Crosstalk and Switching Noise                                                 | 262               |

|     | 8.4.1 Measurements and Simulations of the SQ-Test Board with Three            |                   |

|     | Coupled Lines and 74AC04 Devices                                              | 262               |

|     | References                                                                    | 266               |

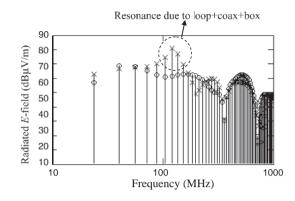

| 9   | PCB Radiated Emission                                                  | 269 |

|-----|------------------------------------------------------------------------|-----|

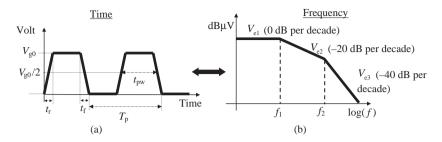

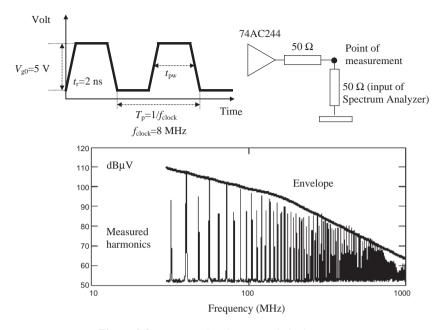

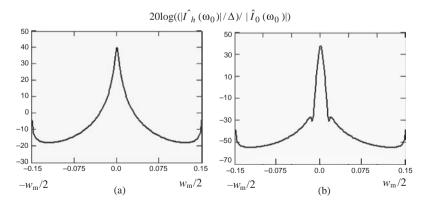

| 9.1 | Frequency Characterization of a Digital Signal                         | 270 |

|     | 9.1.1 Spectrum of a Trapezoidal Waveform                               | 270 |

|     | 9.1.2 Spectrum of Typical Noises                                       | 274 |

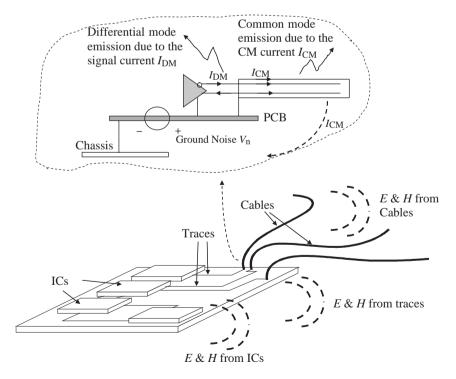

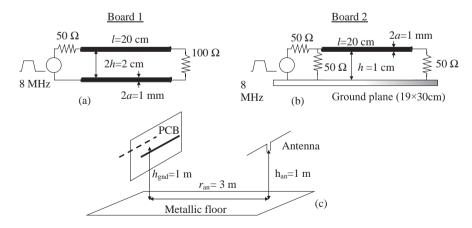

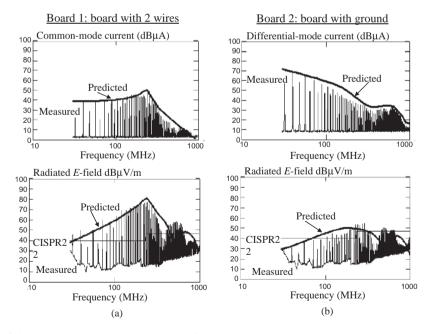

| 9.2 | The Radiated Emission Problem                                          | 276 |

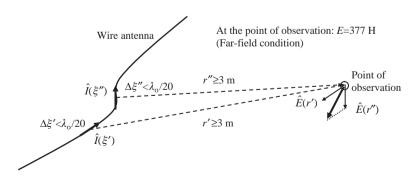

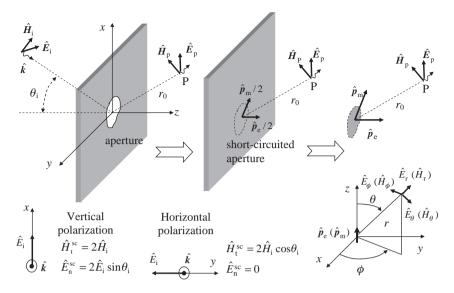

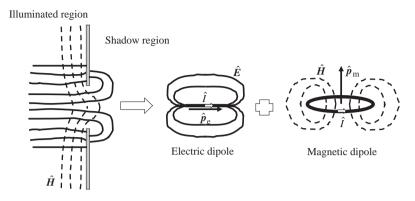

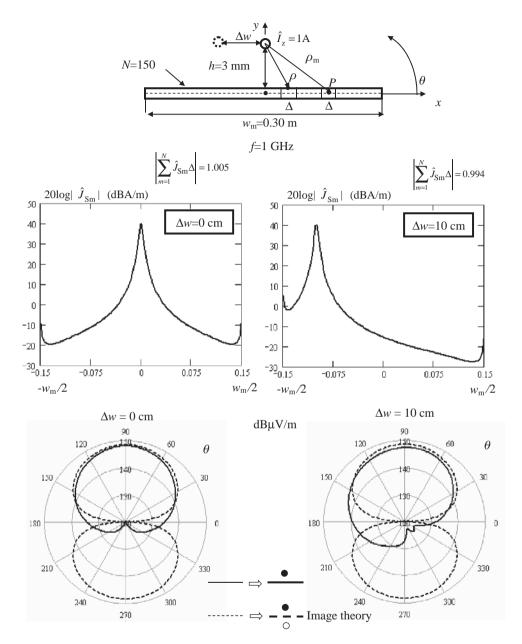

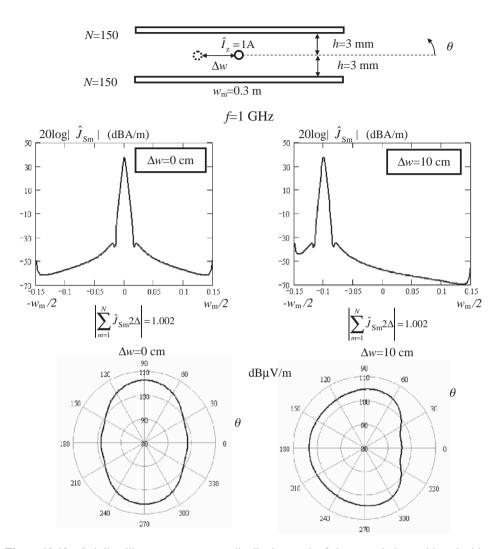

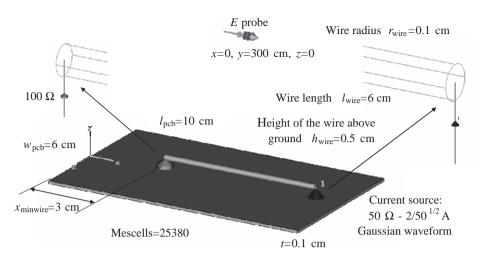

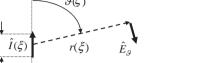

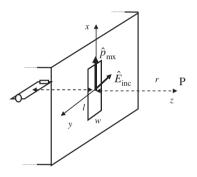

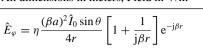

|     | 9.2.1 Radiation from a Wire Antenna                                    | 278 |

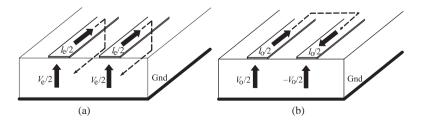

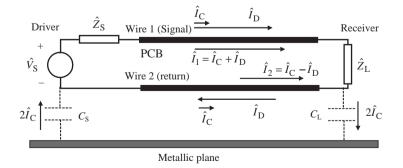

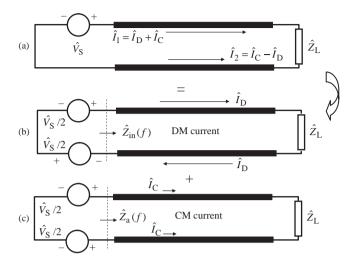

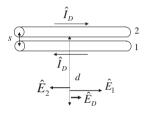

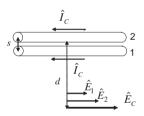

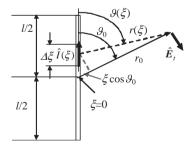

|     | 9.2.2 Common- and Differential-Mode Currents and Radiations            | 279 |

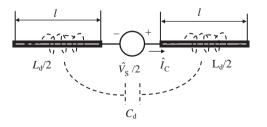

|     | 9.2.3 Emission Due to Line Asymmetrical Feed                           | 281 |

|     | 9.2.4 Differential-Mode Current and Radiated Emission of a             |     |

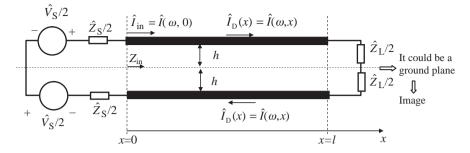

|     | Transmission Line                                                      | 282 |

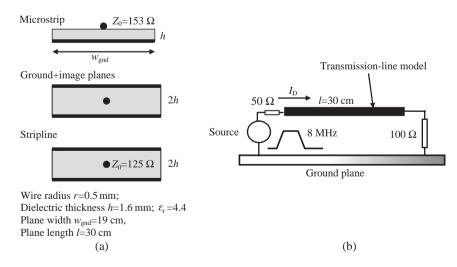

|     | 9.2.5 Common-Mode Current and Radiated Emission of a Transmission Line | 284 |

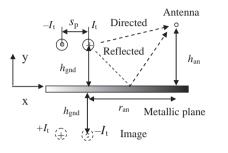

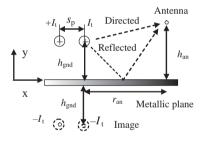

|     | 9.2.6 Image Plane                                                      | 287 |

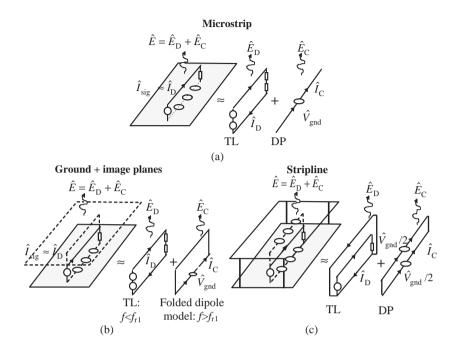

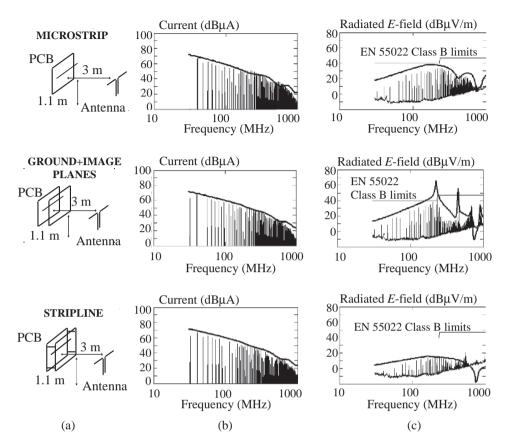

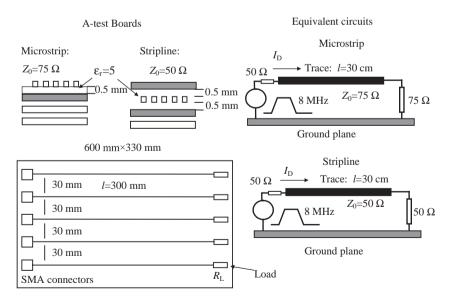

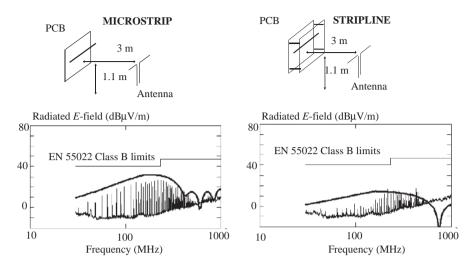

| 9.  | 3 Emission from Traces                                                 | 289 |

|     | 9.3.1 Antenna Models for Calculating the Radiation of Microstrip and   |     |

|     | Stripline Structures                                                   | 289 |

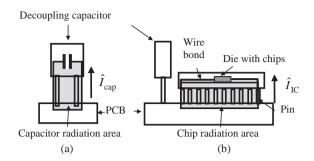

| 9.4 | 4 Emission from ICs                                                    | 295 |

|     | 9.4.1 Radiated Emission Mechanism from Components in a PCB             | 296 |

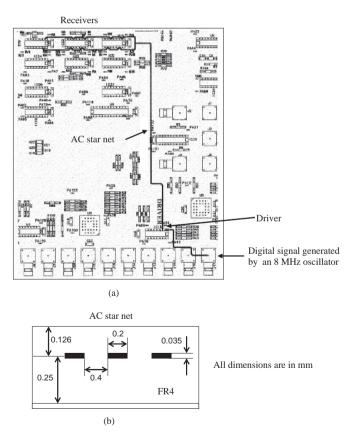

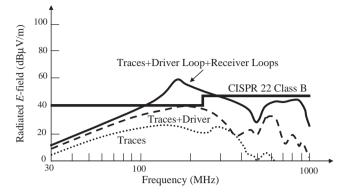

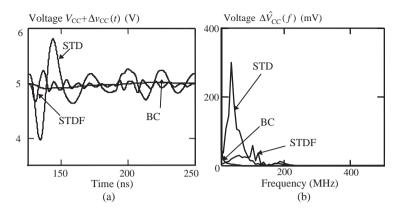

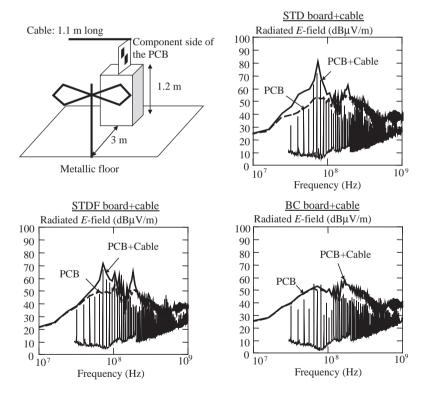

| 9.  | 5 Emission from a Real PCB                                             | 298 |

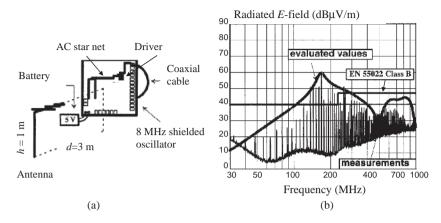

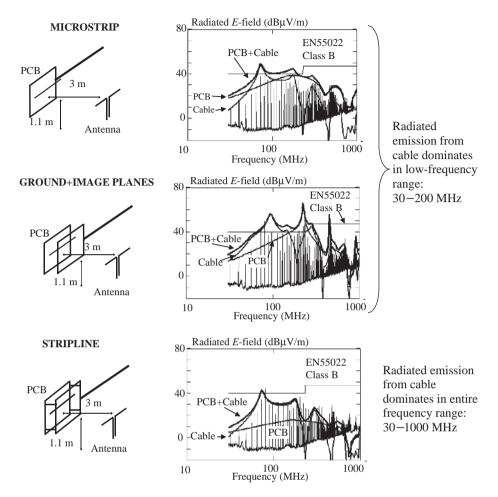

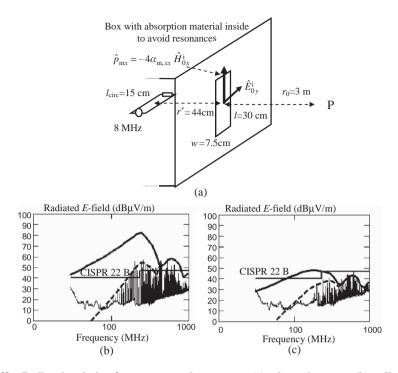

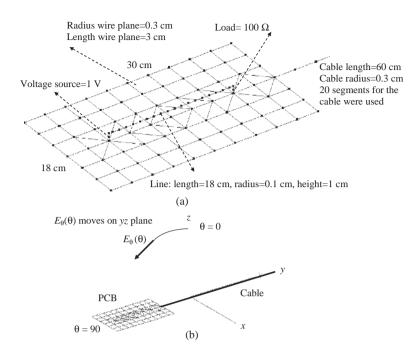

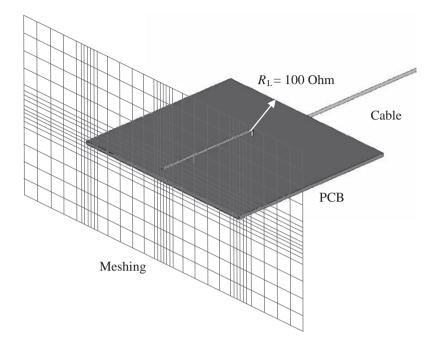

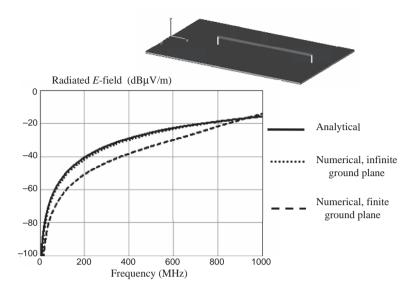

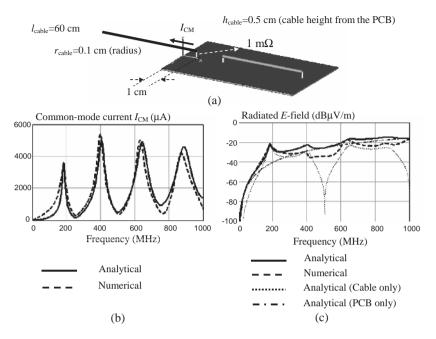

| 9.  | 6 Emission from a PCB with an Attached Cable                           | 303 |

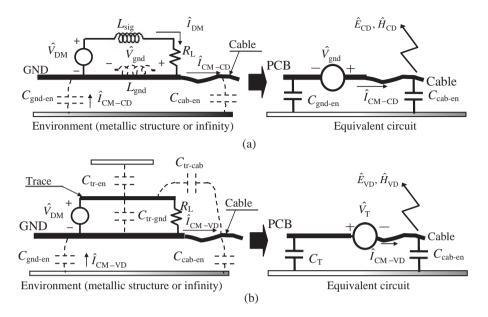

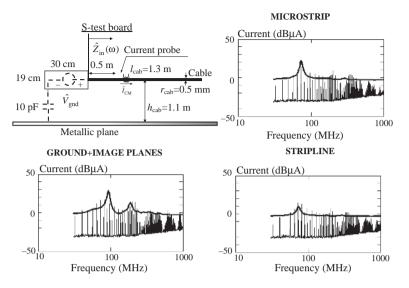

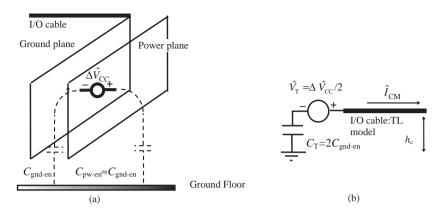

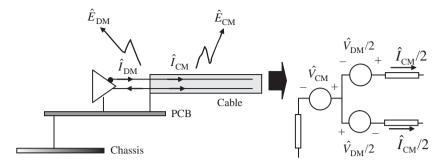

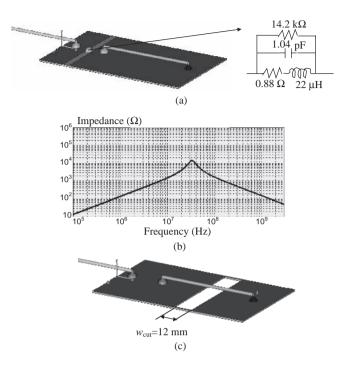

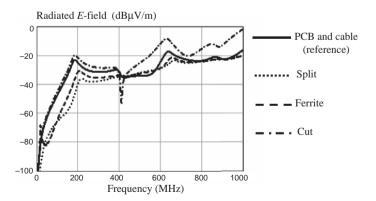

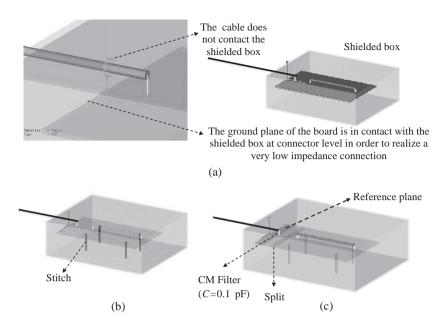

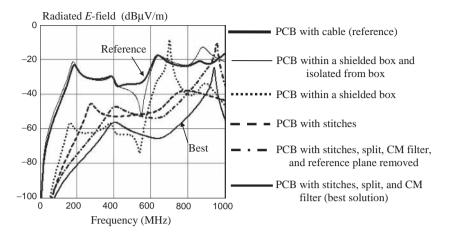

|     | 9.6.1 Sources of Emission                                              | 303 |

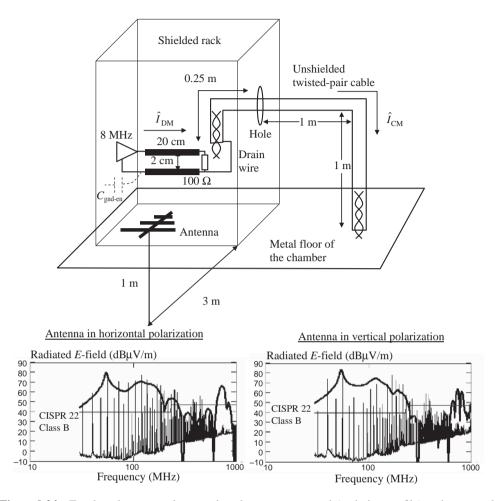

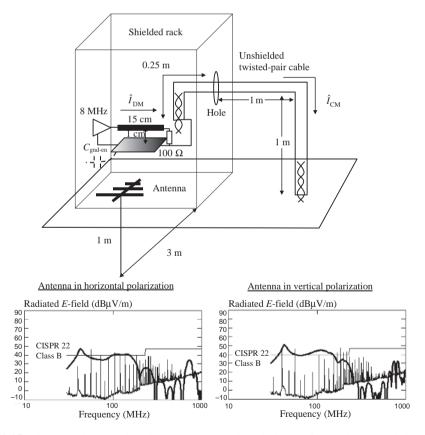

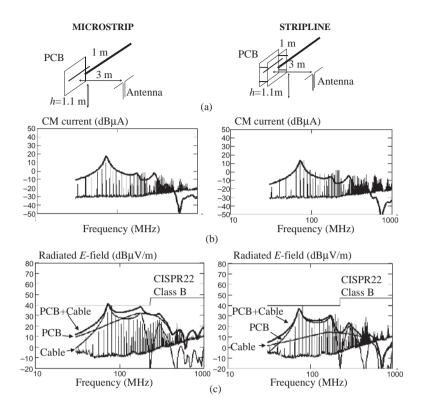

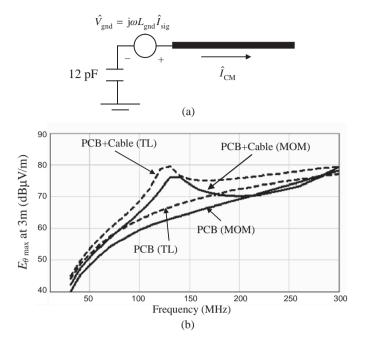

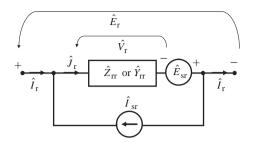

|     | 9.6.2 Current- and Voltage-Driven Mechanisms with a Trace in a PCB     | 303 |

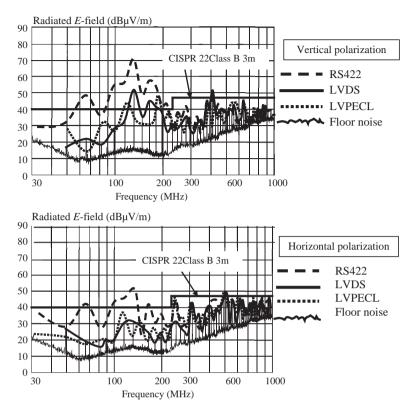

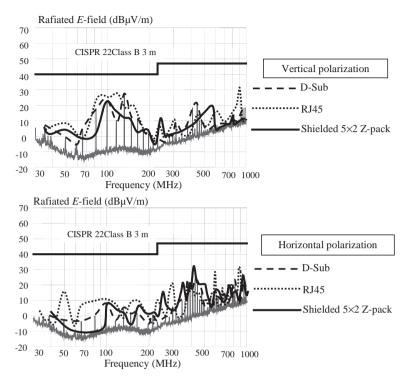

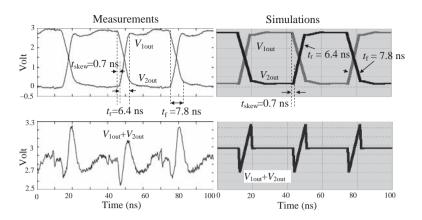

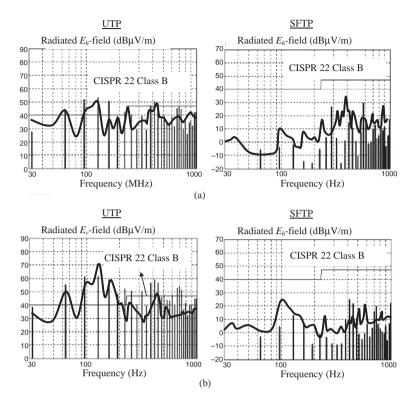

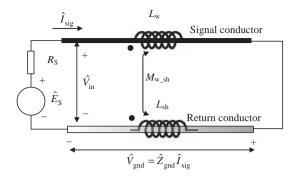

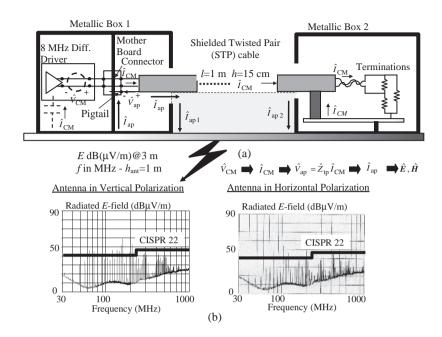

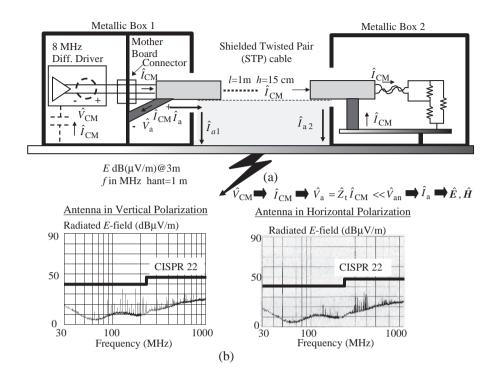

| 9.' | 7 Differential Drivers as Sources of Emission                          | 318 |

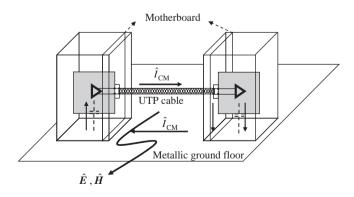

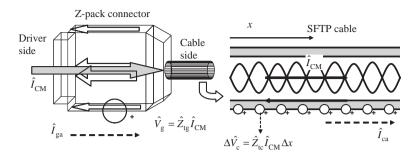

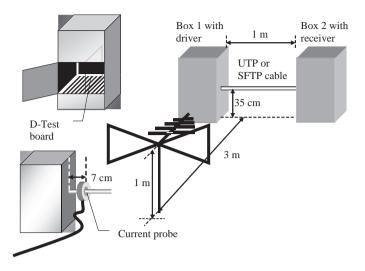

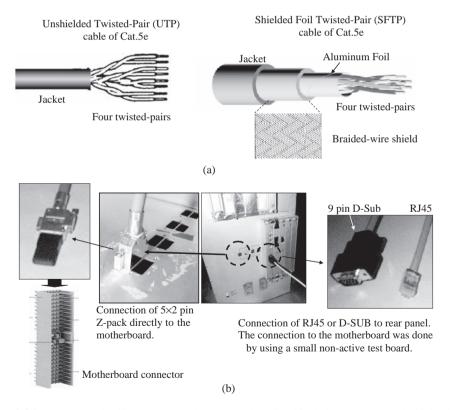

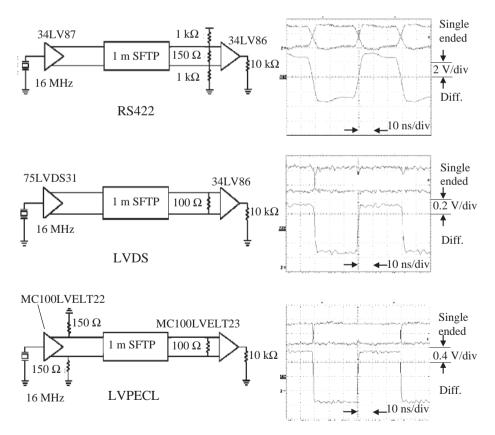

|     | 9.7.1 Common-Mode Current with Differential Drivers                    | 318 |

|     | 9.7.2 Radiated Field Mechanism of UTP and SFTP Cables                  | 319 |

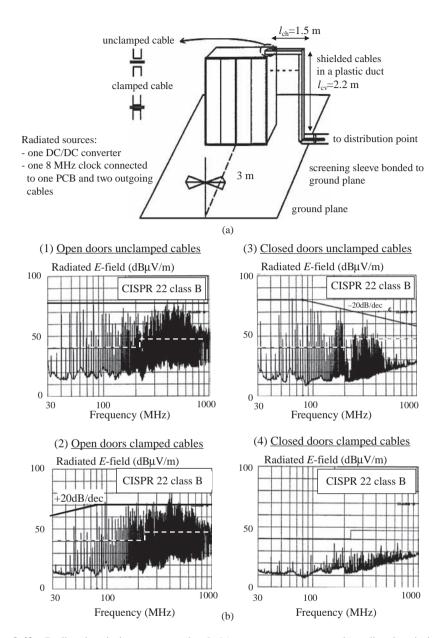

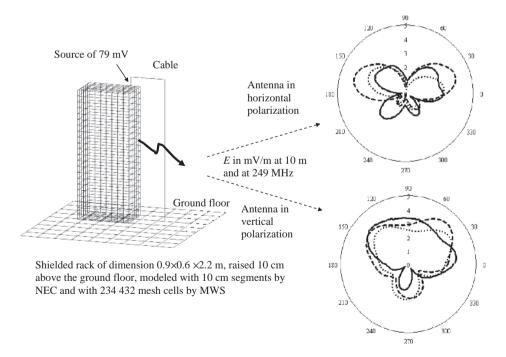

| 9.  | 8 Emission from a Complex System                                       | 327 |

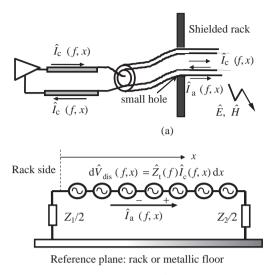

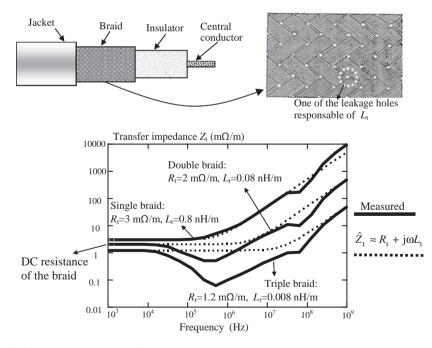

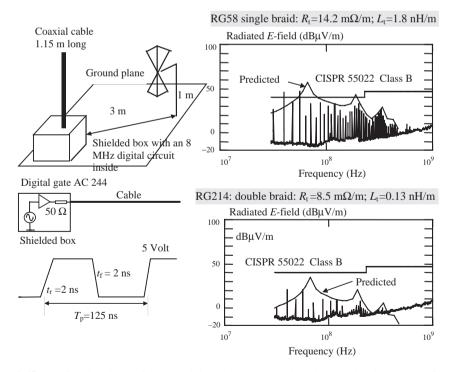

|     | 9.8.1 Emission Model of Coaxial Cables                                 | 330 |

|     | 9.8.2 Low-Frequency Model of an Aperture                               | 336 |

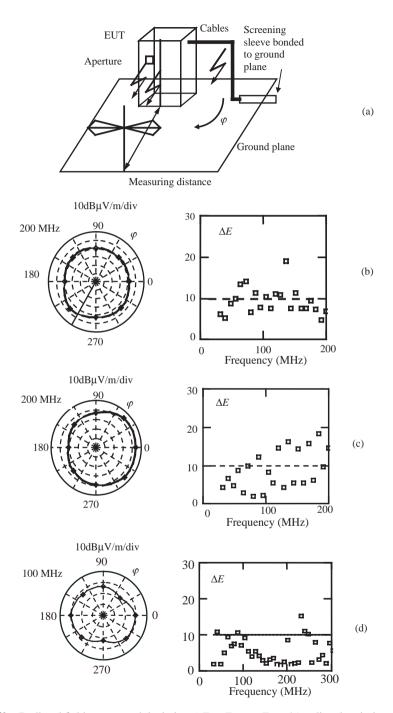

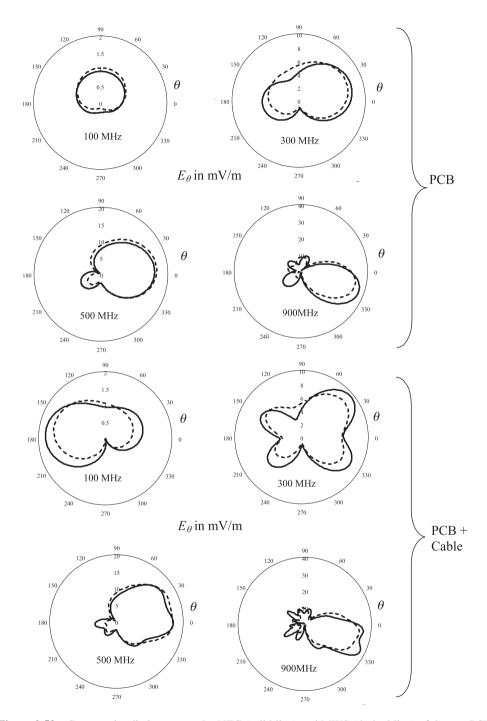

| 9.9 | 9 Radiation Diagrams                                                   | 341 |

| 9.1 | O Points to Remember and Design Rules for Radiated Emission            | 349 |

|     | References                                                             | 352 |

| 10  | Grounding in PCBs                                                      | 355 |

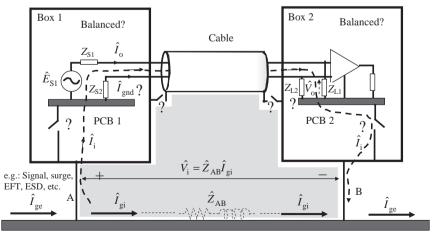

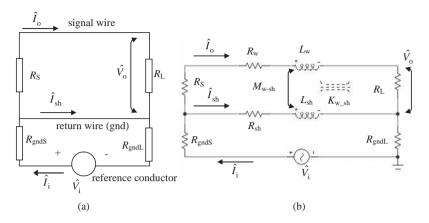

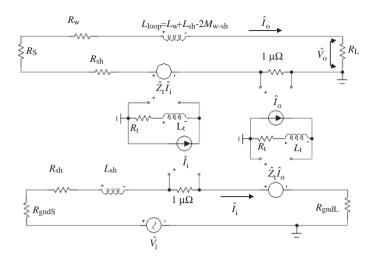

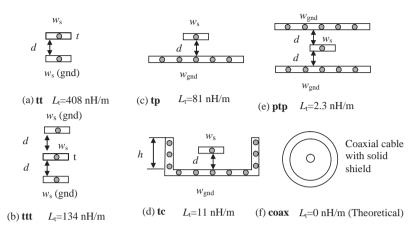

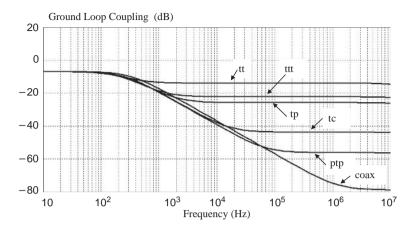

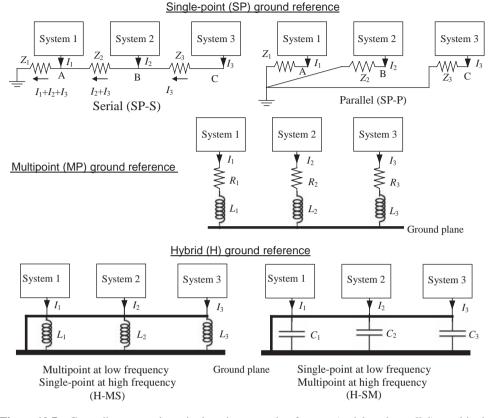

| 10. | 1 Common-Mode Coupling                                                 | 355 |

|     | 10.1.1 What is Ground?                                                 | 356 |

|     | 10.1.2 Ground Loop Coupling and Transfer Impedance                     | 356 |

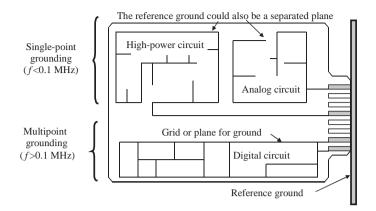

|     | 10.1.3 Grounding Strategy                                              | 363 |

| 10. | 2 Ground and Power Distribution in a Multilayer PCB                    | 365 |

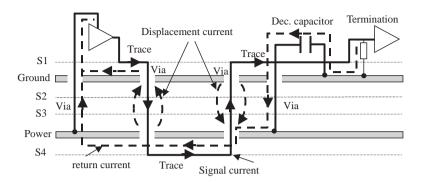

|     | 10.2.1 Return Path for the Signal                                      | 366 |

|     | 10.2.2 Power (PWR) and Ground (GND) Layer Planning and Topology        | 370 |

|     | 10.2.3 Trace Changing Reference Plane                                  | 370 |

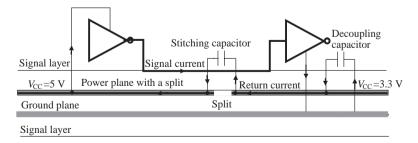

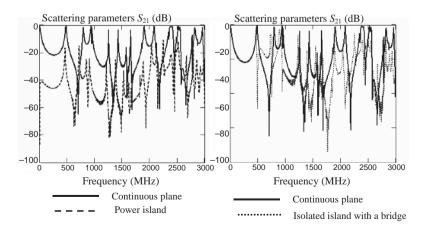

|     | 10.2.4 Split Power Plane                                               | 372 |

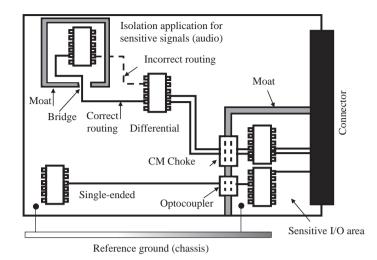

|     | 10.2.5 Moats/Barriers and Bridges                                      | 373 |

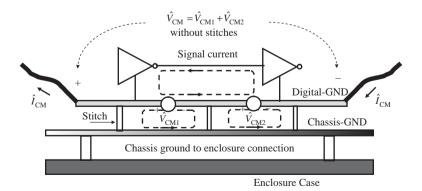

|     | 10.2.6 Stitches                                                        | 374 |

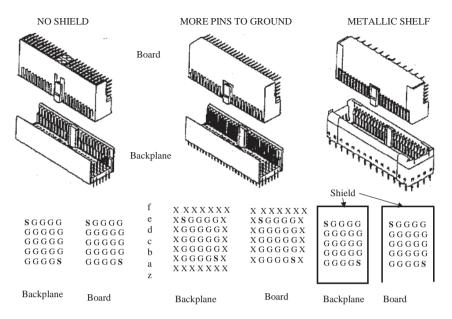

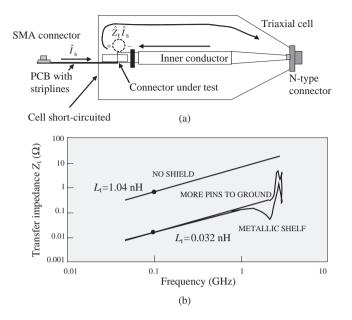

| 10. | 3 Grounding at PCB Connectors                                          | 375 |

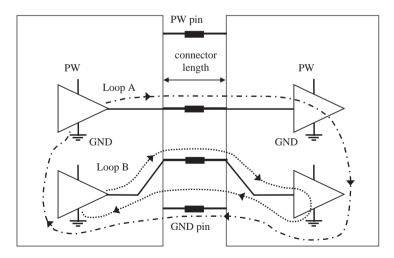

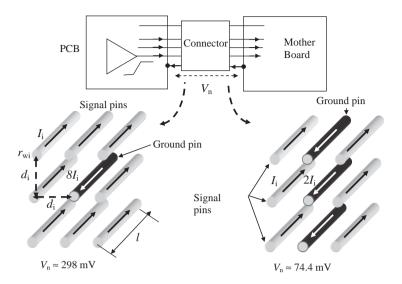

|     | 10.3.1 Ground Noise and Transfer Impedance                             | 375 |

|     | Totell Crowna House and Transfer Impedance                             | 010 |

|      | 10.3.2 Pin Assignment                                                      | 381 |

|------|----------------------------------------------------------------------------|-----|

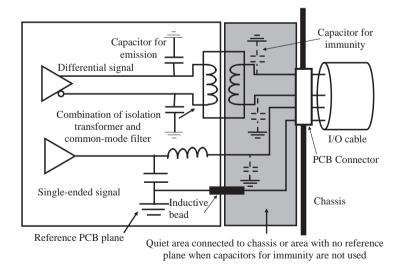

|      | 10.3.3 Grounding a PCB to a Chassis                                        | 384 |

|      | 10.3.4 Techniques to Limit Emission from Cables                            | 385 |

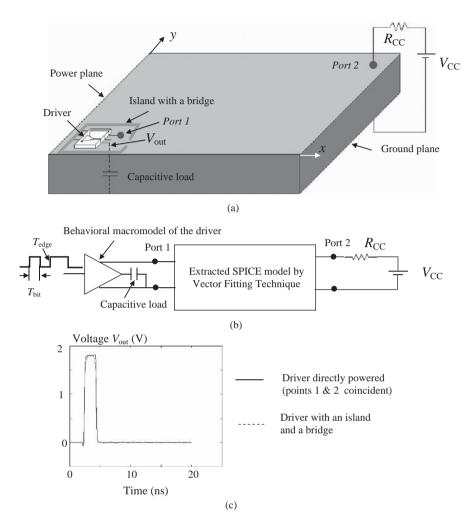

| 10.4 | Partitioning and Modeling                                                  | 393 |

|      | 10.4.1 Modeling the Power Distribution with a Driver for Simulations       | 400 |

| 10.5 | Points to Remember and Design Rules for Grounding in PCBs                  | 402 |

|      | References                                                                 | 406 |

| 11   | Measurement and Modeling                                                   | 409 |

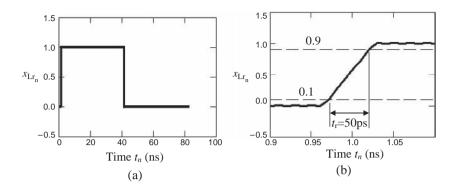

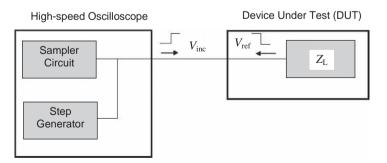

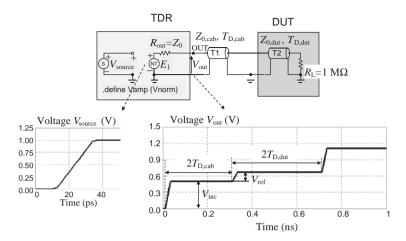

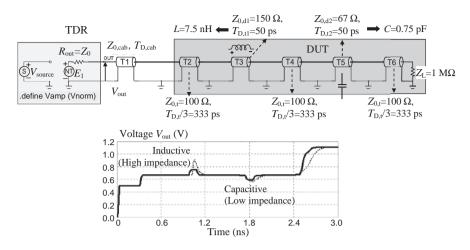

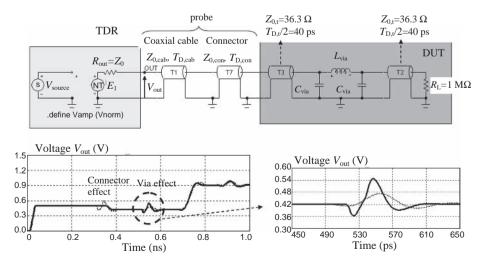

| 11.1 | Time-Domain Reflectometer (TDR)                                            | 410 |

|      | 11.1.1 TDR as a 'Closed-Loop Radar'                                        | 410 |

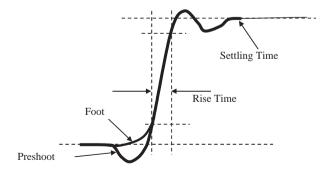

|      | 11.1.2 TDR Resolution and Aberrations                                      | 412 |

|      | 11.1.3 TDR and Lossy Lines                                                 | 415 |

|      | 11.1.4 Differential TDR                                                    | 416 |

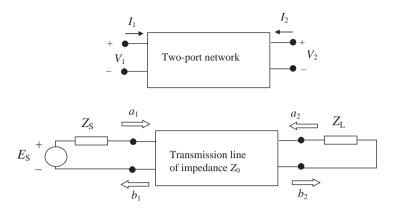

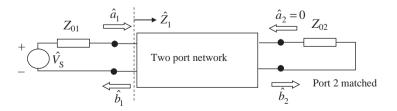

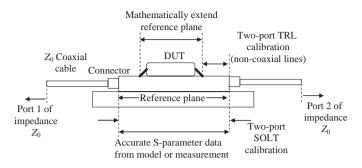

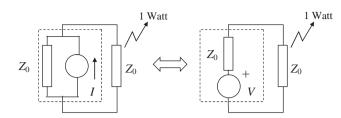

| 11.2 | Vector Network Analyzer (VNA)                                              | 417 |

|      | 11.2.1 Scattering Parameter Definition                                     | 417 |

|      | 11.2.2 VNA Calibration                                                     | 420 |

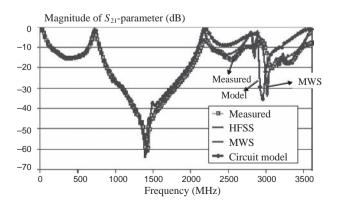

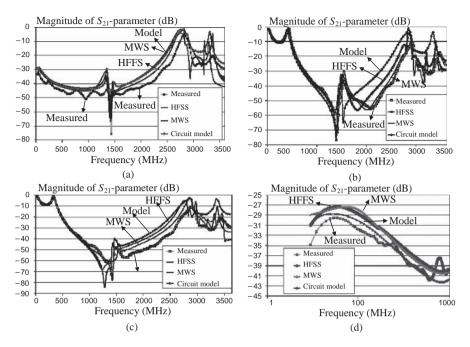

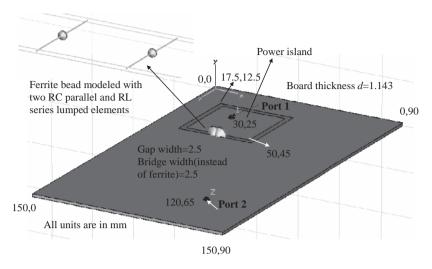

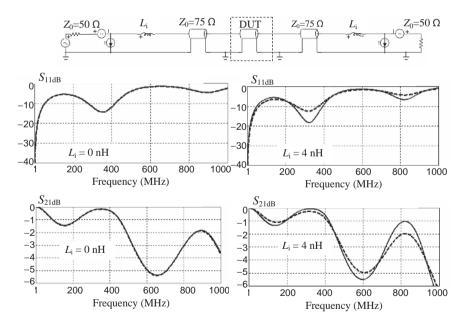

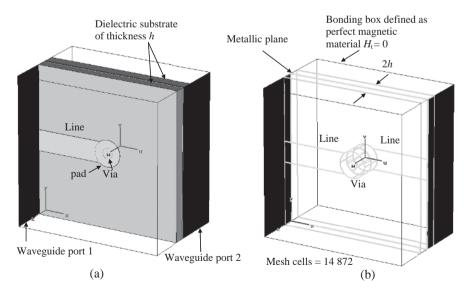

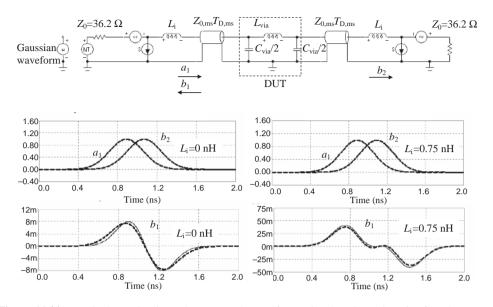

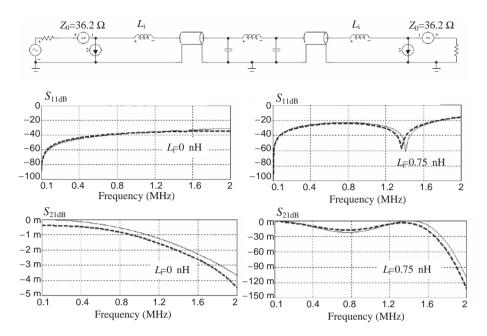

|      | 11.2.3 Extraction of Equivalent Circuits by S-Parameter Simulations        | 421 |

|      | 11.2.4 Conclusions Concerning VNA Measurements and Simulations             | 429 |

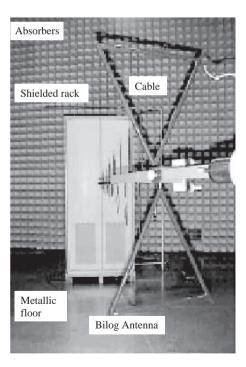

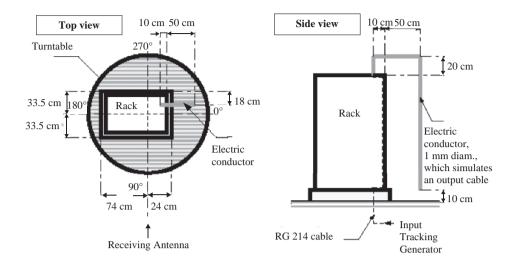

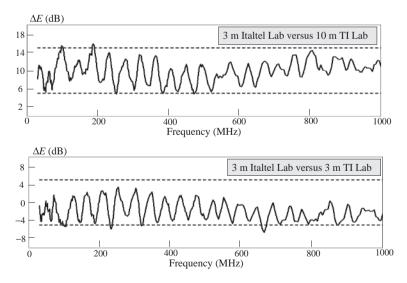

| 11.3 | Prediction Model Validation by Radiated Emission Measurements              | 431 |

|      | 11.3.1 Uncertainty of the EMC Lab for Radiated Field Measurements          |     |

|      | and Numerical Simulations                                                  | 431 |

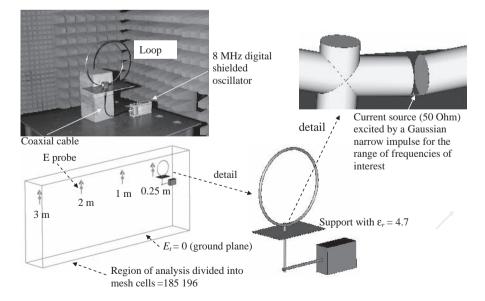

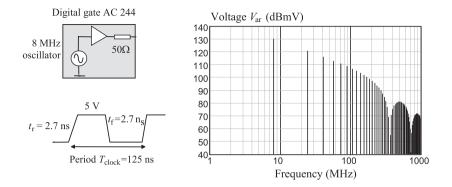

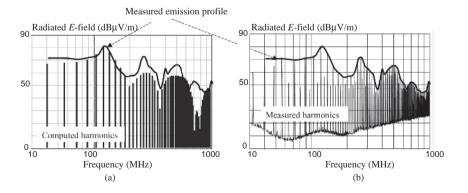

|      | 11.3.2 Modeling the Radiating Source                                       | 436 |

|      | 11.3.3 Conclusion Concerning Validation of the Numerical Prediction        |     |

|      | Model for Radiated Emission by Comparison with Measurements                | 439 |

|      | References                                                                 | 440 |

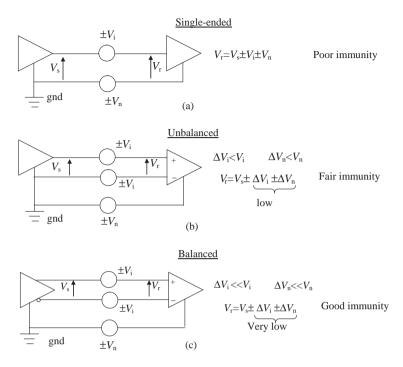

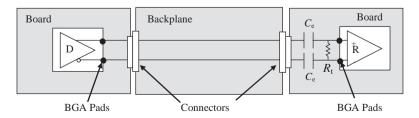

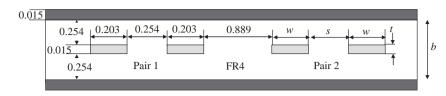

| 12   | Differential Signaling and Discontinuity Modeling in PCBs                  | 441 |

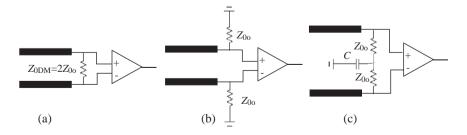

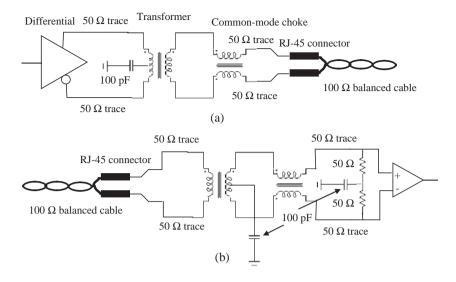

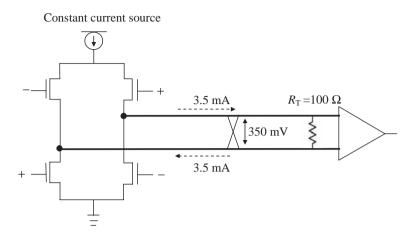

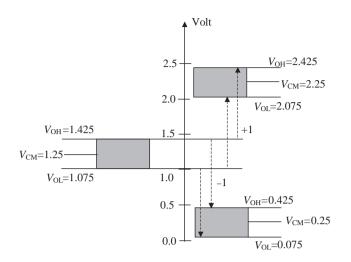

| 12.1 | Differential Signal Transmission                                           | 442 |

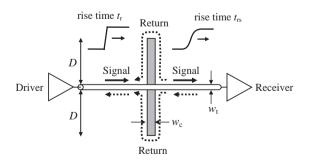

|      | 12.1.1 Single-Ended Versus Differential Signal Transmission                | 442 |

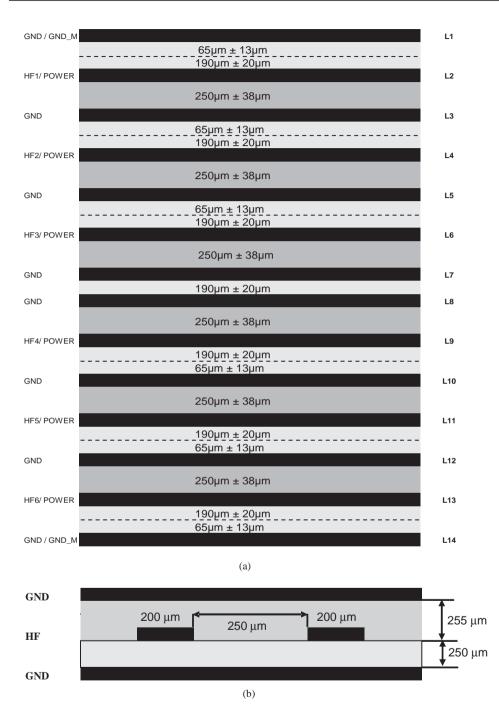

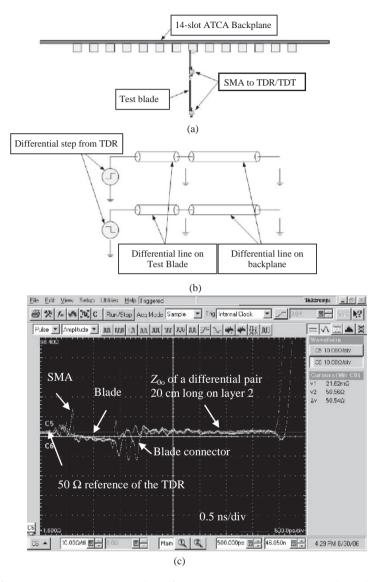

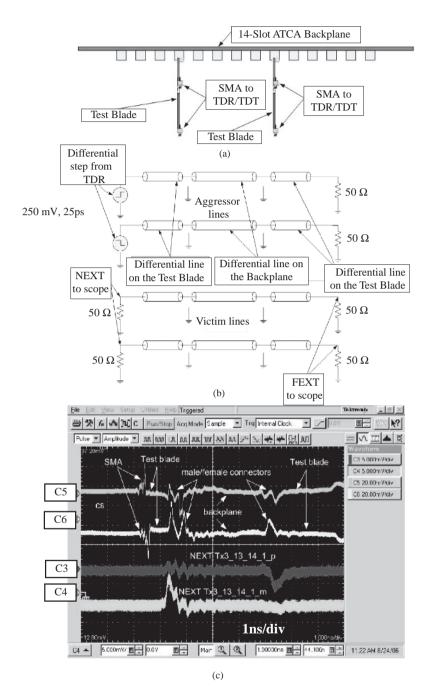

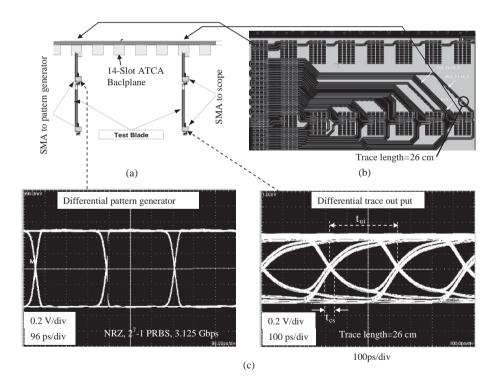

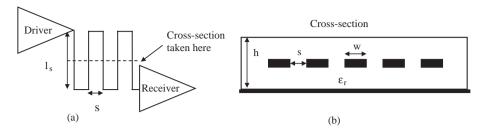

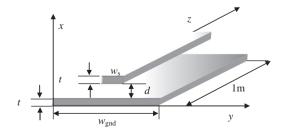

|      | 12.1.2 Differential Interconnect with Traces in PCBs and the ATCA Standard | 445 |

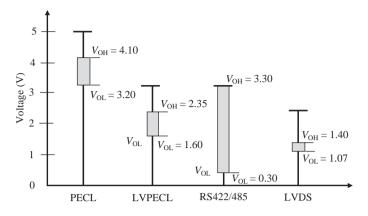

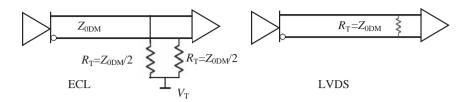

|      | 12.1.3 Differential Devices: Signal Level Comparison                       | 447 |

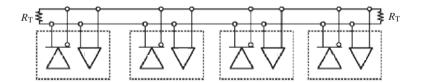

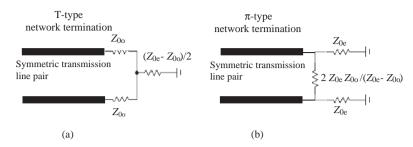

|      | 12.1.4 Differential Signal Distribution and Terminations                   | 447 |

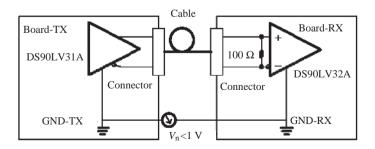

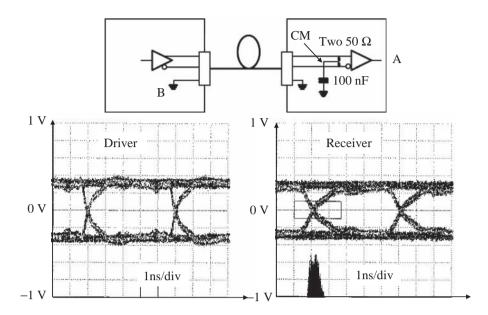

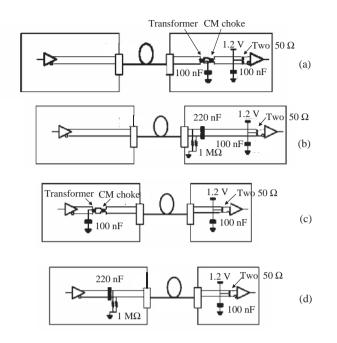

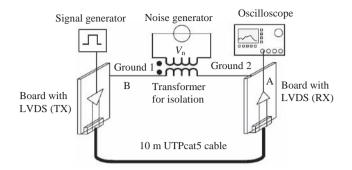

| 10.0 | 12.1.5 LVDS Devices                                                        | 451 |

| 12.2 | Modeling Packages and Interconnect Discontinuities in PCBs                 | 466 |

|      | 12.2.1 Multilayer Boards                                                   | 466 |

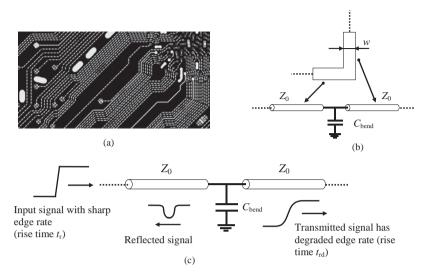

|      | 12.2.2 Bends                                                               | 466 |

|      | 12.2.3 Serpentines                                                         | 468 |

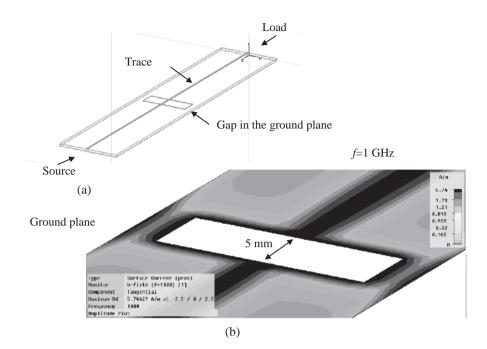

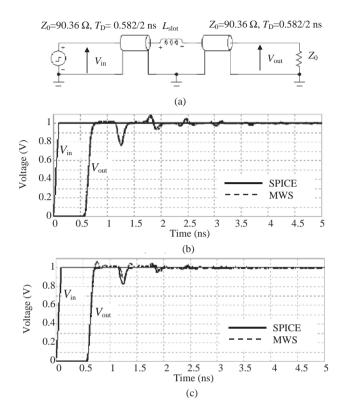

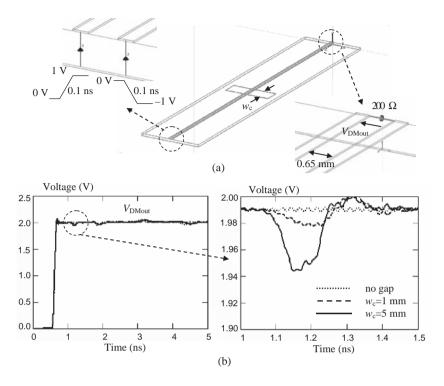

|      | 12.2.4 Ground Slot                                                         | 468 |

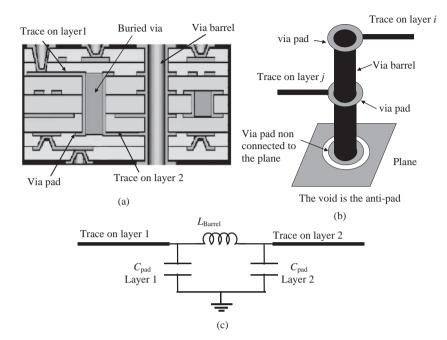

|      | 12.2.5 Vias                                                                | 471 |

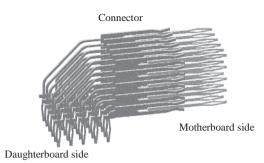

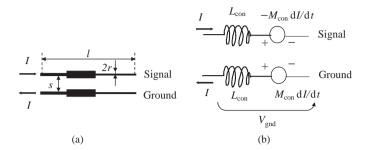

|      | 12.2.6 Connectors                                                          | 473 |

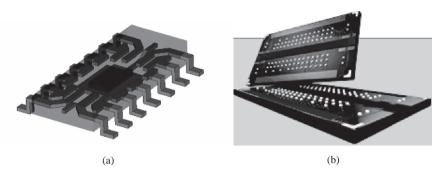

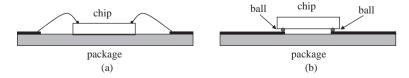

|      | 12.2.7 IC Package                                                          | 475 |

|      | References                                                                 | 477 |

|      | endix A Formulae for Partial Inductance Calculation                        | 481 |

| A.1  | Round Wires                                                                | 481 |

\_\_\_\_\_

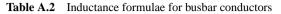

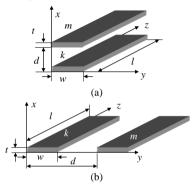

| A.2 Busbars                                                           | 483        |  |  |  |

|-----------------------------------------------------------------------|------------|--|--|--|

| A.3 Examples of Application of the Inductance Formulae                |            |  |  |  |

| References                                                            | 485<br>485 |  |  |  |

| Appendix B Characteristic Impedance, Delay Time, and Attenuation      |            |  |  |  |

| of Microstrips and Striplines                                         | 487        |  |  |  |

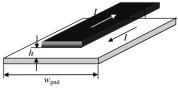

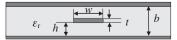

| B.1 Microstrip                                                        | 487        |  |  |  |

| B.2 Stripline                                                         | 489        |  |  |  |

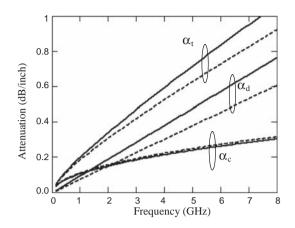

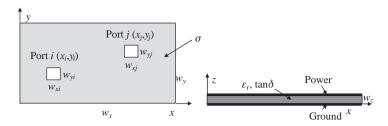

| B.3 Trace Attenuation and the Proximity-Effect Parameter              | 490        |  |  |  |

| References                                                            | 492        |  |  |  |

| Appendix C Computation of Resonances in the Power Distribution No     | etwork     |  |  |  |

| of a PCB                                                              | 493        |  |  |  |

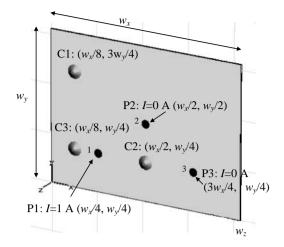

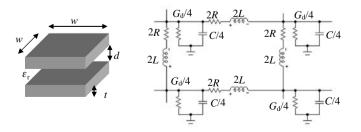

| C.1 Cavity Model                                                      | 493        |  |  |  |

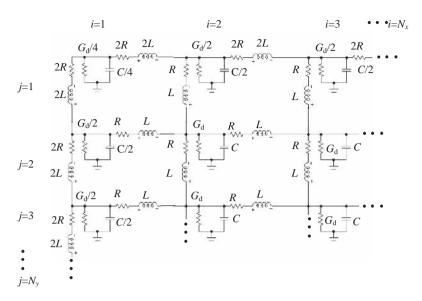

| C.2 Spice Model                                                       | 497        |  |  |  |

| C.3 Numerical Model                                                   | 498        |  |  |  |

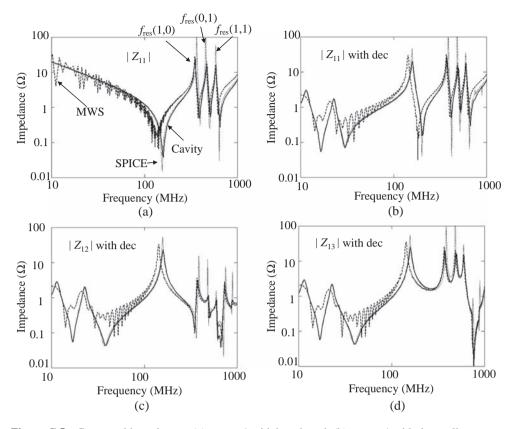

| C.4 Results of the Simulations                                        | 498        |  |  |  |

| References                                                            | 500        |  |  |  |

| Appendix D Formulae for Simple Radiating Structures                   | 501        |  |  |  |

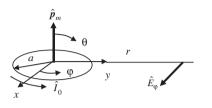

| D.1 Wire Structures                                                   | 501        |  |  |  |

| D.2 Wires and Ground Planes                                           | 503        |  |  |  |

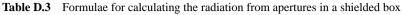

| D.3 Emission from Apertures                                           | 505        |  |  |  |

| References                                                            | 505        |  |  |  |

| Appendix E The Nodal Method to Calculate the Partial Inductance of    |            |  |  |  |

| Ground Planes                                                         | 507        |  |  |  |

| E.1 Nodal Method Equations                                            | 507        |  |  |  |

| E.2 Nodal Method Applied to Compute the Partial Inductance Associated |            |  |  |  |

| a Finite Ground Plane                                                 | 508        |  |  |  |

| References                                                            | 511        |  |  |  |

| Appendix F Files on the Web                                           | 513        |  |  |  |

| F.1 Program Files of Chapter 1                                        | 513        |  |  |  |

| F.2 Program Files of Chapter 2                                        | 513        |  |  |  |

| F.3 Program Files of Chapter 5                                        | 513        |  |  |  |

| F.4 Program Files of Chapter 6                                        | 514        |  |  |  |

| F.5 Program Files of Chapter 7                                        | 514        |  |  |  |

| F.6 Program Files of Chapter 8                                        | 515        |  |  |  |

| F.7 Program Files of Chapter 9                                        | 516        |  |  |  |

| F.8 Program Files of Chapter 10                                       | 517        |  |  |  |

| Index                                                                 | 519        |  |  |  |

xi

## List of Examples

| 3.1: | Calculation of Inductances Associated with the Decoupling                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Capacitor and IC Device in a PCB                                                                                                                                                                                                                                                                                 | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5.1: | Measurements and Graphical Method Applied to an                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | Interconnection with TTL Devices                                                                                                                                                                                                                                                                                 | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.1: | Point-to-Point Structure                                                                                                                                                                                                                                                                                         | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.2: | Chain Structure                                                                                                                                                                                                                                                                                                  | 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.3: | Two Coupled Lines with Linear Loads                                                                                                                                                                                                                                                                              | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.4: | Two Coupled Traces with TTL Devices in a Point-to-Point Test                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | Board Structure                                                                                                                                                                                                                                                                                                  | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.5: | Two Coupled Lines in a Bus Test Board Structure                                                                                                                                                                                                                                                                  | 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.6: | Five Coupled Lines with Non-linear Loads                                                                                                                                                                                                                                                                         | 152                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7.1: | Trace with 50 $\Omega$ Characteristic Impedance                                                                                                                                                                                                                                                                  | 178                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7.2: | Signal Integrity in a Lossy Coaxial Cable                                                                                                                                                                                                                                                                        | 192                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

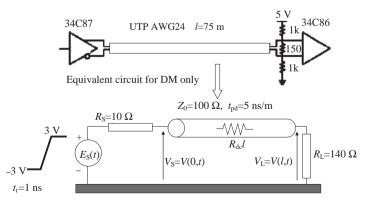

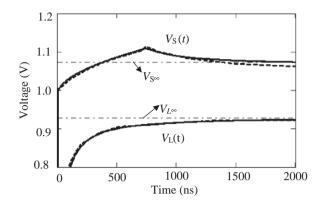

| 7.3: | Signal Integrity in a Lossy UTP Cable                                                                                                                                                                                                                                                                            | 197                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7.4: |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      |                                                                                                                                                                                                                                                                                                                  | 201                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

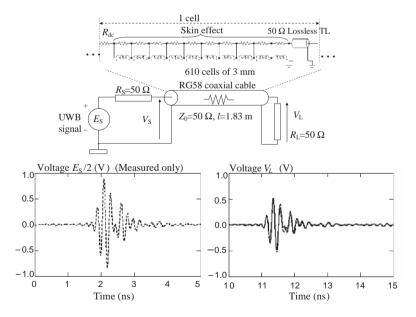

| 7.5: | Coaxial Cable Driven by an Ultrawide-band Signal Simulated by                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | the TL Model Based on the Time-domain S-parameters                                                                                                                                                                                                                                                               | 213                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

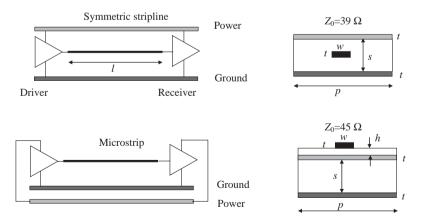

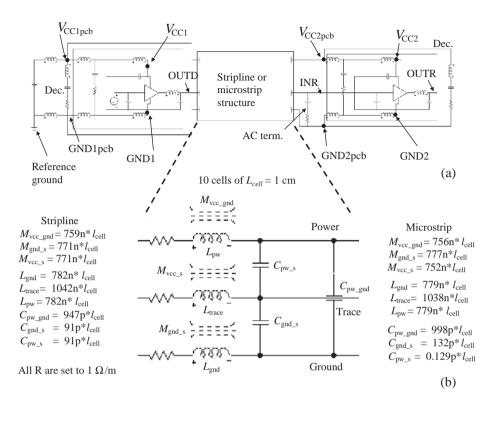

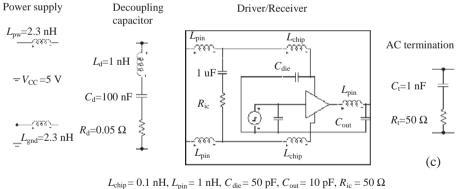

| 8.1: | Switching Noise Simulations of Two Stripline and Microstrip                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | Structures                                                                                                                                                                                                                                                                                                       | 227                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

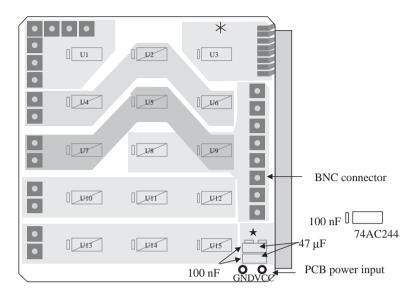

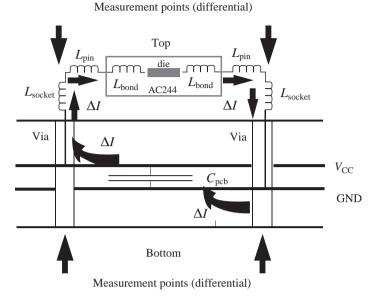

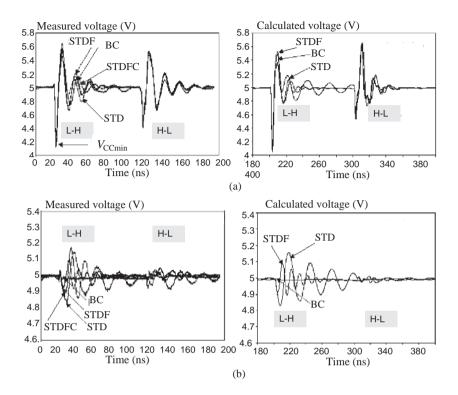

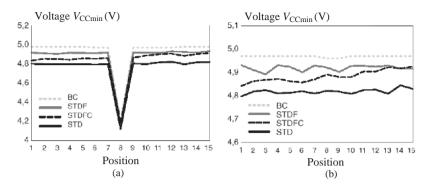

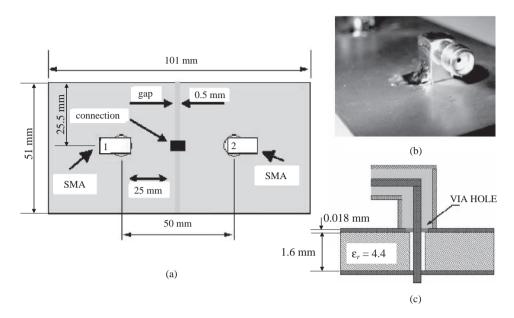

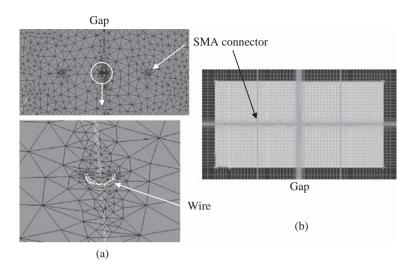

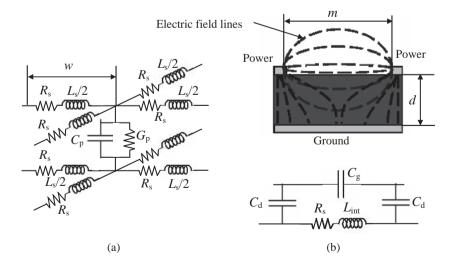

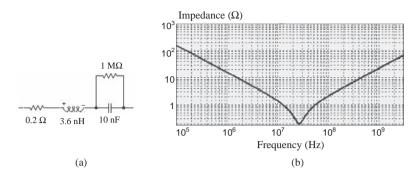

| 8.2: | Test Board for Prediction of Power Bus Impedance by Several                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | Methods                                                                                                                                                                                                                                                                                                          | 239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 8.3: |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | Capacitance (SBC) Test Boards                                                                                                                                                                                                                                                                                    | 247                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | •                                                                                                                                                                                                                                                                                                                | 272                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9.2: |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |